SN65LVDS96

lvds serdes 接受者

slls296f – 将 1998 – 修订 二月 2000

5

邮递 办公室 盒 655303

•

达拉斯市, 德州 75265

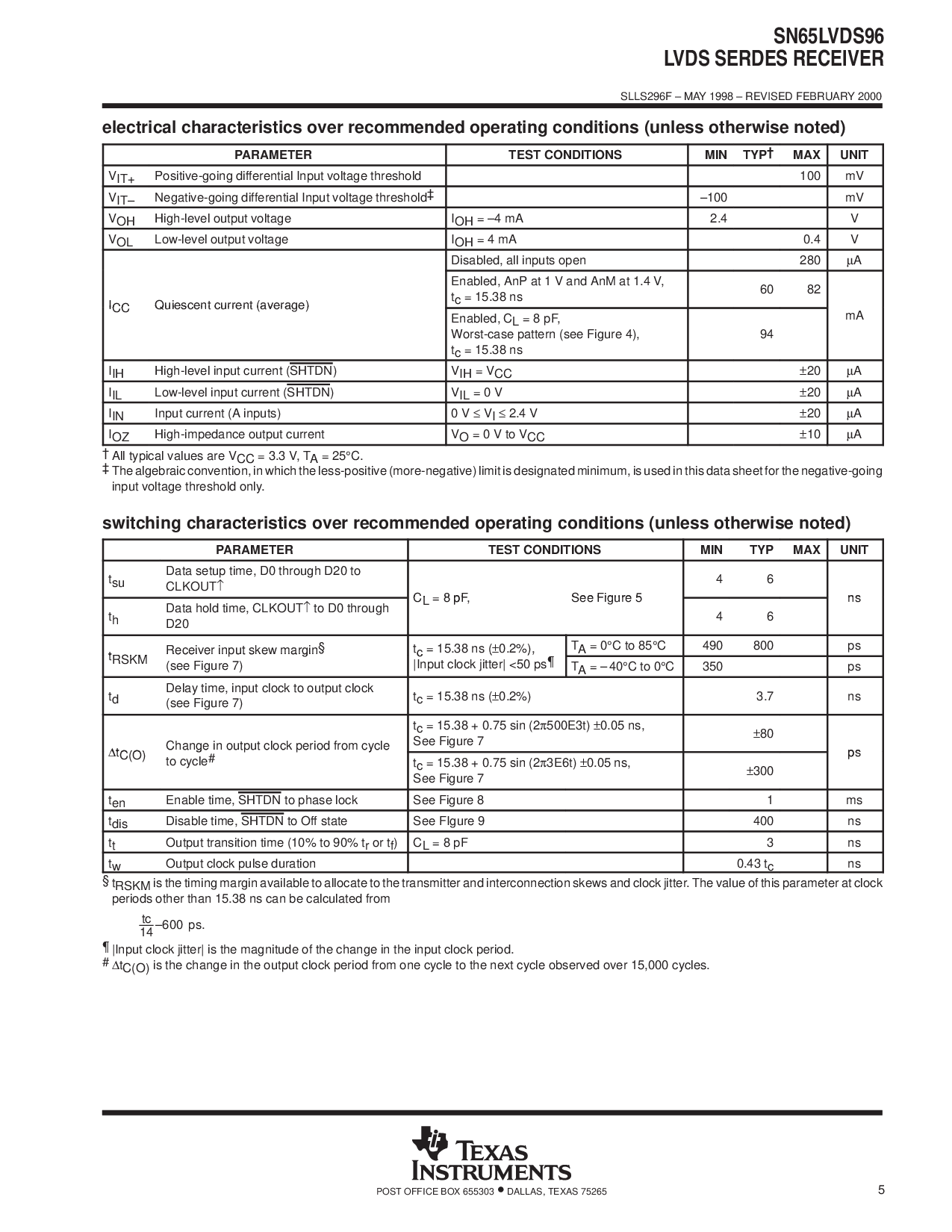

电的 特性 在 推荐 运行 情况 (除非 否则 指出)

参数 测试 情况 最小值 典型值

†

最大值 单位

V

IT+

积极的-going 差别的 输入 电压 门槛 100 mV

V

IT–

负的-going 差别的 输入 电压 门槛

‡

–100 mV

V

OH

高-水平的 输出 电压 I

OH

= –4 毫安 2.4 V

V

OL

低-水平的 输出 电压 I

OH

= 4 毫安 0.4 V

无能, 所有 输入 打开 280

µ

一个

I

CC

安静的 电流 (平均)

使能, anp 在 1 v 和 anm 在 1.4 v,

t

c

= 15.38 ns

60 82

I

CC

安静的 电流 (平均)

使能, c

L

= 8 pf,

worst-情况 模式 (看 图示 4),

t

c

= 15.38 ns

94

毫安

I

IH

高-水平的 输入 电流 (shtdn) V

IH

= v

CC

±

20

µ

一个

I

IL

低-水平的 输入 电流 (shtdn) V

IL

= 0 v

±

20

µ

一个

I

在

输入 电流 (一个 输入) 0 v

≤

V

I

≤

2.4 v

±

20

µ

一个

I

OZ

高-阻抗 输出 电流 V

O

= 0 v 至 v

CC

±

10

µ

一个

†

所有 典型 值 是 v

CC

= 3.3 v, t

一个

= 25

°

c.

‡

这 algebraic convention, 在 这个 这 较少-积极的 (更多-负的) 限制 是 designated 最小, 是 使用 在 这个 数据 薄板 为 这 negative-going

输入 电压 门槛 仅有的.

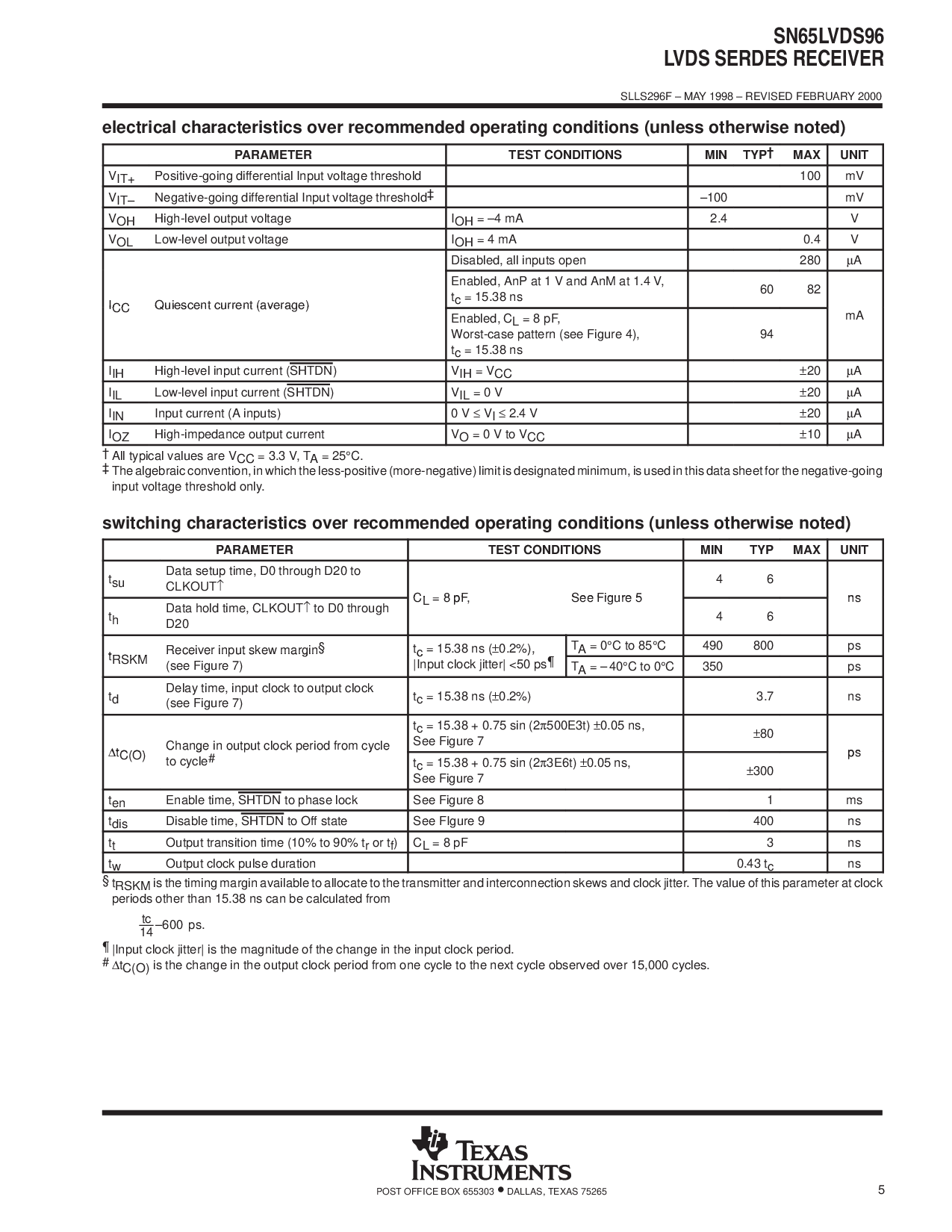

切换 特性 在 推荐 运行 情况 (除非 否则 指出)

参数 测试 情况 最小值 典型值 最大值 单位

t

su

数据 建制 时间, d0 通过 d20 至

CLKOUT

↑

C

L

=8pF 看 图示 5

4 6

ns

t

h

数据 支撑 时间, clkout

↑

至 d0 通过

D20

C

L

=8 pf, 看 图示 5

4 6

ns

t

RSKM

接受者 输入 skew 三月gin

§

t

c

= 15.38 ns (

±

0.2%),

T

一个

= 0

°

c 至 85

°

C 490 800 ps

t

RSKM

接受者 在 ut skew 余裕

(看 图示 7)

c

( ),

|input 时钟 jitter| <50 ps

¶

T

一个

= – 40

°

c 至 0

°

C 350 ps

t

d

延迟 时间, 输入 时钟 至 输出 时钟

(看 图示 7)

t

c

= 15.38 ns (

±

0.2%) 3.7 ns

∆

t

c(o)

Change 在 输出 时钟 时期 从 cycle

t

c

= 15.38 + 0.75 sin (2

π

500e3t)

±

0.05 ns,

看 图示 7

±

80

ps

∆

t

c(o)

改变 在 输出 ut 时钟 eriod 从 循环

至 循环

#

t

c

= 15.38 + 0.75 sin (2

π

3e6t)

±

0.05 ns,

看 图示 7

±

300

ps

t

en

使能 时间, shtdn至 阶段 锁 看 图示 8 1 ms

t

dis

使不能运转 时间, shtdn至 止 状态 看 图示 9 400 ns

t

t

输出 转变 时间 (10% 至 90% t

r

或者 t

f

) C

L

= 8 pf 3 ns

t

w

输出 时钟 脉冲波 持续时间 0.43 t

c

ns

§

t

RSKM

是 这 定时 余裕 有 至 allocate 至 这 传输者 和 interconnection skews 和 时钟 jitter. 这 值 的 这个 parameter 在 时钟

时期 其它 比 15.38 ns 能 是 计算 从

tc

14

–600 ps.

¶

|input 时钟 jitter| 是 这 巨大 的 这 改变 在 这 输入 时钟 时期.

#

∆

t

c(o)

是 这 改变 在 这 输出 时钟 时期 从 一个 循环 至 这 next 循环 observed 在 15,000 循环.