通过 科技, 公司

VT82C42

-6-

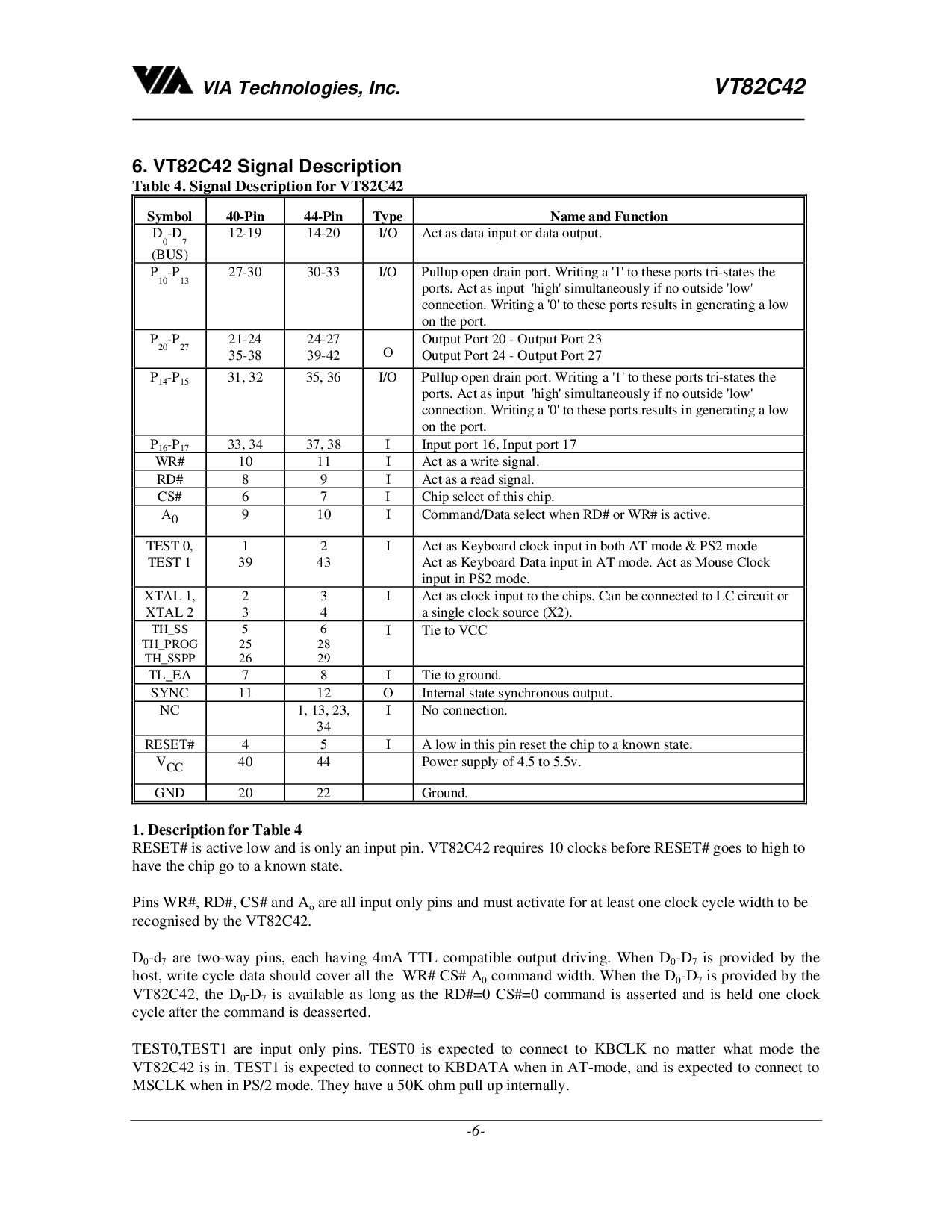

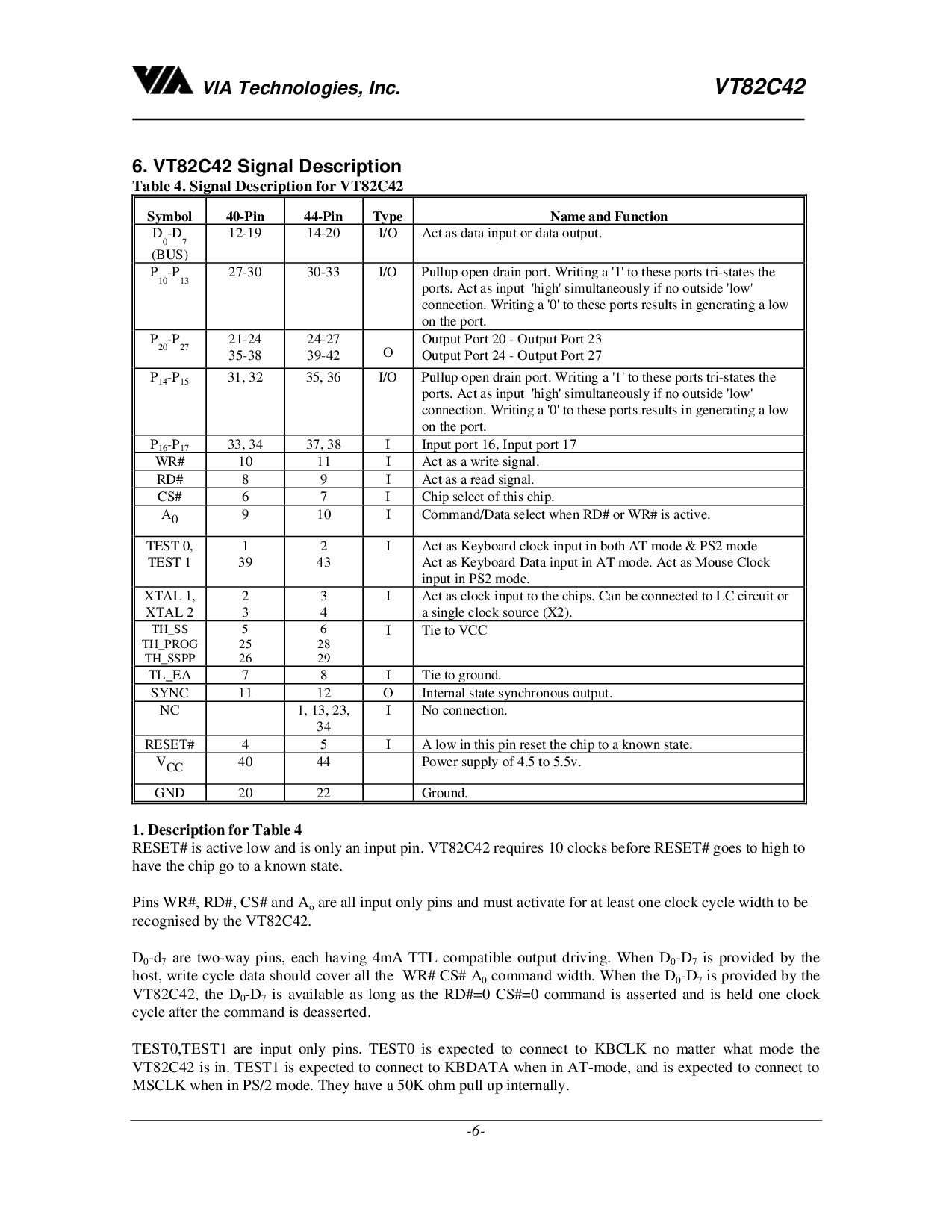

6. vt82c42 信号 描述

表格 4. 信号 描述 为 vt82c42

标识 40-管脚 44-管脚 类型 名字 和 函数

D

0

-d

7

(总线)

12-19 14-20 i/o act 作 数据 输入 或者 数据 输出.

P

10

-p

13

27-30 30-33 i/o pullup 打开 流 端口. writing 一个 '1' 至 这些 端口 触发-states 这

端口. act 作 输入 '高' 同时发生地 如果 非 外部 '低'

连接. writing 一个 '0' 至 这些 端口 结果 在 generating 一个 低

在 这 端口.

P

20

-p

27

21-24

35-38

24-27

39-42

O

输出 端口 20 - 输出 端口 23

输出 端口 24 - 输出 端口 27

P

14

-p

15

31, 32 35, 36 i/o pullup 打开 流 端口. writing 一个 '1' 至 这些 端口 触发-states 这

端口. act 作 输入 '高' 同时发生地 如果 非 外部 '低'

连接. writing 一个 '0' 至 这些 端口 结果 在 generating 一个 低

在 这 端口.

P

16

-p

17

33, 34 37, 38 I 输入 端口 16, 输入 端口 17

WR# 10 11 I act 作 一个 写 信号.

RD# 8 9 I act 作 一个 读 信号.

CS# 6 7 I 碎片 选择 的 这个 碎片.

一个

0

9 10 I command/数据 选择 当 rd# 或者 wr# 是 起作用的.

测试 0,

测试 1

1

39

2

43

I act 作 键盘 时钟 输入 在 两个都 在 模式 &放大; ps2 模式

act 作 键盘 数据 输入 在 在 模式. act 作 mouse 时钟

输入 在 ps2 模式.

xtal 1,

xtal 2

2

3

3

4

I act 作 时钟 输入 至 这 碎片. 能 是 连接 至 lc 电路 或者

一个 单独的 时钟 源 (x2).

th_ss

th_prog

th_sspp

5

25

26

6

28

29

I 系 至 vcc

tl_ea 7 8 I 系 至 地面.

同步 11 12 O 内部的 状态 同步的 输出.

NC 1, 13, 23,

34

I 非 连接.

RESET# 4 5 I 一个 低 在 这个 管脚 重置 这 碎片 至 一个 知道 状态.

V

CC

40 44 电源 供应 的 4.5 至 5.5v.

地 20 22 地面.

1. 描述 为 表格 4

reset# 是 起作用的 低 和 是 仅有的 一个 输入 管脚. vt82c42 需要 10 clocks 在之前 reset# 变得 至 高 至

有 这 碎片 go 至 一个 知道 状态.

管脚 wr#, rd#, cs# 和 一个

o

是 所有 输入 仅有的 管脚 和 必须 活动 为 在 least 一个 时钟 循环 宽度 至 是

recognised 用 这 vt82c42.

D

0

-d

7

是 二-方法 管脚, 各自 having 4ma ttl 兼容 输出 驱动. 当 d

0

-d

7

是 提供 用 这

host, 写 循环 数据 应当 覆盖 所有 这 wr# cs# 一个

0

command 宽度. 当 这 d

0

-d

7

是 提供 用 这

vt82c42, 这 d

0

-d

7

是 有 作 长 作 这 rd#=0 cs#=0 command 是 asserted 和 是 使保持 一个 时钟

循环 之后 这 command 是 deasserted.

test0,test1 是 输入 仅有的 管脚. test0 是 预期的 至 连接 至 kbclk 非 matter what 模式 这

vt82c42 是 在. test1 是 预期的 至 连接 至 kbdata 当 在 在-模式, 和 是 预期的 至 连接 至

msclk 当 在 ps/2 模式. 它们 有 一个 50k ohm 拉 向上 内部.