W180

7

应用 信息

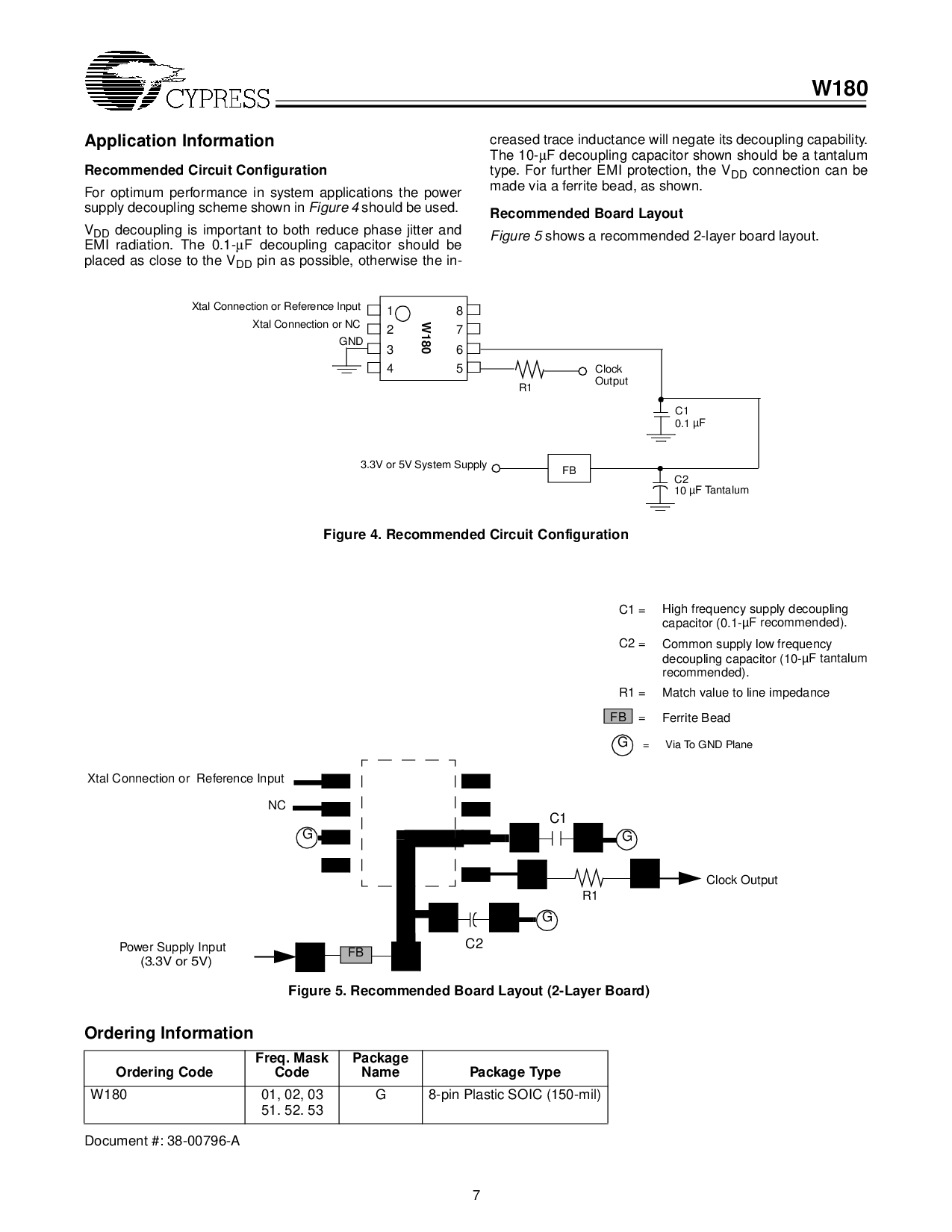

推荐 电路 配置

为 最佳的 效能 在 系统 产品 这 电源

供应 解耦 scheme 显示 在

图示 4

应当 是 使用.

V

DD

解耦 是 重要的 至 两个都 减少 阶段 jitter 和

emi 辐射. 这 0.1-

µ

f 解耦 电容 应当 是

放置 作 关闭 至 这 v

DD

管脚 作 可能, 否则 这 在-

creased 查出 电感 将 negate 它的 解耦 能力.

这 10-

µ

f 解耦 电容 显示 应当 是 一个 tantalum

类型. 为 更远 emi 保护, 这 v

DD

连接 能 是

制造 通过 一个 ferrite bead, 作 显示.

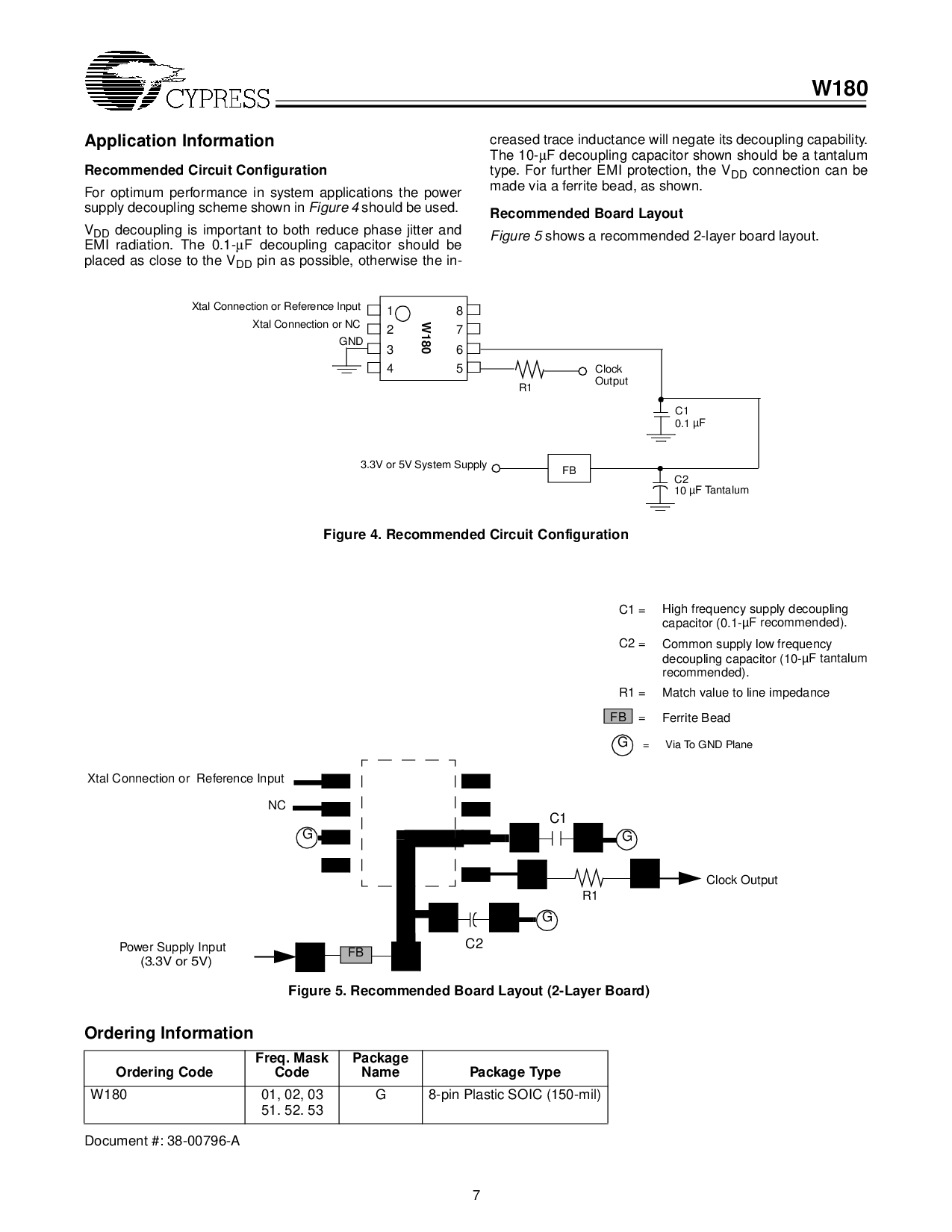

推荐 板 布局

图示 5

显示 一个 推荐 2-layer 板 布局.

文档 #: 38-00796-一个

图示 4. 推荐 电路 配置

地

W180

8

7

6

5

1

2

3

4

C1

FB

C2

3.3v 或者 5v 系统 供应

10

µf tantalum

0.1

µF

时钟

xtal 连接 或者 涉及 输入

xtal 连接 或者 nc

输出

R1

订货 信息

订货 代号

freq. 掩饰

代号

包装

名字

Package 类型

W180 01, 02, 03

51. 52. 53

G 8-管脚 塑料 soic (150-mil)

时钟 输出

高 频率 供应 解耦

电容 (0.1-

µf 推荐).

一般 供应 低 频率

解耦 电容 (10-

µf tantalum

推荐).

FB

Ferr它e bead

c1 =

c2 =

相一致 值 至 线条 阻抗

r1 =

=

R1

C1

C2

G

G

FB

= 通过 至 地 平面

G

xtal 连接 或者 涉及 输入

NC

G

电源 供应 输入

(3.3v 或者 5v)

图示 5. 推荐 板 布局 (2-layer 板)