max114/max118

在 读 模式,

WR

/rdy 是 配置 作 一个 状态 输出

(rdy), 所以 它 能 驱动 这 准备好 或者 wait 输入 的 一个 µp.

rdy 是 一个 打开-集电级 输出 (非 内部的 拉-向上)

那 变得 低 之后 这 下落 边缘 的

CS

和 变得 高

在 这 终止 的 这 转换. 如果 不 使用, 这

WR

/rdy

管脚 能 是 left unconnected. 这

INT

输出 变得 低

在 这 终止 的 这 转换 和 returns 高 在 这 ris-

ing 边缘 的

CS

或者

RD

.

写-读 模式 (模式 = 1)

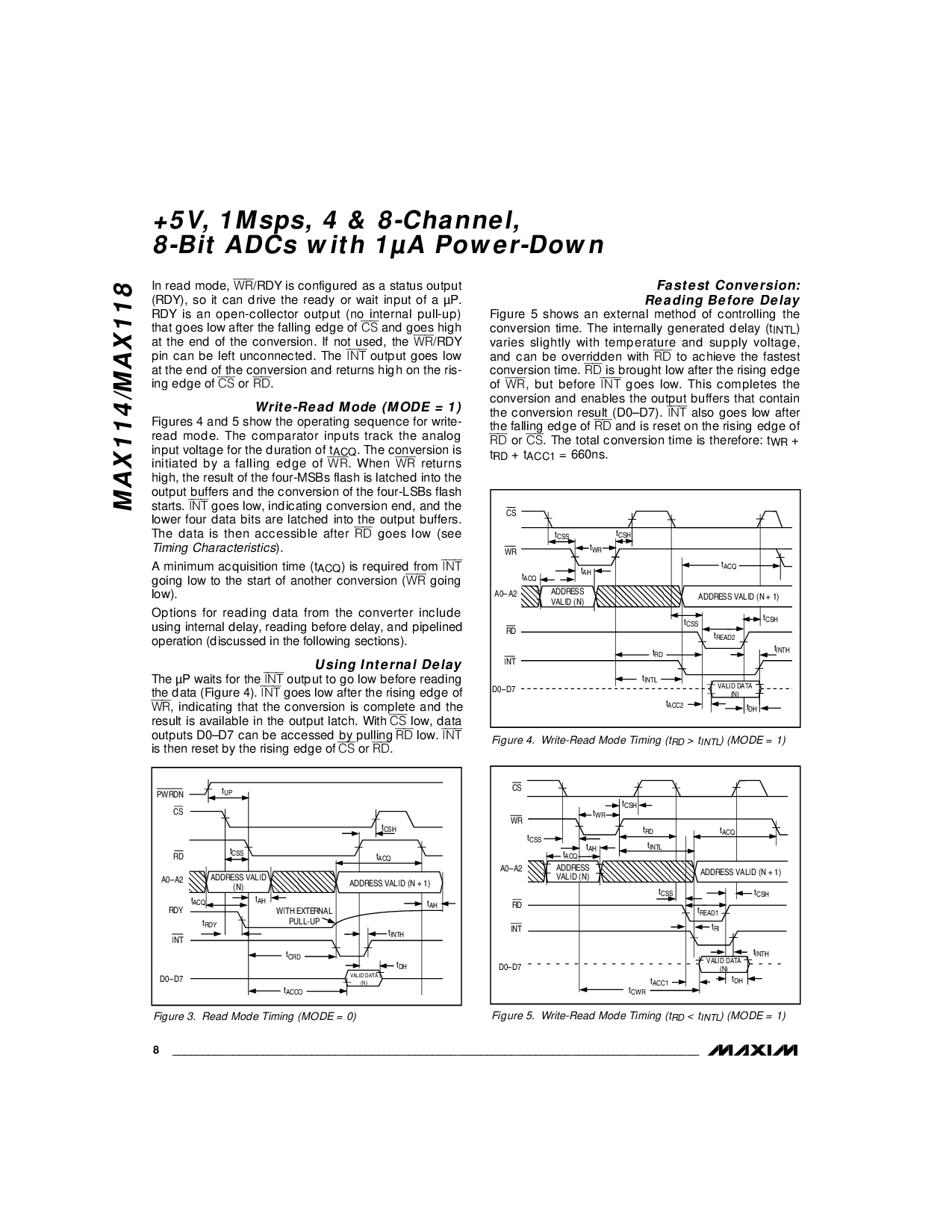

计算数量 4 和 5 显示 这 运行 sequence 为 写-

读 模式. 这 比较器 输入 追踪 这 相似物

输入 电压 为 这 持续时间 的 t

ACQ

. 这 转换 是

initiated 用 一个 下落 边缘 的

WR

. 当

WR

returns

高, 这 结果 的 这 四-msbs flash 是 latched 在 这

输出 缓存区 和 这 转换 的 这 四-lsbs flash

开始.

INT

变得 低, 表明 转换 终止, 和 这

更小的 四 数据 位 是 latched 在 这 输出 缓存区.

这 数据 是 然后 accessible 之后

RD

变得 低 (看

定时 特性

).

一个 最小 acquisition 时间 (t

ACQ

) 是 必需的 从

INT

going 低 至 这 开始 的 另一 转换 (

WR

going

低).

选项 为 读 数据 从 这 转换器 包含

使用 内部的 延迟, 读 在之前 延迟, 和 pipelined

运作 (discussed 在 这 下列的 sections).

使用 内部的 延迟

这 µp waits 为 这

INT

输出 至 go 低 在之前 读

这 数据 (图示 4).

INT

变得 低 之后 这 rising 边缘 的

WR

, 表明 那 这 转换 是 完全 和 这

结果 是 有 在 这 输出 获得. 和

CS

低, 数据

输出 d0–d7 能 是 accessed 用 拉

RD

低.

INT

是 然后 重置 用 这 rising 边缘 的

CS

或者

RD

.

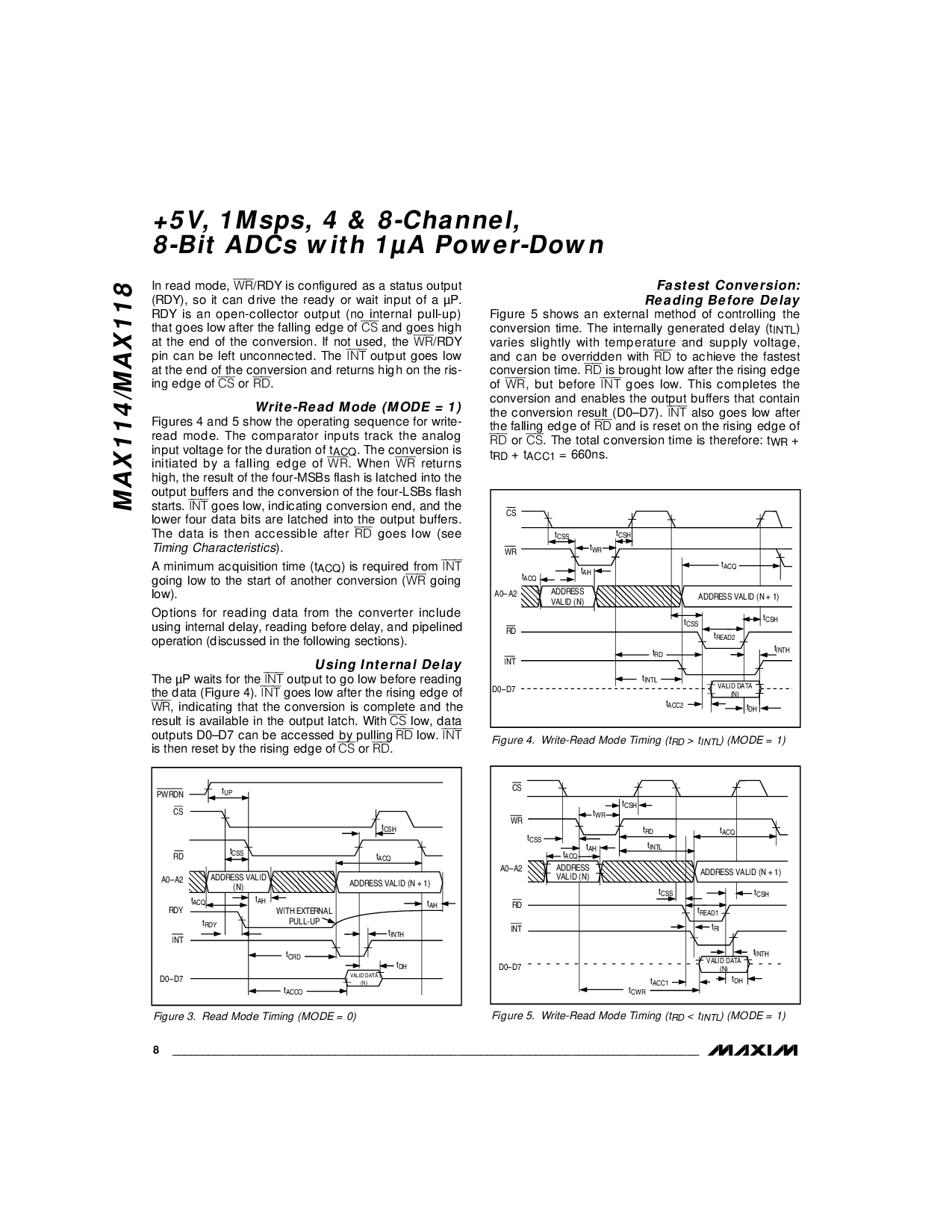

fastest 转换:

读 在之前 延迟

图示 5 显示 一个 外部 方法 的 controlling 这

转换 时间. 这 内部 发生 延迟 (t

INTL

)

varies slightly 和 温度 和 供应 电压,

和 能 是 overridden 和

RD

至 达到 这 fastest

转换 时间.

RD

是 brought 低 之后 这 rising 边缘

的

WR

, 但是 在之前

INT

变得 低. 这个 完成 这

转换 和 使能 这 输出 缓存区 那 包含

这 转换 结果 (d0–d7).

INT

也 变得 低 之后

这 下落 边缘 的

RD

和 是 重置 在 这 rising 边缘 的

RD

或者

CS

. 这 总的 转换 时间 是 因此: t

WR

+

t

RD

+ t

ACC1

= 660ns.

+5v, 1msps, 4 &放大; 8-频道,

8-位 adcs 和 1µa 电源-向下

8 _______________________________________________________________________________________

t

AH

t

ACQ

t

DH

t

READ2

t

RD

D0–D7

RD

WR

CS

INT

有效的 data

(n)

t

INTL

t

ACC2

t

WR

t

CSS

t

CSH

t

ACQ

t

CSS

t

CSH

A0–A2

t

INTH

ADDRESS

有效的 (n)

地址 有效的 (n + 1)

图示 4. 写-读 模式 定时 (t

RD

> t

INTL

) (模式 = 1)

t

CSS

t

ACQ

t

DH

t

READ1

t

RD

t

INTL

t

ACQ

t

AH

RD

WR

CS

INT

有效的 data

(n)

t

CSS

t

CSH

t

INTH

t

WR

t

CSH

t

ACC1

t

CWR

t

RI

A0–A2

D0–D7

ADDRESS

有效的 (n)

地址 有效的 (n + 1)

图示 5. 写-读 模式 定时 (t

RD

< t

INTL

) (模式 = 1)

t

CSS

t

RDY

t

ACQ

t

AH

和 external

拉-向上

t

CSH

t

ACQ

t

INTH

t

向上

t

DH

t

CRD

t

ACCO

D0–D7

RDY

RD

CS

PWRDN

INT

A0–A2

有效的 data

(n)

地址 有效的 (n + 1)

地址 valid

(n)

t

AH

图示 3. 读 模式 定时 (模式 = 0)