xc18v00 序列 在-系统 可编程序的 配置 proms

2

www.xilinx.com

ds026 (v4.0) 六月 11, 2003

1-800-255-7778

产品 规格

R

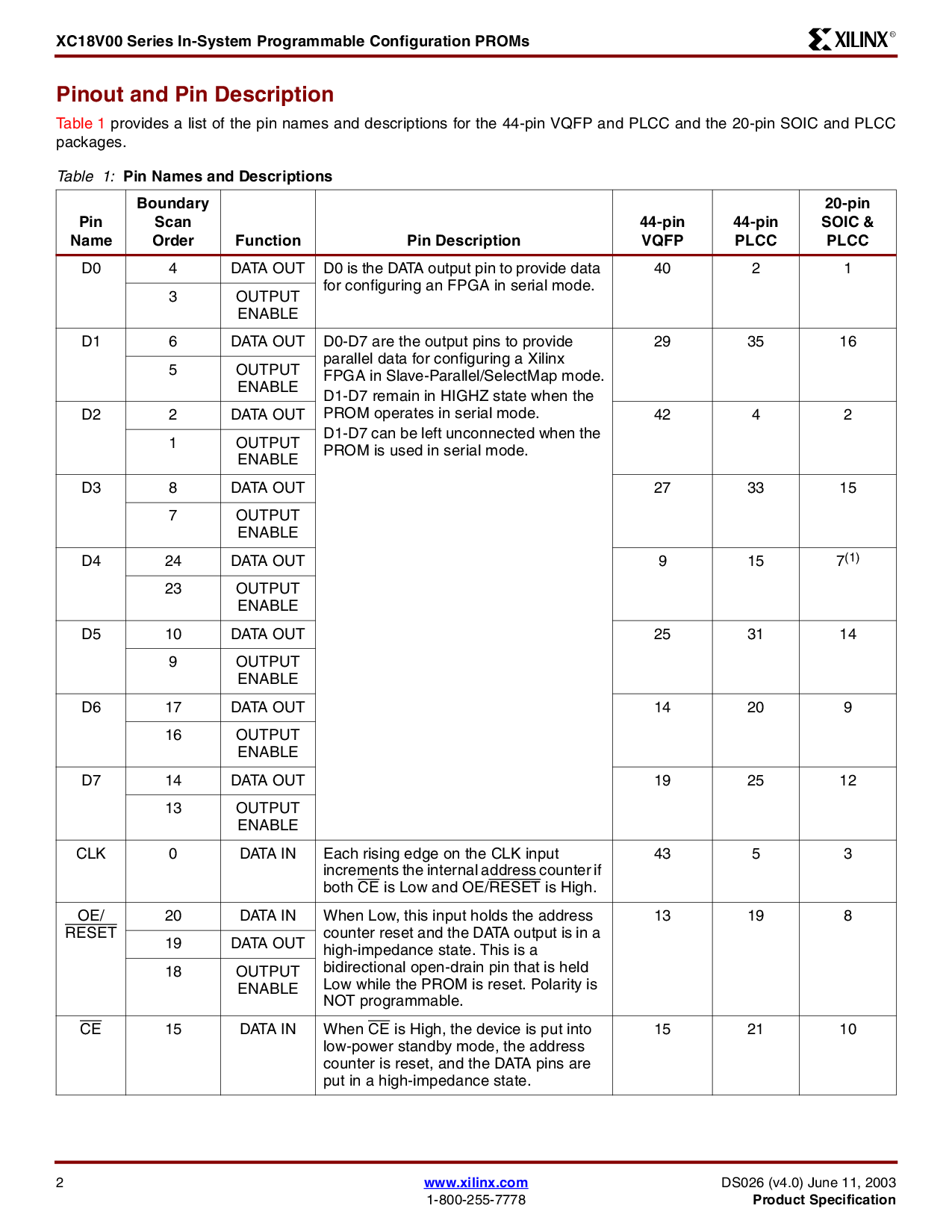

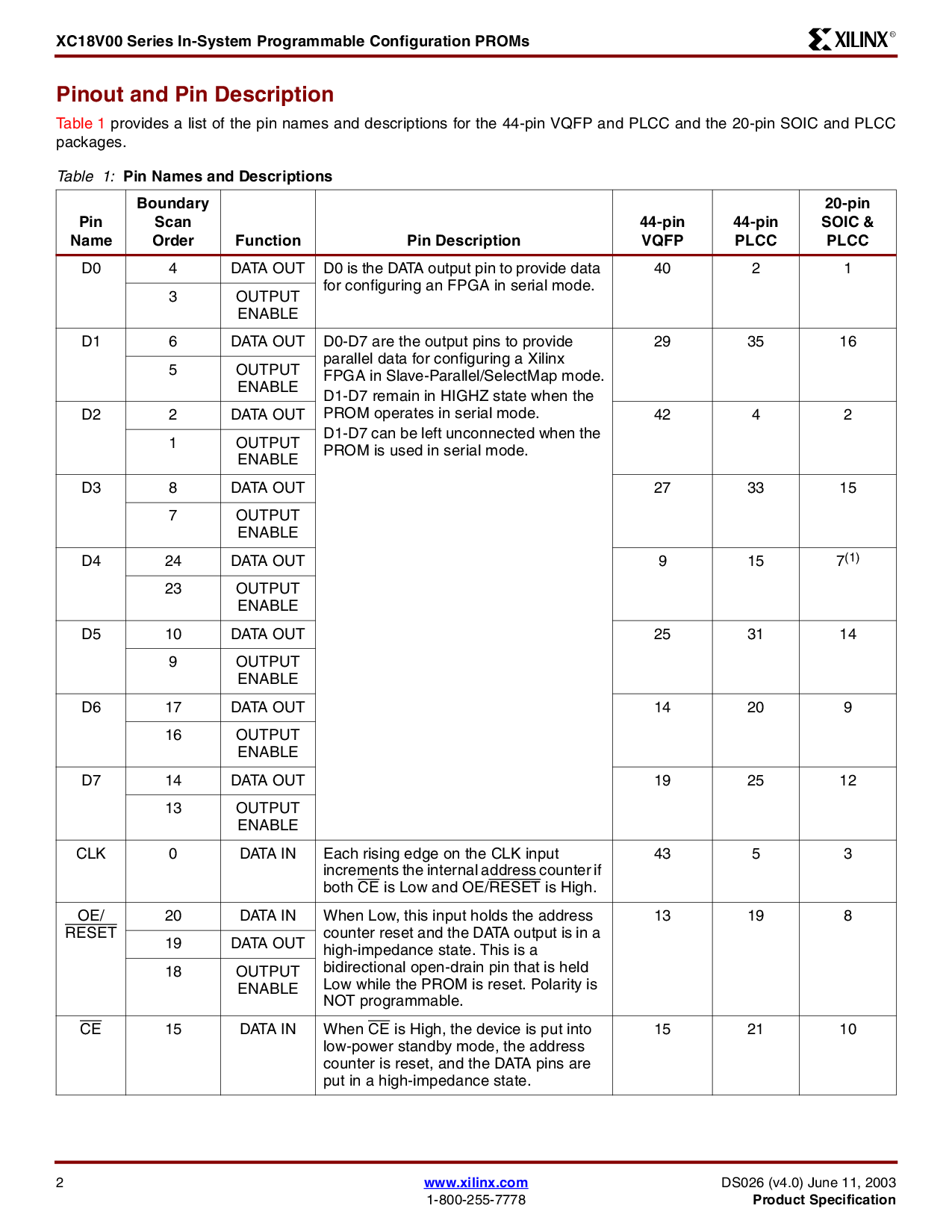

引脚 和 管脚 描述

表格 1提供 一个 列表 的 这 管脚 names 和 描述 为 这 44-管脚 vqfp 和 plcc 和 这 20-管脚 soic 和 plcc

包装.

表格 1:

管脚 names 和 描述

管脚

名字

Boundary

Scan

Order 函数 管脚 描述

44-管脚

VQFP

44-管脚

PLCC

20-管脚

soic &放大;

PLCC

D0 4 数据 输出 d0 是 这 数据 输出 管脚 至 提供 数据

为 configuring 一个 fpga 在 串行 模式.

40 2 1

3OUTPUT

使能

D1 6 数据 输出 d0-d7 是 这 输出 管脚 至 提供

并行的 数据 为 configuring 一个 xilinx

fpga 在 从动装置-并行的/selectmap 模式.

d1-d7 仍然是 在 highz 状态 当 这

prom 运作 在 串行 模式.

d1-d7 能 是 left unconnected 当 这

prom 是 使用 在 串行 模式.

29 35 16

5OUTPUT

使能

D2 2 数据 输出 42 4 2

1OUTPUT

使能

D3 8 数据 输出 27 33 15

7OUTPUT

使能

D4 24 数据 输出 9 15 7

(1)

23 输出

使能

D5 10 数据 输出 25 31 14

9OUTPUT

使能

D6 17 数据 输出 14 20 9

16 输出

使能

D7 14 数据 输出 19 25 12

13 输出

使能

CLK 0 数据 在 各自 rising 边缘 在 这 clk 输入

increments 这 内部的 地址 计数器 如果

两个都 ce

是 低 和 oe/重置是 高.

43 5 3

oe/

重置

20 数据 在 当 低, 这个 输入 holds 这 地址

计数器 重置 和 这 数据 输出 是 在 一个

高-阻抗 状态. 这个 是 一个

双向的 打开-流 管脚 那 是 使保持

低 当 这 prom 是 重置. 极性 是

不 可编程序的.

13 19 8

19 数据 输出

18 输出

使能

CE

15 数据 在 当 ce是 高, 这 设备 是 放 在

低-电源 备用物品 模式, 这 地址

计数器 是 重置, 和 这 数据 管脚 是

放 在 一个 高-阻抗 状态.

15 21 10