ds077-1 (v1.0) 十一月 15, 2001

www.xilinx.com

1

初步的 产品 规格

1-800-255-7778

© 2001 xilinx, 公司 所有 权利 保留. 所有 xilinx 商标, 注册 商标, patents, 和 免责声明 是 作 列表 一个t

http://www.xilinx.com/legal.htm

.

所有 其它 商标 和 注册 商标 是 这 所有物 的 它们的 各自的 所有权人. 所有 规格 是 主题 至 change 没有 注意.

介绍

这 spartan™-iie 1.8v 地方-可编程序的 门 排列

家族 给 用户 高 效能, abundant 逻辑

resources, 和 一个 rich 特性 设置, 所有 在 一个 exceptionally 低

价格. 这 five-成员 家族 提供 densities ranging 从

50,000 至 300,000 系统 门, 作 显示 在Ta bl e 1 . sys-

tem 效能 是 supported 在之外 200 mhz.

spartan-iie 设备 deliver 更多 门, i/os, 和 特性

每 dollar 比 其它 fpgas 用 结合 先进的 pro-

cess 技术 和 一个 streamlined architecture 为基础 在

这 proven virtex™-e platform. 特性 包含 块 内存

(至 64k 位), distributed 内存 (至 98,304 bits), 19 可选择的

i/o standards, 和 四 dlls (延迟-锁 循环). fast,

predictable interconnect 意思 那 successive 设计 iter-

ations continue 至 满足 定时 (所需的)东西.

这 spartan-iie 家族 是 一个 更好的 alternative 至

掩饰-编写程序 asics. 这 fpga 避免 这 最初的 费用,

lengthy 开发 循环, 和 固有的 风险 的

常规的 asics. 也, fpga programmability 准许

设计 升级 在 这 地方 和 非 硬件 替换

需要 (impossible 和 asics).

特性

• 第二 一代 asic 替换 技术

- densities 作 高 作 6,912 逻辑 cells 和 向上 至

300,000 系统 门

- streamlined 特性 为基础 在 virtex-e

architecture

- unlimited 在-系统 reprogrammability

- 非常 低 费用

• 系统 水平的 特性

- selectram+™ hierarchical 记忆:

·

16 位/lut distributed 内存

·

configurable 4k-位 真实 双-端口 块 内存

·

快 接口 至 外部 内存

- 全部地 3.3v pci 一致的 至 64 位 在 66 mhz 和

cardbus 一致的

- 低-电源 segmented routing architecture

- 全部 readback 能力 为 verification/observability

- 专心致志的 carry 逻辑 为 高-速 arithmetic

- 效率高的 乘法器 support

- cascade chain 为 宽-输入 功能

- abundant 寄存器/latches 和 使能, 设置, 重置

- 四 专心致志的 dlls 为 先进的 时钟 控制

- 四 primary

低-skew

global

时钟

分发

nets

- ieee 1149.1 兼容 boundary scan 逻辑

•

多功能的 i/o 和 包装

- 低 费用 包装 有 在 所有 densities

- 家族 footprint 兼容性 在 一般 包装

- 19 高-效能 接口 standards, 包含

LVDS一个nd LVPECL

- 向上 至 120 差别的 i/o pairs 那 能 是 输入,

输出, 或者 双向的

- 零 支撑 时间 使简化 系统 定时

•

全部地 supported 用 powerful xilinx ise 开发

系统

- 全部地 自动 mapping, placement, 和 routing

- 整体的 和 设计 entry 和 verification tools

0

spartan-iie 1.8v fpga 家族:

介绍 和 订货

信息

ds077-1 (v1.0) 十一月 15, 2001

00

初步的 产品 规格

R

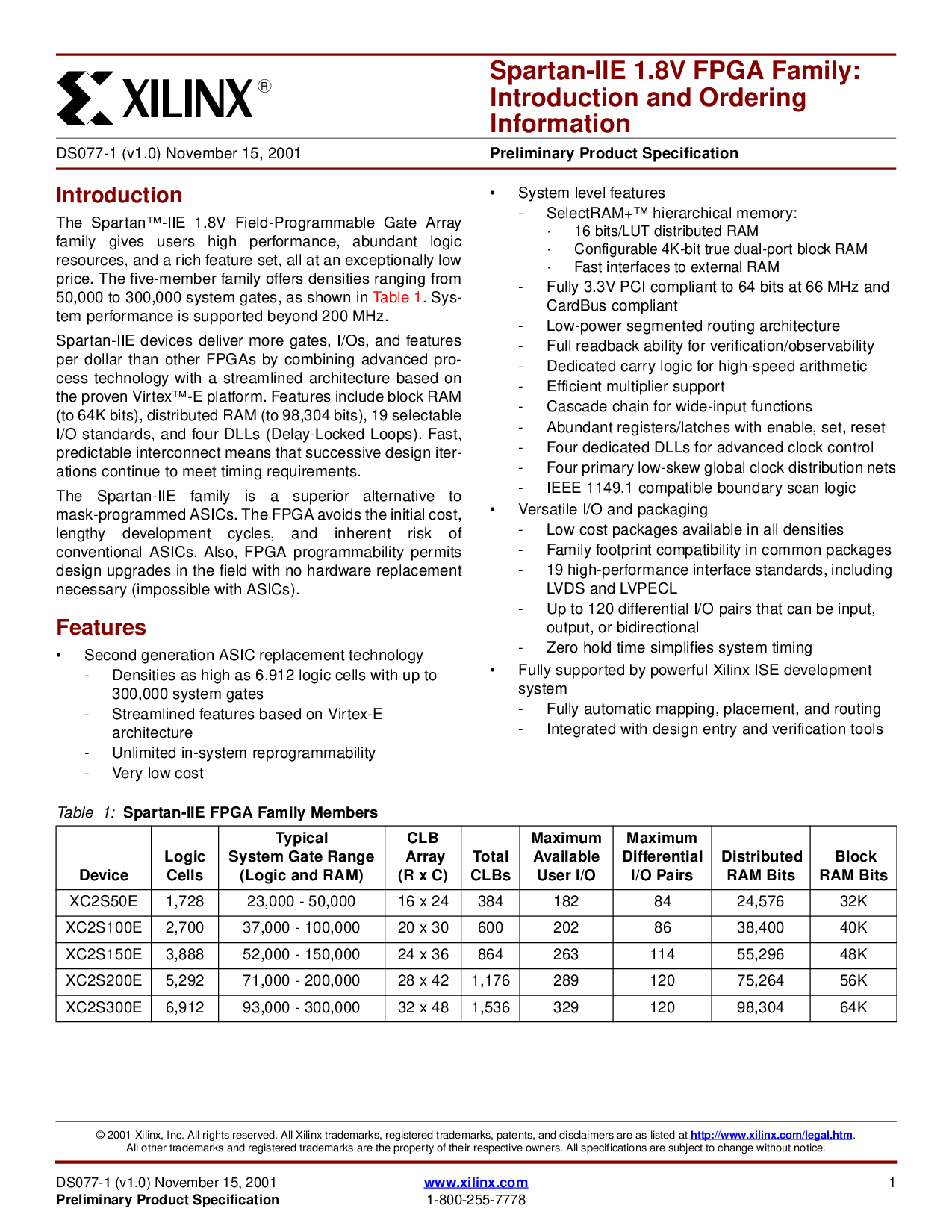

表格 1:

spartan-iie fpga 家族 members

设备

逻辑

Cells

Typic一个l

系统 门 范围

(逻辑 和 内存)

CLB

排列

(r x c)

至t一个l

CLBs

最大

有

用户 i/o

最大

差别的

i/o pairs

Distributed

内存 位

块

内存 位

XC2S50E 1,728 23,000 - 50,000 16 x 24 384 182 84 24,576 32K

XC2S100E 2,700 37,000 - 100,000 20 x 30 600 202 86 38,400 40K

XC2S150E 3,888 52,000 - 150,000 24 x 36 864 263 114 55,296 48K

XC2S200E 5,292 71,000 - 200,000 28 x 42 1,176 289 120 75,264 56K

XC2S300E 6,912 93,000 - 300,000 32 x 48 1,536 329 120 98,304 64K