飞利浦 半导体 产品 规格

74als161b/74als163b4-位 二进制的 计数器

1991 二月 08

6

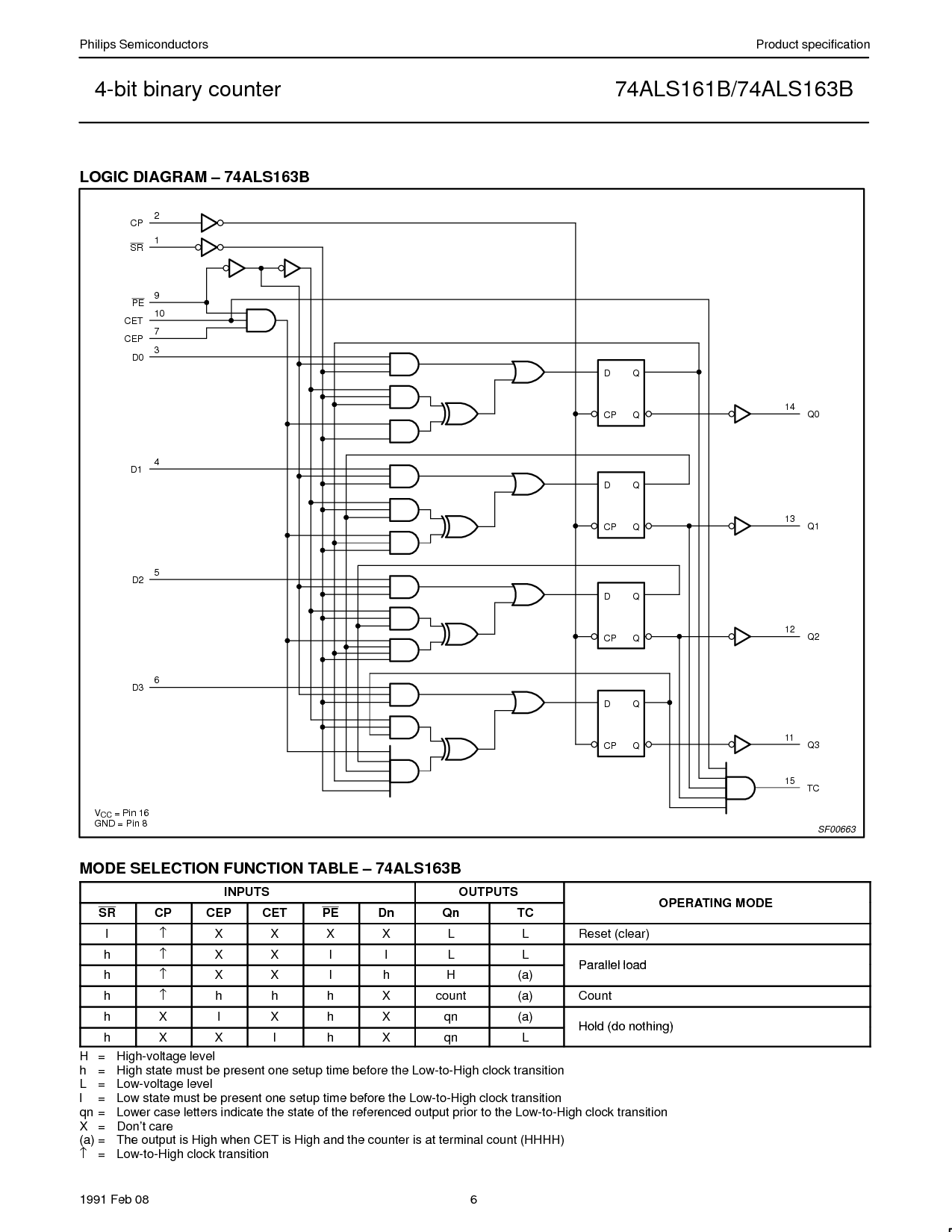

逻辑 图解 – 74als163b

D

CP

Q

Q

D

CP

Q

Q

D

CP

Q

Q

D

CP

Q

Q

14

Q0

13

Q1

12

Q2

11

Q3

15

TC

6

D3

5

D2

4

D1

3

D0

7

CEP

10

CET

9

PE

1

SR

2

CP

SF00663

V

CC

= 管脚 16

地 = 管脚 8

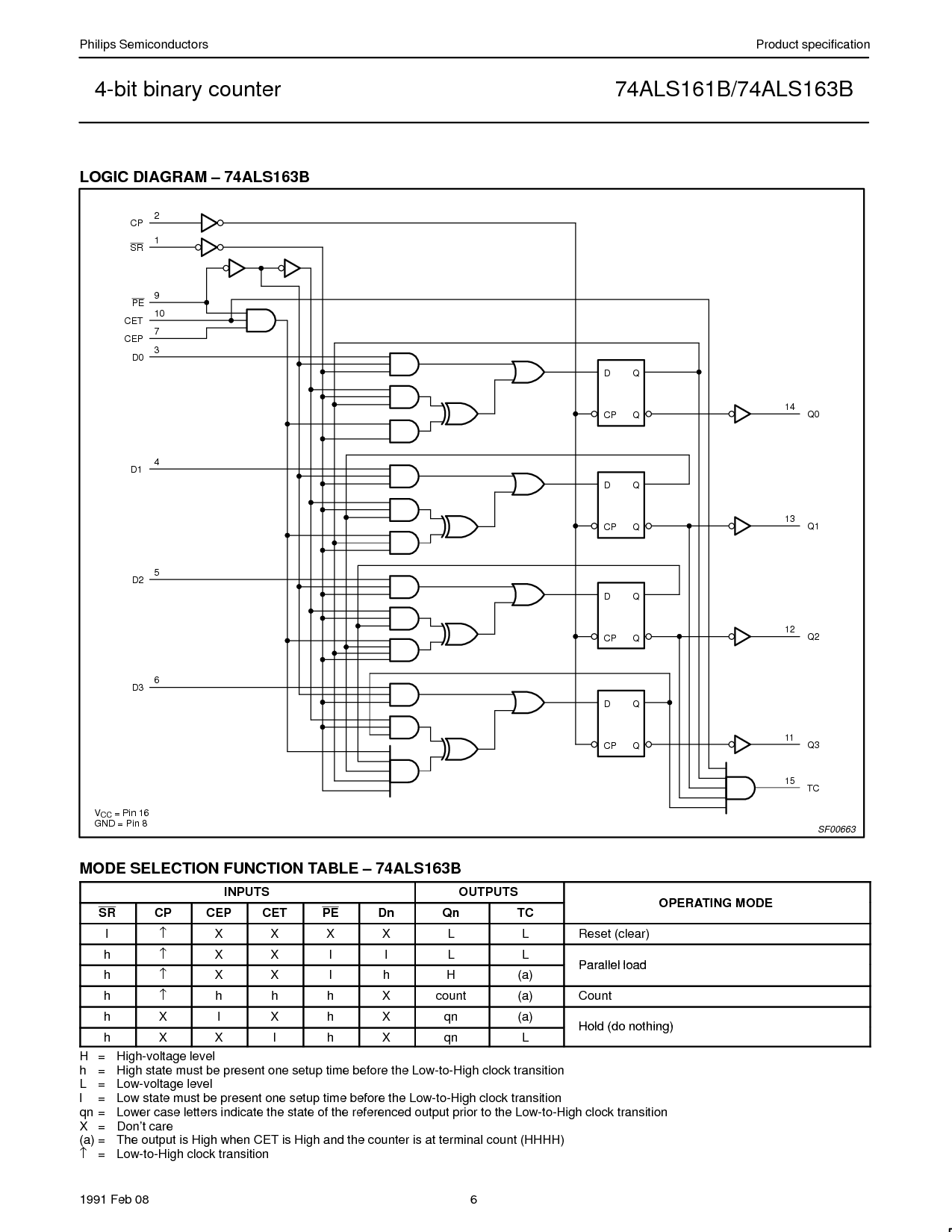

模式 选择 函数 表格 – 74als163b

输入 输出

运行 模式

SR CP CEP CET PE Dn Qn TC

运行 模式

l

↑

X X X X L L 重置 (clear)

h

↑

X X l l L L

并行的 加载

h

↑

X X l h H (一个)

并行的 加载

h

↑

h h h X 计数 (一个) 计数

h X l X h X qn (一个)

支撑 (做 nothing)

h X X l h X qn L

支撑 (做 nothing)

H = 高-电压 水平的

h = 高 状态 必须 是 呈现 一个 建制 时间 在之前 这 低-至-高 时钟 转变

L = 低-电压 水平的

l = 低 状态 必须 是 呈现 一个 建制 时间 在之前 这 低-至-高 时钟 转变

qn = 更小的 情况 letters 表明 这 状态 的 这 关联 输出 较早的 至 这 低-至-高 时钟 转变

X = don’t 小心

(一个) = 这 输出 是 高 当 cet 是 高 和 这 计数器 是 在 终端 计数 (hhhh)

↑

= 低-至-高 时钟 转变