idt72v805/72v815/72v825/72v835/72v845

3.3 v cmos 双 syncfifo™ 256 x 18, 512 x 18, 1,024 x 18, 4,096 x 18

商业的 和 工业的

温度 范围

9

便条:

1. 这 一样 选择 sequence 应用 至 读 从 这 寄存器.

REN

是 使能 和

读 是 执行 在 这 低-至-高 转变 的 rclk.

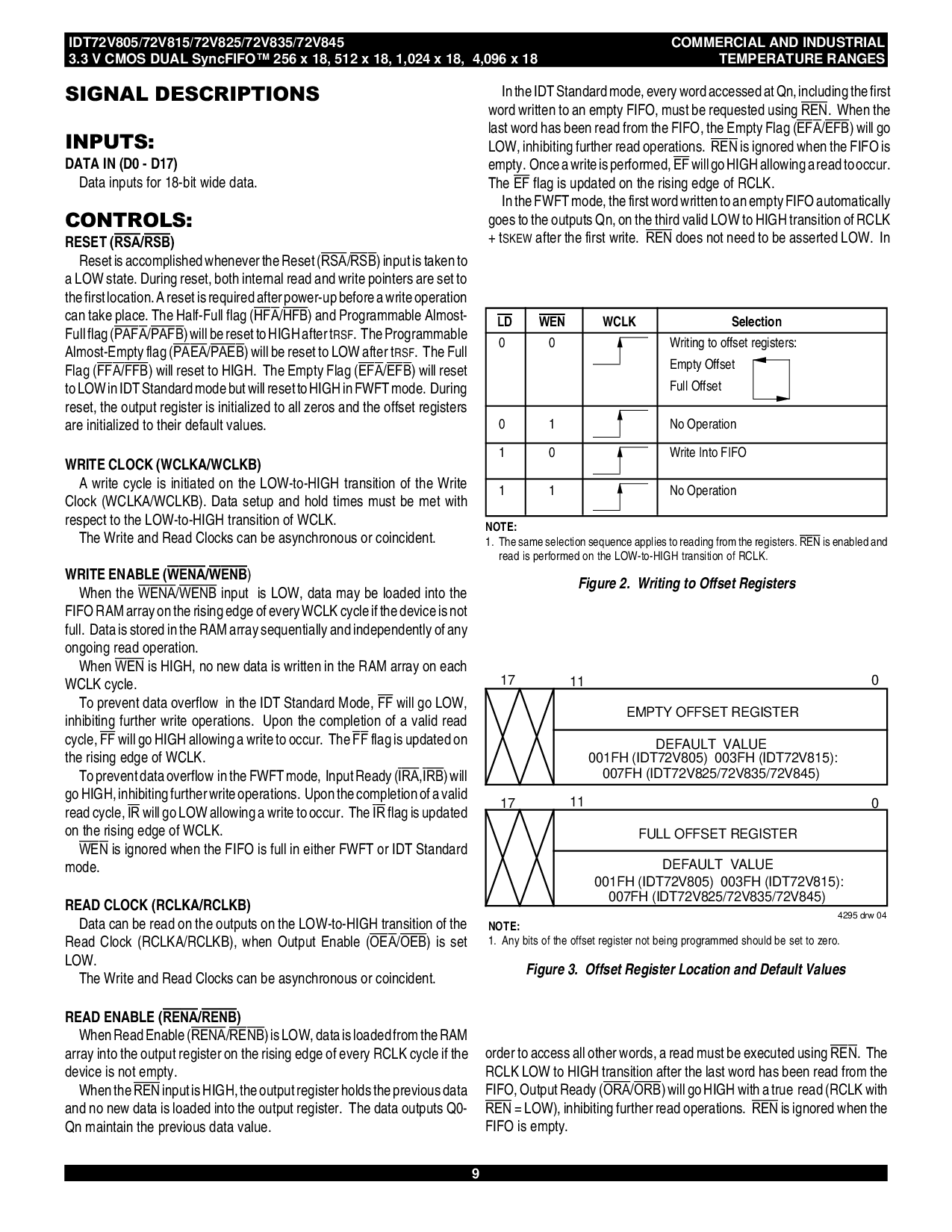

empty 补偿 寄存器

17

11

0

001fh (idt72v805) 003fh (idt72v815):

007fh (idt72v825/72v835/72v845)

全部 补偿 寄存器

17

11

0

default 值

default 值

001fh (idt72v805) 003fh (idt72v815):

007fh (idt72v825/72v835/72v845)

4295 drw 04

便条:

1. 任何 位 的 这 补偿 寄存器 不 正在 编写程序 应当 是 设置 至 零.

数据 在 (d0 - d17)

数据 输入 为 18-位 宽 数据.

重置 (

RSA

/

RSB

)

重置 是 accomplished whenever 这 重置 (

RSA

/

RSB

) 输入 是 带去 至

一个 低 状态. 在 重置, 两个都 内部的 读 和 写 pointers 是 设置 至

这 第一 location. 一个 重置 是 必需的 之后 电源-向上 在之前 一个 写 运作

能 引领 放置. 这 half-全部 标记 (

HFA

/

HFB

) 和 可编程序的 almost-

全部 标记 (

PAFA

/

PAFB

) 将 是 重置 至 高 之后 t

RSF

. 这 可编程序的

almost-empty 标记 (

PAEA

/

PAEB

) 将 是 重置 至 低 之后 t

RSF

. 这 全部

标记 (

ffa/ffb

) 将 重置 至 高. 这 empty 标记 (

EFA

/

EFB

) 将 重置

至 低 在 idt 标准 模式 但是 将 重置 至 高 在 fwft 模式. 在

重置, 这 输出 寄存器 是 initialized 至 所有 zeros 和 这 补偿 寄存器

是 initialized 至 它们的 default 值.

写 时钟 (wclka/wclkb)

一个 写 循环 是 initiated 在 这 低-至-高 转变 的 这 写

时钟 (wclka/wclkb). 数据 建制 和 支撑 时间 必须 是 符合 和

遵守 至 这 低-至-高 转变 的 wclk.

这 写 和 读 clocks 能 是 异步的 或者 coincident.

写 使能 (

WENA

/

WENB

)

当 这

WENA

/

WENB

输入 是 低, 数据 将 是 承载 在 这

先进先出 内存 排列 在 这 rising 边缘 的 每 wclk 循环 如果 这 设备 是 不

全部. 数据 是 贮存 在 这 内存 排列 sequentially 和 independently 的 任何

ongoing 读 运作.

当

WEN

是 高, 非 新 数据 是 写 在 这 内存 排列 在 各自

wclk 循环.

至 阻止 数据 overflow 在 这 idt 标准 模式,

FF

将 go 低,

inhibiting 更远 写 行动. 在之上 这 completion 的 一个 有效的 读

循环,

FF

将 go 高 准许 一个 写 至 出现. 这

FF

标记 是 updated 在

这 rising 边缘 的 wclk.

至 阻止 数据 overflow 在 这 fwft 模式, 输入 准备好 (

IRA

,

IRB

) 将

go 高, inhibiting 更远 写 行动. 在之上 这 completion 的 一个 有效的

读 循环,

IR

将 go 低 准许 一个 写 至 出现. 这

IR

标记 是 updated

在 这 rising 边缘 的 wclk.

WEN

是 ignored 当 这 先进先出 是 全部 在 也 fwft 或者 idt 标准

模式.

读 时钟 (rclka/rclkb)

数据 能 是 读 在 这 输出 在 这 低-至-高 转变 的 这

读 时钟 (rclka/rclkb), 当 输出 使能 (

OEA

/

OEB

) 是 设置

低.

这 写 和 读 clocks 能 是 异步的 或者 coincident.

读 使能 (

RENA

/

RENB

)

当 读 使能 (

RENA

/

RENB

) 是 低, 数据 是 承载 从 这 内存

排列 在 这 输出 寄存器 在 这 rising 边缘 的 每 rclk 循环 如果 这

设备 是 不 empty.

当 这

REN

输入 是 高, 这 输出 寄存器 holds 这 previous 数据

和 非 新 数据 是 承载 在 这 输出 寄存器. 这 数据 输出 q0-

qn 维持 这 previous 数据 值.

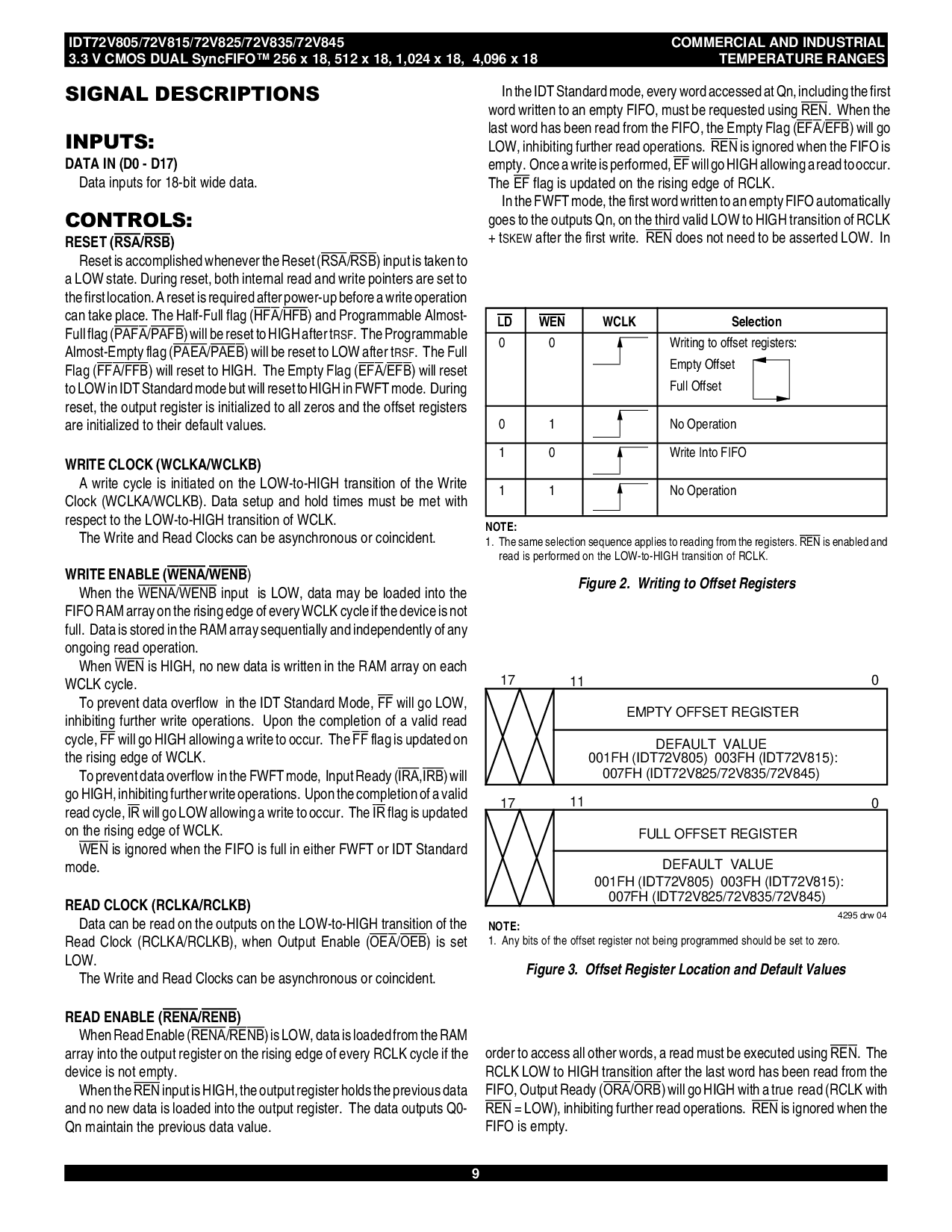

图示 2. writing 至 补偿 寄存器

图示 3. 补偿 寄存器 location 和 default 值

在 这 idt 标准 模式, 每 文字 accessed 在 qn, 包含 这 第一

文字 写 至 一个 empty 先进先出, 必须 是 要求 使用

REN

. 当 这

last 文字 有 被 读 从 这 先进先出, 这 empty 标记 (

EFA

/

EFB

) 将 go

低, inhibiting 更远 读 行动.

REN

是 ignored 当 这 先进先出 是

empty. once 一个 写 是 执行,

EF

将 go 高 准许 一个 读 至 出现.

这

EF

标记 是 updated 在 这 rising 边缘 的 rclk.

在 这 fwft 模式, 这 第一 文字 写 至 一个 empty 先进先出 automatically

变得 至 这 输出 qn, 在 这 第三 有效的 低 至 高 转变 的 rclk

+ t

SKEW

之后 这 第一 写.

REN

做 不 需要 至 是 asserted 低. 在

顺序 至 进入 所有 其它 words, 一个 读 必须 是 executed 使用

REN

. 这

rclk 低 至 高 转变 之后 这 last 文字 有 被 读 从 这

先进先出, 输出 准备好 (

ORA

/

ORB

) 将 go 高 和 一个 真实 读 (rclk 和

REN

= 低), inhibiting 更远 读 行动.

REN

是 ignored 当 这

先进先出 是 empty.

LD WEN

WCLK 选择

0 0 writing 至 补偿 寄存器:

empty 补偿

全部 补偿

0 1 非 运作

1 0 写 在 先进先出

1 1 非 运作