1999 十一月 23 2

飞利浦 半导体 产品 规格

octal d-类型 transparent 获得; 3-状态 74ahc373; 74ahct373

特性

•

静电释放 保护:

HBM eia/jesd22-a114-一个 超过 2000 V

MM eia/jesd22-a115-一个 超过 200 V

CDM eia/jesd22-c101 超过 1000 V

•

保持平衡 传播 延迟

•

所有 输入 有 施密特-触发 actions

•

输入 accepts 电压 高等级的 比 v

CC

•

一般 3-状态 输出 使能 输入

•

functionally 完全同样的 至 这 ‘533’, ‘563’ 和 ‘573’

•

为 ahc 仅有的: 运作 和 CMOS 输入 水平

•

为 ahct 仅有的: 运作 和 TTL 输入 水平

•

指定 从

−

40 至 +85

°

c 和

−

40 至 +125

°

c.

描述

这 74ahc/ahct373 是 高-速 si-门 cmos

设备 和 是 管脚 兼容 和 低 电源 肖特基

ttl (lsttl). 它们 是 指定 在 遵从 和

电子元件工业联合会 标准 非. 7a.

这 74ahc/ahct373 是 octal d-类型 transparent

latches featuring 独立的 d-类型 输入 为 各自 获得 和

3-状态 输出 为 总线 朝向 产品. 一个 获得

使能 (le) 输入 和 一个 输出 使能 (oe) 输入 是

一般 至 所有 latches.

这 ‘373’ 组成 的 第八 d-类型 transparent latches 和

3-状态 真实 输出. 当 le 是 高, 数据 在 这

D

n

输入 enters 这 latches. 在 这个 情况 这 latches

是 transparent, i.e. 一个 获得 输出 将 改变 状态 各自

时间 它的 相应的 d-输入 改变.

当 le 是 低 这 latches store 这 信息 那

是 呈现 在 这 d-输入 一个 设置-向上 时间 preceding 这

高-至-低 转变 的 le. 当 oe 是 低, 这

内容 的 这 8 latches 是 有 在 这 输出.

当 oe 是 高, 这 输出 go 至 这 高-阻抗

止-状态. 运作 的 这 oe 输入 做 不 影响 这

状态 的 这 latches.

这 ‘373’ 是 functionally 完全同样的 至 这 ‘533’, ‘563’ 和

‘573’, 但是 这 ‘533’ 和 ‘563’ 有 inverted 输出 和 这

‘563’ 和 ‘573’ 有 一个 不同的 管脚 arrangement.

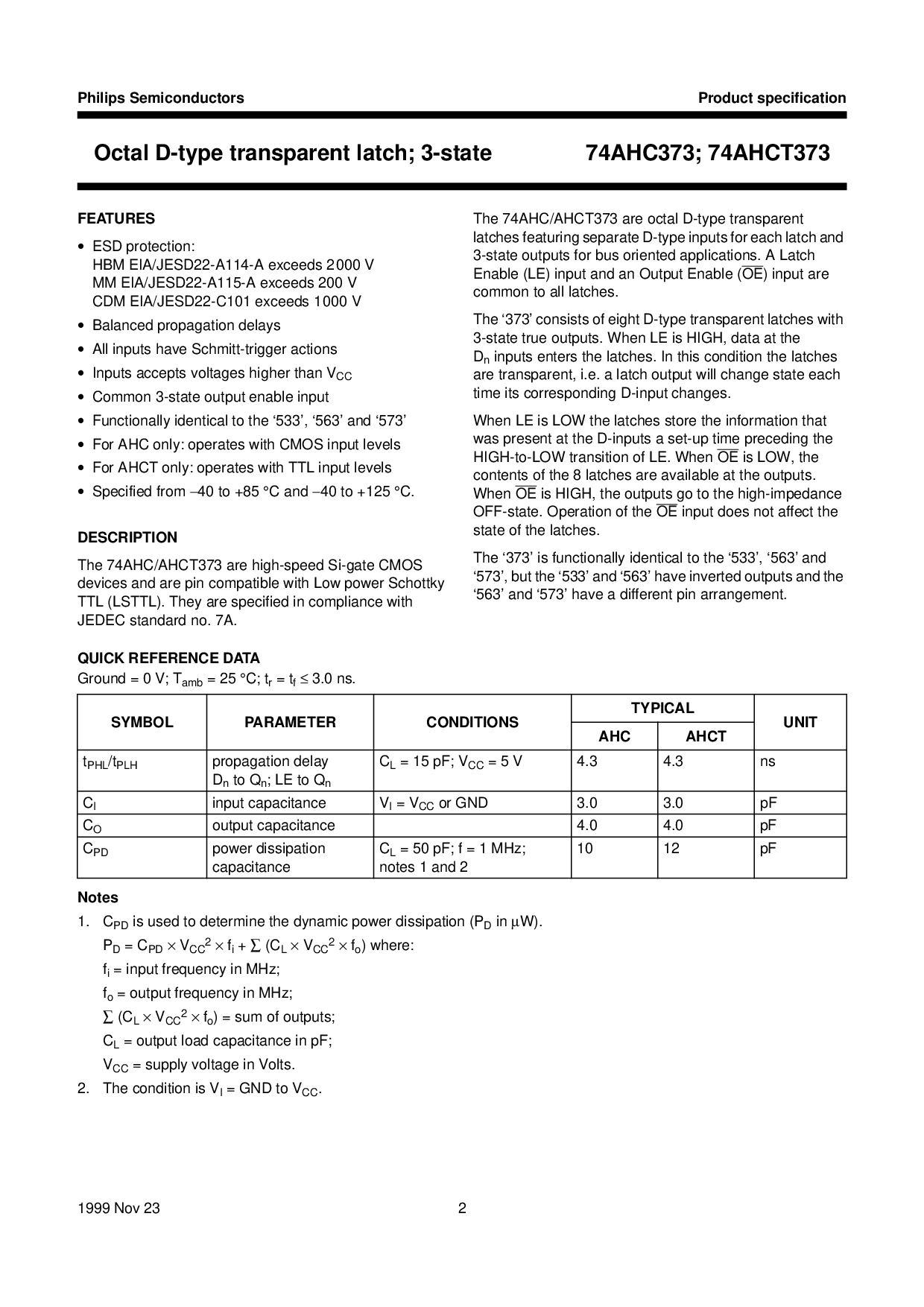

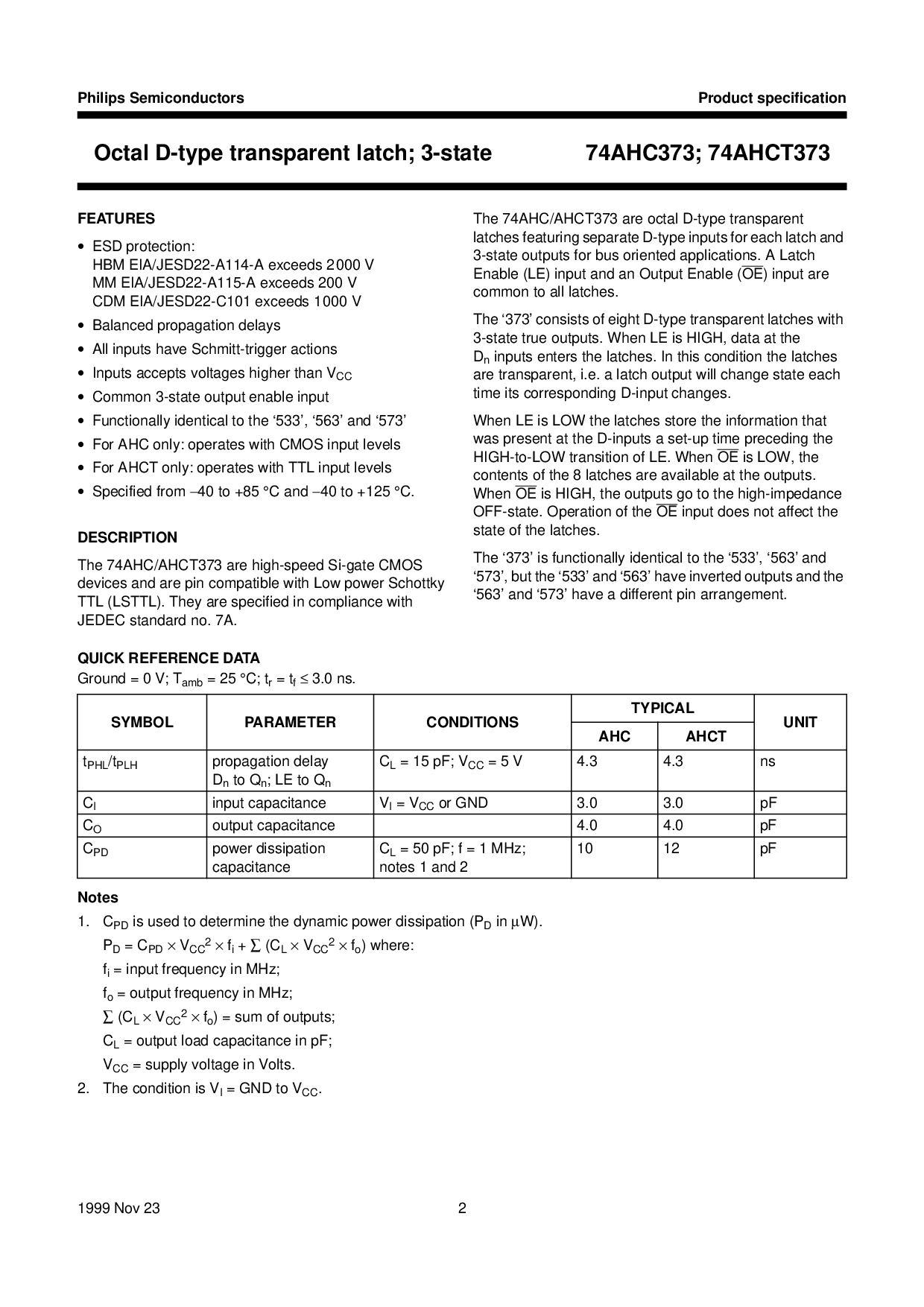

快 涉及 数据

地面 = 0 v; t

amb

=25

°

c; t

r

=t

f

≤

3.0 ns.

注释

1. C

PD

是 使用 至 决定 这 动态 电源 消耗 (p

D

在

µ

w).

P

D

=C

PD

×

V

CC

2

×

f

i

+

∑

(c

L

×

V

CC

2

×

f

o

) 在哪里:

f

i

= 输入 频率 在 mhz;

f

o

= 输出 频率 在 mhz;

∑

(c

L

×

V

CC

2

×

f

o

) = 总 的 输出;

C

L

= 输出 加载 电容 在 pf;

V

CC

= 供应 电压 在 伏特.

2. 这 情况 是 v

I

= 地 至 v

CC

.

标识 参数 情况

典型

单位

AHC AHCT

t

PHL

/t

PLH

传播 延迟

D

n

至 Q

n

; le 至 Q

n

C

L

= 15 pf; v

CC

= 5 V 4.3 4.3 ns

C

I

输入 电容 V

I

=V

CC

或者 地 3.0 3.0 pF

C

O

输出 电容 4.0 4.0 pF

C

PD

电源 消耗

电容

C

L

= 50 pf; f = 1 mhz;

注释 1 和 2

10 12 pF