www.fairchildsemi.com 2

74VHC164

函数的 描述

这 vhc164 是 一个 边缘-triggered 8-位 变换 寄存器 和

串行 数据 entry 和 一个 输出 从 各自 的 这 第八

stages. 数据 是 entered serially 通过 一个 的 二 输入

(一个 或者 b); 也 的 这些 输入 能 是 使用 作 一个 起作用的

高 使能 为 数据 entry 通过 这 其它 输入. 一个

unused 输入 必须 是 系 高.

各自 低-至-高 转变 在 这 时钟 (cp) 输入

shifts 数据 一个 放置 至 这 正确的 和 enters 在 q

0

这 log-

ical 和 的 这 二 数据 输入 (一个 • b) 那 existed 在之前

这 rising 时钟 边缘. 一个 低 水平的 在 这 主控 重置

(mr

) 输入 overrides 所有 其它 输入 和 clears 这 寄存器

asynchronously, forcing 所有 q 输出 低.

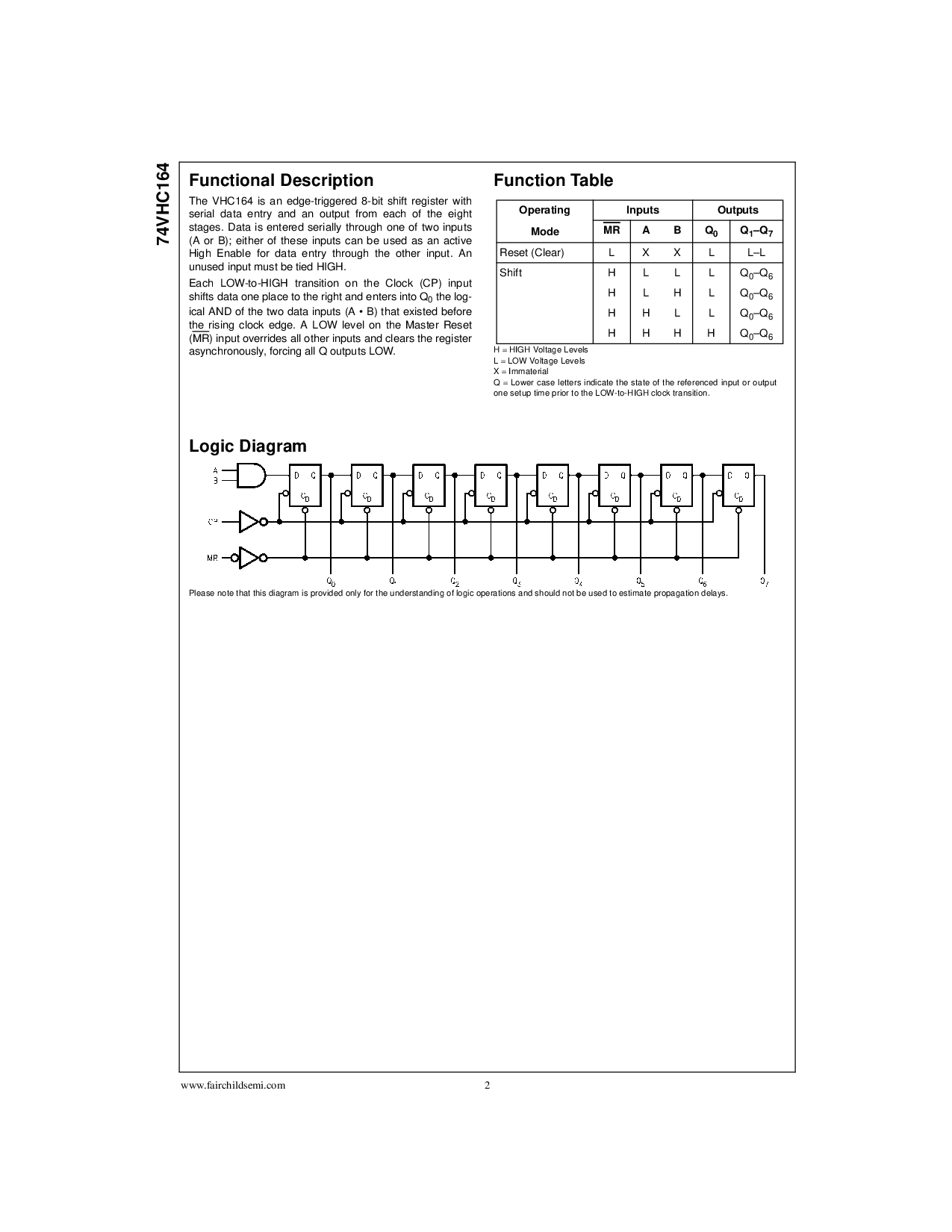

函数 表格

H

=

高 电压 水平

L

=

低 电压 水平

X

=

Immaterial

Q

=

更小的 情况 letters 表明 这 状态 的 这 关联 输入 或者 输出

一个 建制 时间 较早的 至 这 低-至-高 时钟 转变.

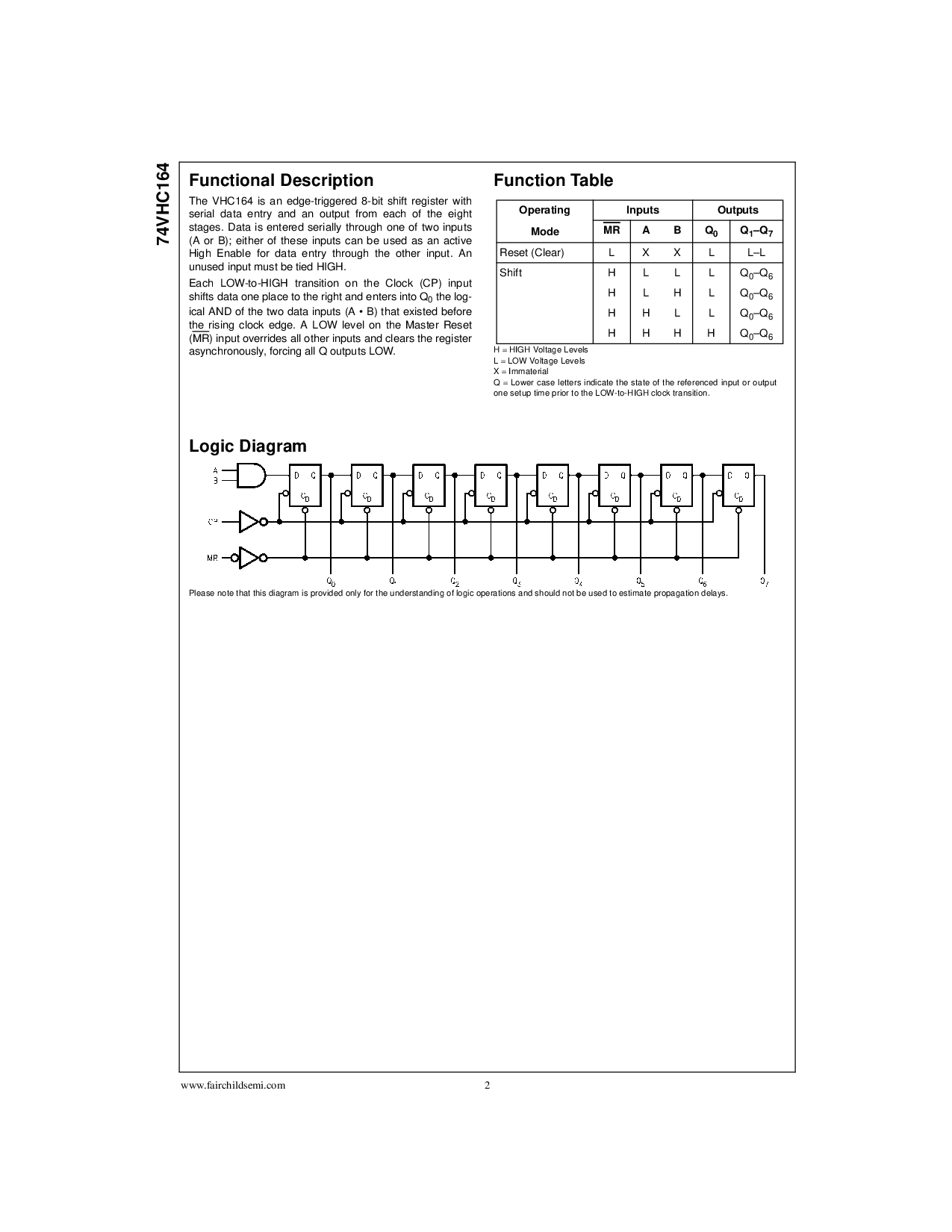

逻辑 图解

请 便条 那 这个 图解 是 提供 仅有的 为 这 understanding 的 逻辑 行动 和 应当 不 是 使用 至 估计 传播 延迟.

运行 输入 输出

模式

MR

ABQ

0

Q

1

–Q

7

重置 (clear) L X X L

L–L

变换 H L L L Q

0

–Q

6

HLHLQ

0

–Q

6

HHL LQ

0

–Q

6

HHHHQ

0

–Q

6