rev. 一个

–3–

AD1895

数字的 定时 (–40

c < t

一个

< +105

c, vdd_核心 = 3.3 v

5%, vdd_io = 5.0 v

10%)

参数

1

最小值 最大值 单位

t

MCLKI

mclk_i 时期 33.3 ns

f

MCLK

mclk_i 频率 30.0

2, 3

MHz

t

MPWH

mclk_i pulsewidth 高 8 ns

t

MPWL

mclk_i pulsewidth 低 12 ns

输入 串行 端口 定时

t

LRIS

lrclk_i 建制 至 sclk_i 8 ns

t

SIH

sclk_i pulsewidth 高 8 ns

t

SIL

sclk_i pulsewidth 低 8 ns

t

DIS

sdata_i 建制 至 sclk_i rising 边缘 8 ns

t

DIH

sdata_i 支撑 从 sclk_i rising 边缘 3 ns

输出 串行 端口 定时

t

TDMS

tdm_在 建制 至 sclk_o 下落 边缘 3 ns

t

TDMH

tdm_在 支撑 从 sclk_o 下落 边缘 3 ns

t

DOPD

sdata_o 传播 延迟 从 sclk_o, lrclk_o 20 ns

t

DOH

sdata_o 支撑 从 sclk_o 3 ns

t

LROS

lrclk_o 建制 至 sclk_o (tdm 模式 仅有的) 5 ns

t

LROH

lrclk_o 支撑 从 sclk_o (tdm 模式 仅有的) 3 ns

t

SOH

sclk_o pulsewidth 高 10 ns

t

SOL

sclk_o pulsewidth 低 5 ns

t

RSTL

重置 pulsewidth lo 200 ns

注释

1

谈及 至 定时 图解 部分.

2

这 最大 可能 样本 比率 是:

FS

最大值

=

f

MCLK

/138.

3

f

MCLK

的 向上 至 34 mhz 是 可能 下面 这 下列的 情况: 0

°

c < t

一个

< 70

°

c, 45/55 或者 更好的 mclk_i 职责 循环.

规格 主题 至 改变 没有 注意.

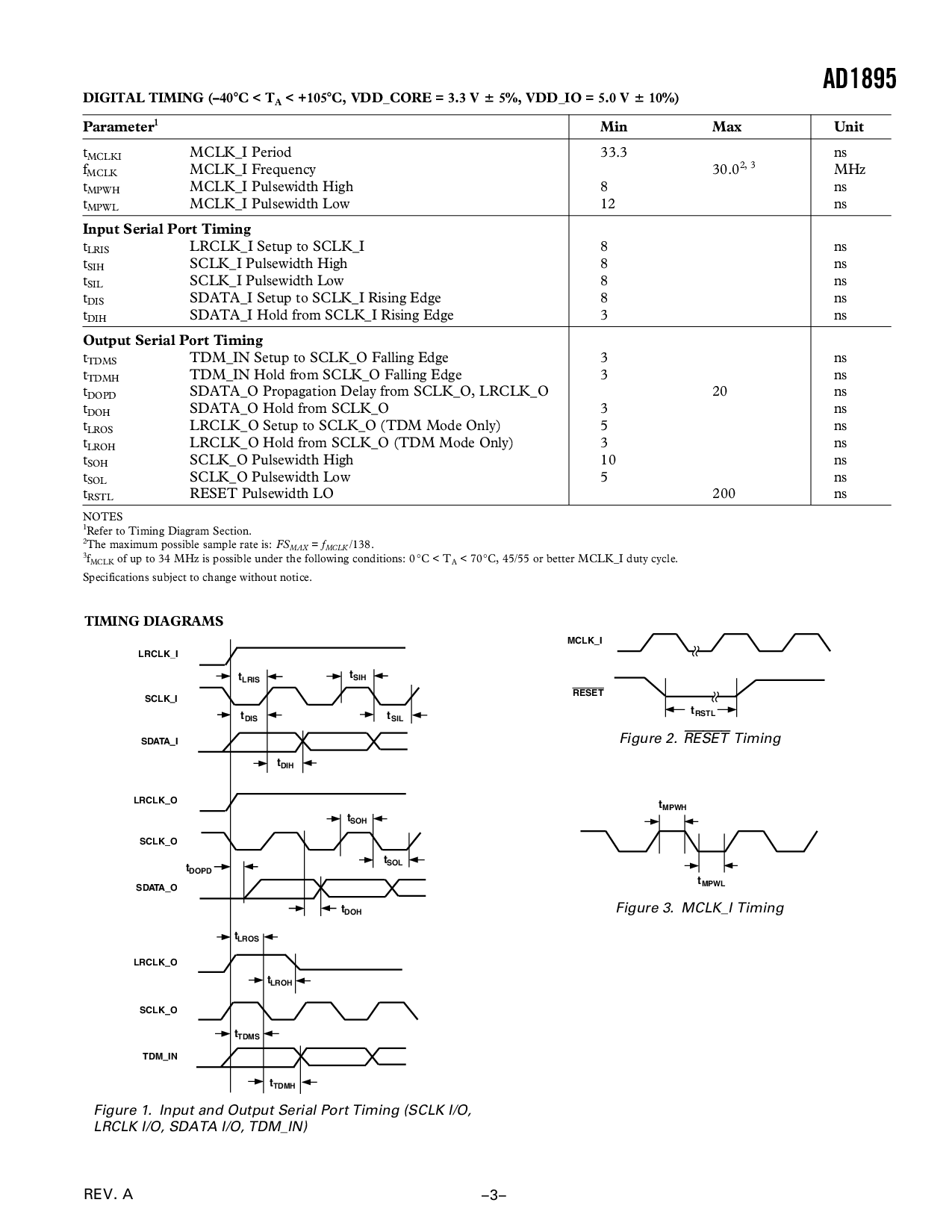

定时 图解

t

LRIS

t

SIH

t

DIS

t

SIL

t

DIH

t

LROS

t

SOH

t

DOPD

t

SOL

t

DOH

t

LROH

t

TDMS

t

TDMH

lrclk_i

SCLK

I

SDATA

I

LRCLK

O

SCLK

O

SDATA

O

LRCLK

O

SCLK

O

TDM

在

图示 1. 输入 和 输出 串行 端口 定时 (sclk i/o,

lrclk i/o, sdata i/o, tdm_在)

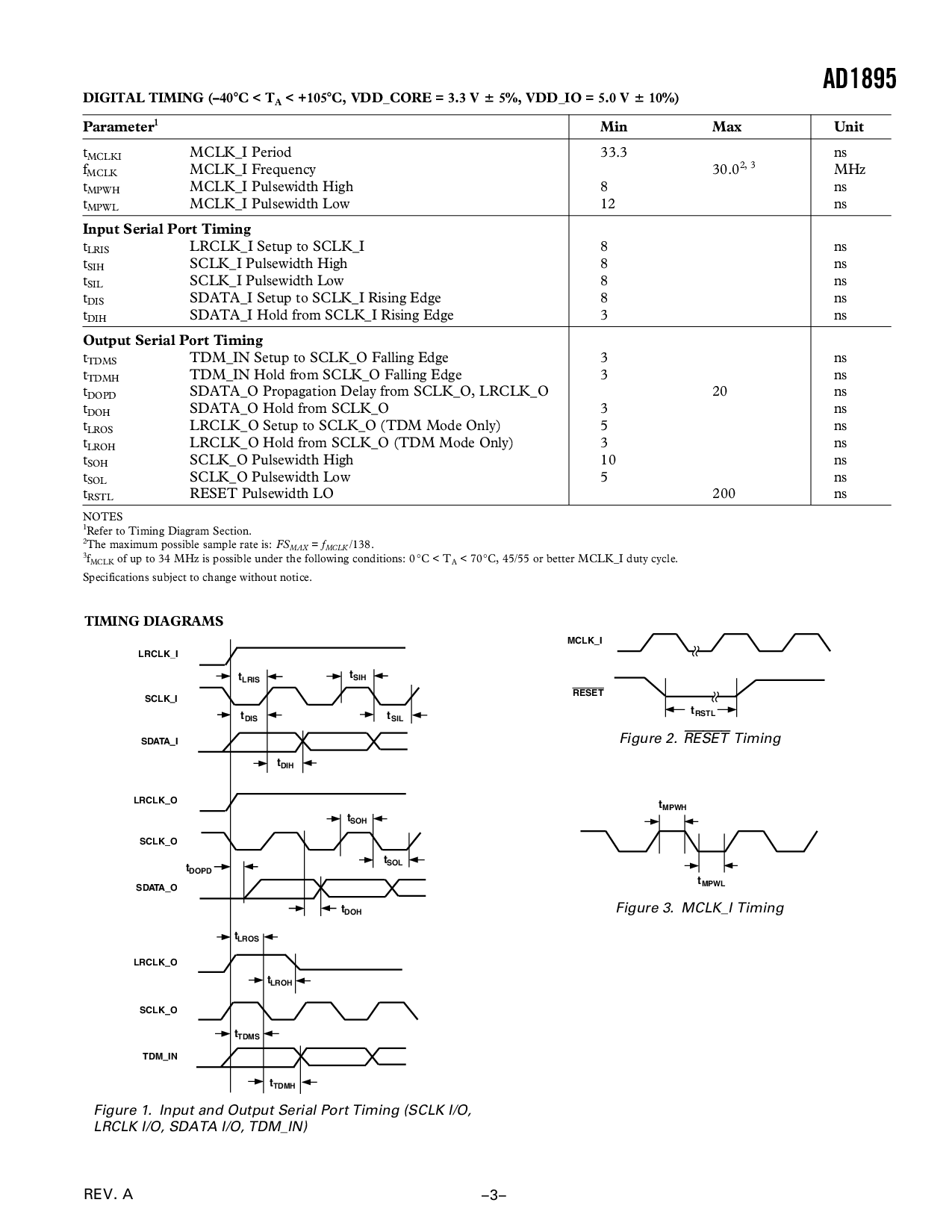

t

RSTL

MCLK I

重置

图示 2.

重置

定时

t

MPWH

t

MPWL

图示 3. mclk_i 定时