rev. 一个

–4–

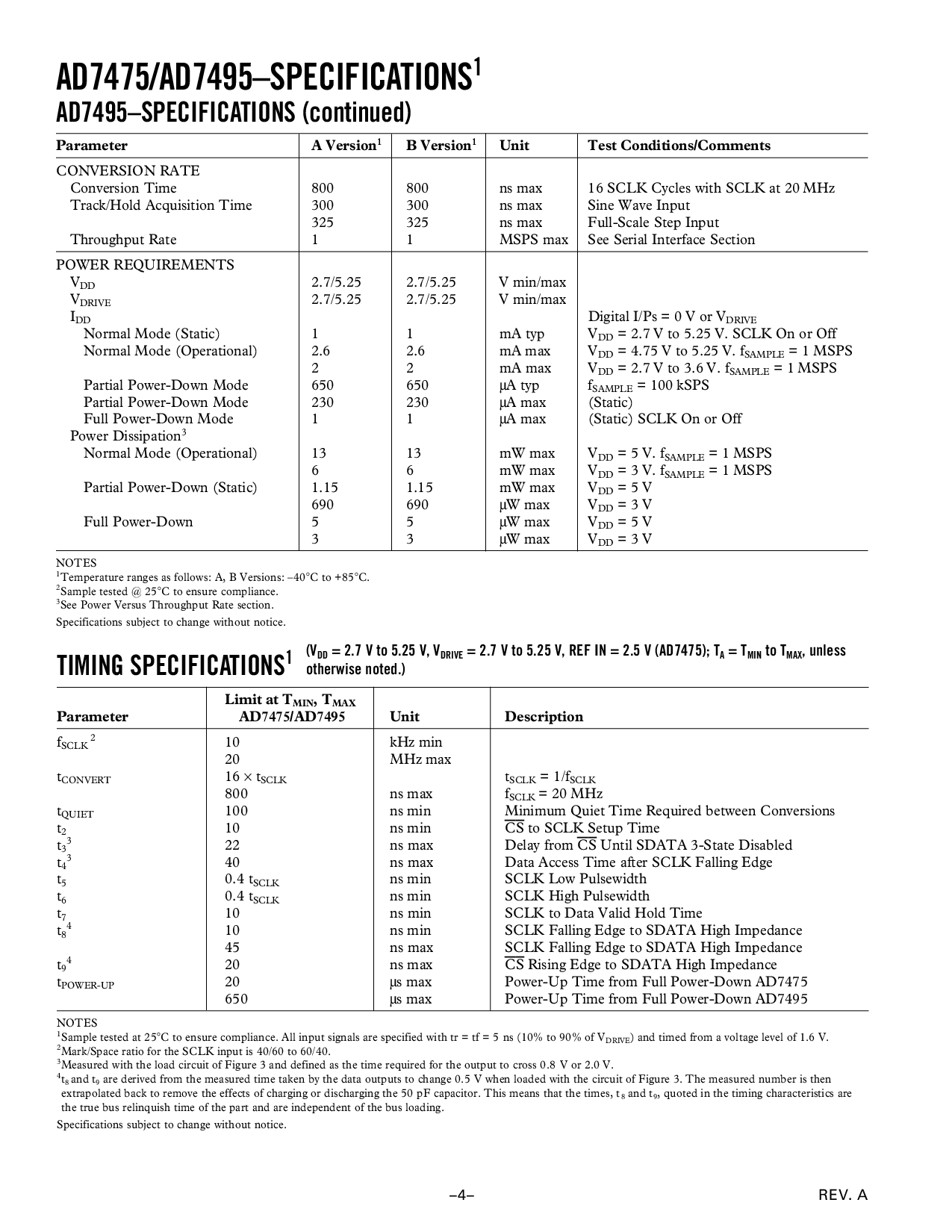

ad7475/ad7495–specifications

1

ad7495–specifications (持续)

参数 一个 版本

1

b 版本

1

单位 测试 情况/comments

转换 比率

转换 时间 800 800 ns 最大值 16 sclk 循环 和 sclk 在 20 MHz

追踪/支撑 acquisition 时间 300 300 ns 最大值 sine 波 输入

325 325 ns 最大值 全部-规模 步伐 输入

throughput 比率 1 1 msps 最大值 看 串行 接口 部分

电源 (所需的)东西

V

DD

2.7/5.25 2.7/5.25 v 最小值/最大值

V

驱动

2.7/5.25 2.7/5.25 v 最小值/最大值

I

DD

数字的 i/ps = 0 v 或者 v

驱动

正常的 模式 (静态的) 1 1 毫安 典型值 V

DD

= 2.7 v 至 5.25 v. sclk 在 或者 止

正常的 模式 (运算的) 2.6 2.6 毫安 最大值 V

DD

= 4.75 v 至 5.25 v. f

样本

= 1 MSPS

2 2 毫安 最大值 V

DD

= 2.7 v 至 3.6 v. f

样本

= 1 MSPS

partial 电源-向下 模式 650 650

µ

一个 典型值 f

样本

= 100 kSPS

partial 电源-向下 模式 230 230

µ

一个 最大值 (静态的)

全部 电源-向下 模式 1 1

µ

一个 最大值 (静态的) sclk 在 或者 止

电源 消耗

3

正常的 模式 (运算的) 13 13 mw 最大值 V

DD

= 5 v. f

样本

= 1 MSPS

6 6 mw 最大值 V

DD

= 3 v. f

样本

= 1 MSPS

partial 电源-向下 (静态的) 1.15 1.15 mw 最大值 V

DD

= 5 V

690 690

µ

w 最大值 V

DD

= 3 V

全部 电源-向下 5 5

µ

w 最大值 V

DD

= 5 V

33

µ

w 最大值 V

DD

= 3 V

注释

1

温度 范围 作 跟随: 一个, b 版本: –40

c 至 +85

c.

2

样本 测试 @ 25

c 至 确保 遵从.

3

看 电源 相比 throughput 比率 部分.

规格 主题 至 改变 没有 注意.

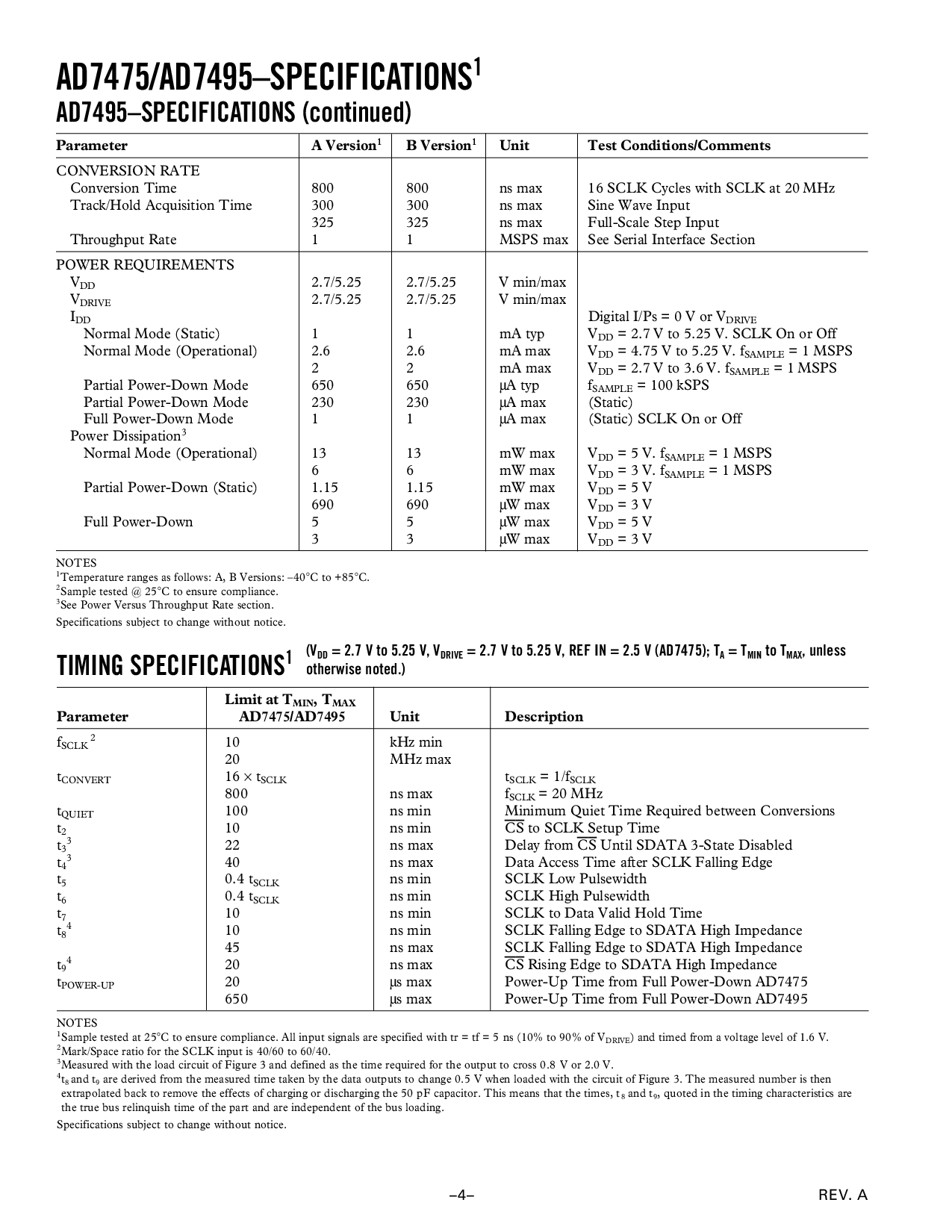

定时 规格

1

(v

DD

= 2.7 v 至 5.25 v, v

驱动

= 2.7 v 至 5.25 v, ref 在 = 2.5 v (ad7475); t

一个

= t

最小值

至 t

最大值

, 除非

否则 指出.)

限制 在 t

最小值

, t

最大值

参数 ad7475/ad7495 单位 描述

f

SCLK

2

10 khz 最小值

20 mhz 最大值

t

转变

16

×

t

SCLK

t

SCLK

= 1/f

SCLK

800 ns 最大值 f

SCLK

= 20 MHz

t

安静

100 ns 最小值 最小 安静 时间 必需的 在 conversions

t

2

10 ns 最小值

CS

至 sclk 建制 时间

t

3

3

22 ns 最大值 延迟 从

CS

直到 sdata 3-状态 无能

t

4

3

40 ns 最大值 数据 进入 时间 之后 sclk 下落 边缘

t

5

0.4 t

SCLK

ns 最小值 sclk 低 pulsewidth

t

6

0.4 t

SCLK

ns 最小值 sclk 高 pulsewidth

t

7

10 ns 最小值 sclk 至 数据 有效的 支撑 时间

t

8

4

10 ns 最小值 sclk 下落 边缘 至 sdata 高 阻抗

45 ns 最大值 sclk 下落 边缘 至 sdata 高 阻抗

t

9

4

20 ns 最大值

CS

rising 边缘 至 sdata 高 阻抗

t

电源-向上

20

µ

s 最大值 电源-向上 时间 从 全部 电源-向下 ad7475

650

µ

s 最大值 电源-向上 时间 从 全部 电源-向下 ad7495

注释

1

样本 测试 在 25

c 至 确保 遵从. 所有 输入 信号 是 指定 和 tr = tf = 5 ns (10% 至 90% 的 v

驱动

) 和 安排时间 从 一个 电压 水平的 的 1.6 v.

2

mark/空间 比率 为 这 sclk 输入 是 40/60 至 60/40.

3

量过的 和 这 加载 电路 的 图示 3 和 定义 作 这 时间 必需的 为 这 输出 至 交叉 0.8 v 或者 2.0 v.

4

t

8

和 t

9

是 获得 从 这 量过的 时间 带去 用 这 数据 输出 至 改变 0.5 v 当 承载 和 这 电路 的 图示 3. 这 量过的 号码 是 然后

extrapolated 后面的 至 除去 这 影响 的 charging 或者 discharging 这 50 pf 电容. 这个 意思 那 这 时间, t

8

和 t

9

, quoted 在 这 定时 特性 是

这 真实 总线 relinquish 时间 的 这 部分 和 是 独立 的 这 总线 加载.

规格 主题 至 改变 没有 注意.