2

AT29C256

0046p–flash–10/04

至 准许 为 简单的 在-系统 reprogrammability, 这 at29c256 做 不 需要 高

输入 电压 为 程序编制. five-volt-仅有的 commands 决定 这 运作 的

这 设备. 读 数据 输出 的 这 设备 是 类似的 至 读 从 一个 静态的 内存.

reprogramming 这 at29c256 是 执行 在 一个 页 基准; 64 字节 的 数据 是

承载 在 这 设备 和 然后 同时发生地 编写程序. 这 内容 的 这 全部

设备 将 是 erased 用 使用 一个 六-字节 软件 代号 (虽然 erasure 在之前 pro-

gramming 是 不 需要).

在 一个 reprogram 循环, 这 地址 locations 和 64 字节 的 数据 是 内部

latched, freeing 这 地址 和 数据 总线 为 其它 行动. 下列的 这 initiation 的

一个 程序 循环, 这 设备 将 automatically 擦掉 这 页 和 然后 程序 这

latched 数据 使用 一个 内部的 控制 计时器. 这 终止 的 一个 程序 循环 能 是 发现

用 数据

polling 的 i/o7. once 这 终止 的 一个 程序 循环 有 被 发现 一个 新

进入 为 一个 读, 程序 或者 碎片 擦掉 能 begin.

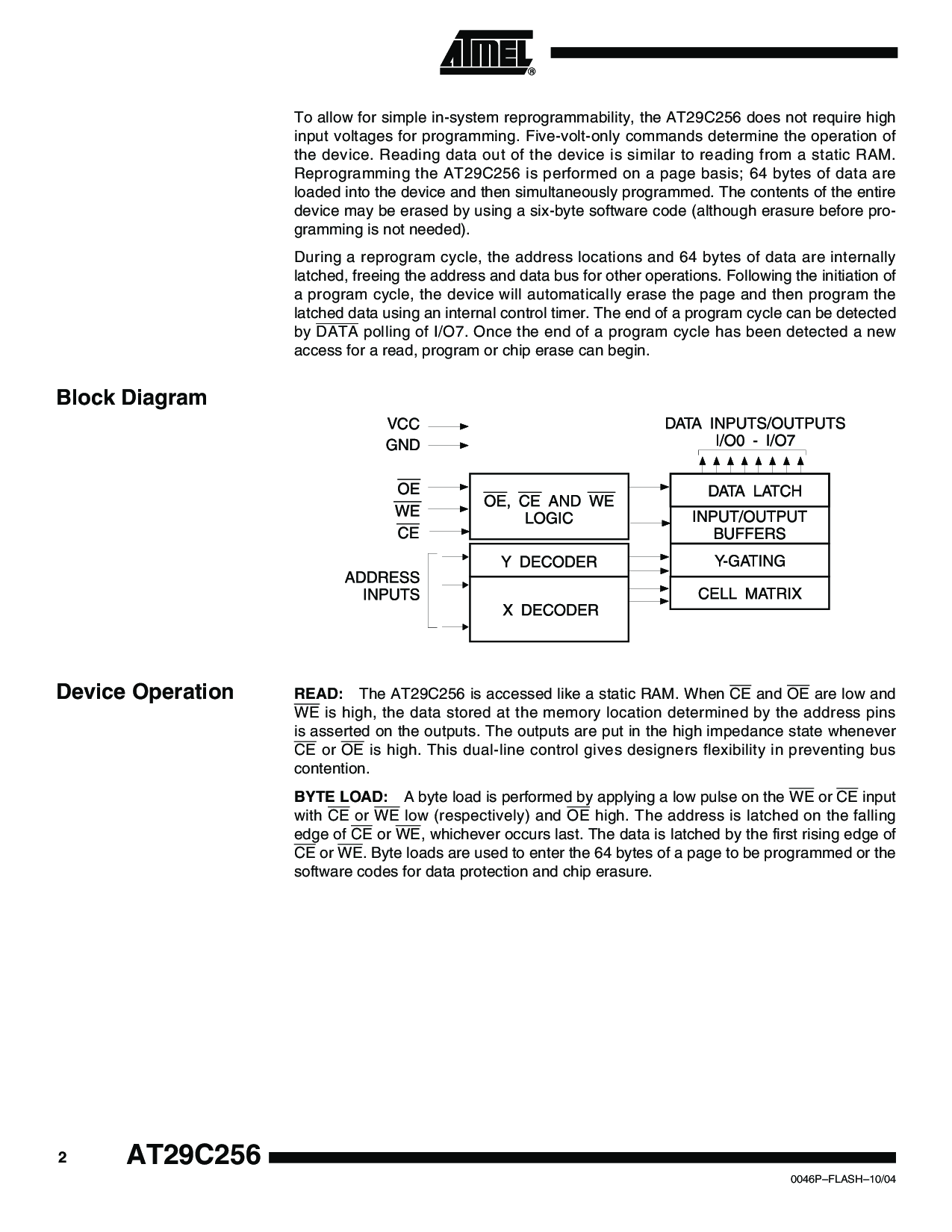

块 图解

设备 运作

读:

这 at29c256 是 accessed 像 一个 静态的 内存. 当 ce和 oe是 低 和

我们

是 高, 这 数据 贮存 在 这 记忆 location 决定 用 这 地址 管脚

是 asserted 在 这 输出. 这 输出 是 放 在 这 高 阻抗 状态 whenever

CE

或者 oe是 高. 这个 双-线条 控制 给 designers flexibility 在 阻止 总线

contention.

字节 加载:

一个 字节 加载 是 执行 用 应用 一个 低 脉冲波 在 这 我们

或者 ce输入

和 ce

或者 我们低 (各自) 和 oe高. 这 地址 是 latched 在 这 下落

边缘 的 ce

或者 我们, whichever occurs last. 这 数据 是 latched 用 这 第一 rising 边缘 的

CE

或者 我们. 字节 负载 是 使用 至 enter 这 64 字节 的 一个 页 至 是 编写程序 或者 这

软件 代号 为 数据 保护 和 碎片 erasure.