AD767

rev. 一个

–8–

c1068a–10–4/88

打印 在 美国

图示 9. tms32020 – ad767 接口

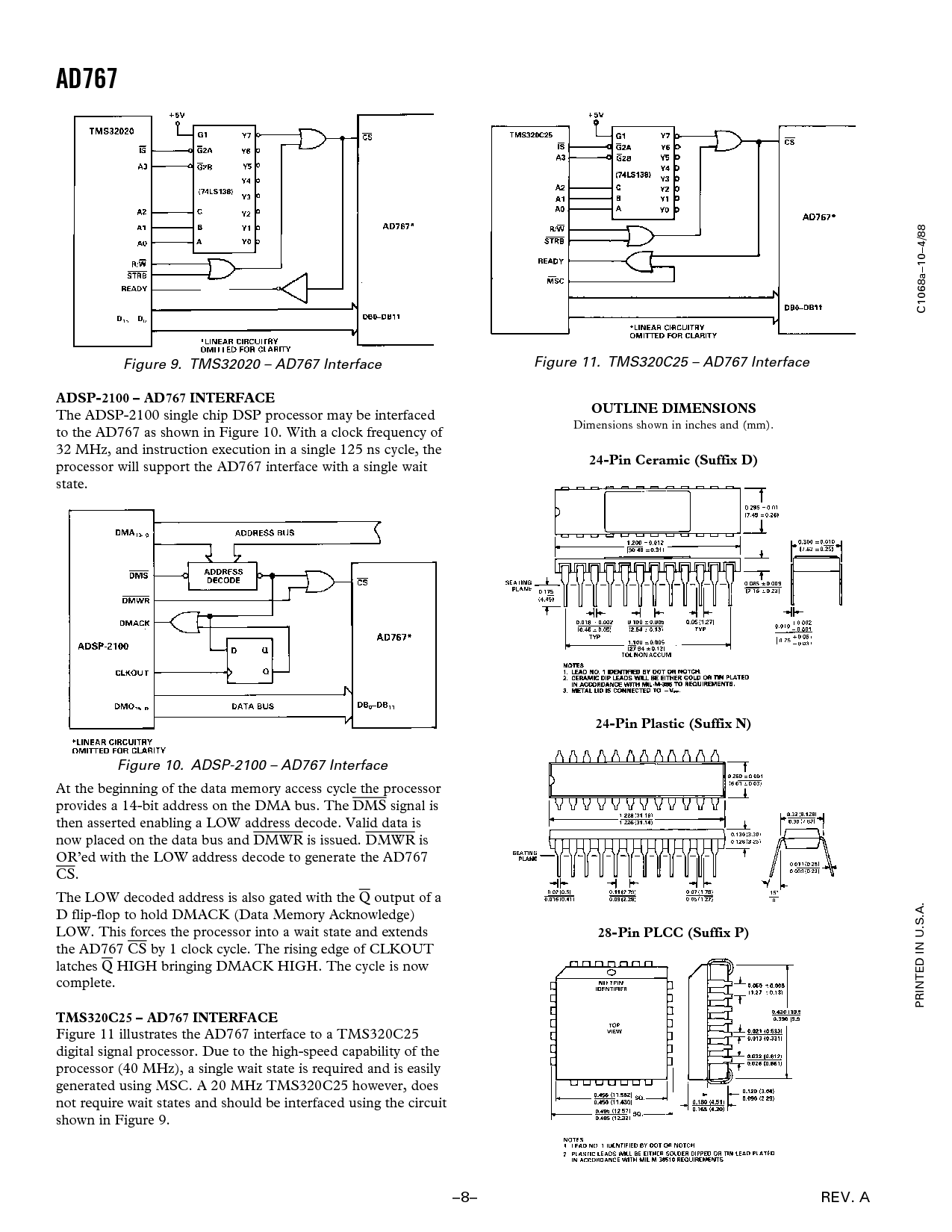

adsp-2100 – ad767 接口

这 adsp-2100 单独的 碎片 dsp 处理器 将 是 连接

至 这 ad767 作 显示 在 图示 10. 和 一个 时钟 频率 的

32 mhz, 和 操作指南 执行 在 一个 单独的 125 ns 循环, 这

处理器 将 支持 这 ad767 接口 和 一个 单独的 wait

状态.

图示 10. adsp-2100 – ad767 接口

在 这 beginning 的 这 数据 记忆 进入 循环 这 处理器

提供 一个 14-位 地址 在 这 dma 总线. 这

DMS

信号 是

然后 asserted enabling 一个 低 地址 decode. 有效的 数据 是

now 放置 在 这 数据 总线 和

DMWR

是 issued.

DMWR

是

或者’ed 和 这 低 地址 decode 至 发生 这 ad767

CS

.

这 低 解码 地址 是 也 gated 和 这

Q

输出 的 一个

d flip-flop 至 支撑 dmack (数据 记忆 acknowledge)

低. 这个 forces 这 处理器 在 一个 wait 状态 和 extends

这 ad767

CS

用 1 时钟 循环. 这 rising 边缘 的 clkout

latches

Q

高 bringing dmack 高. 这 循环 是 now

完全.

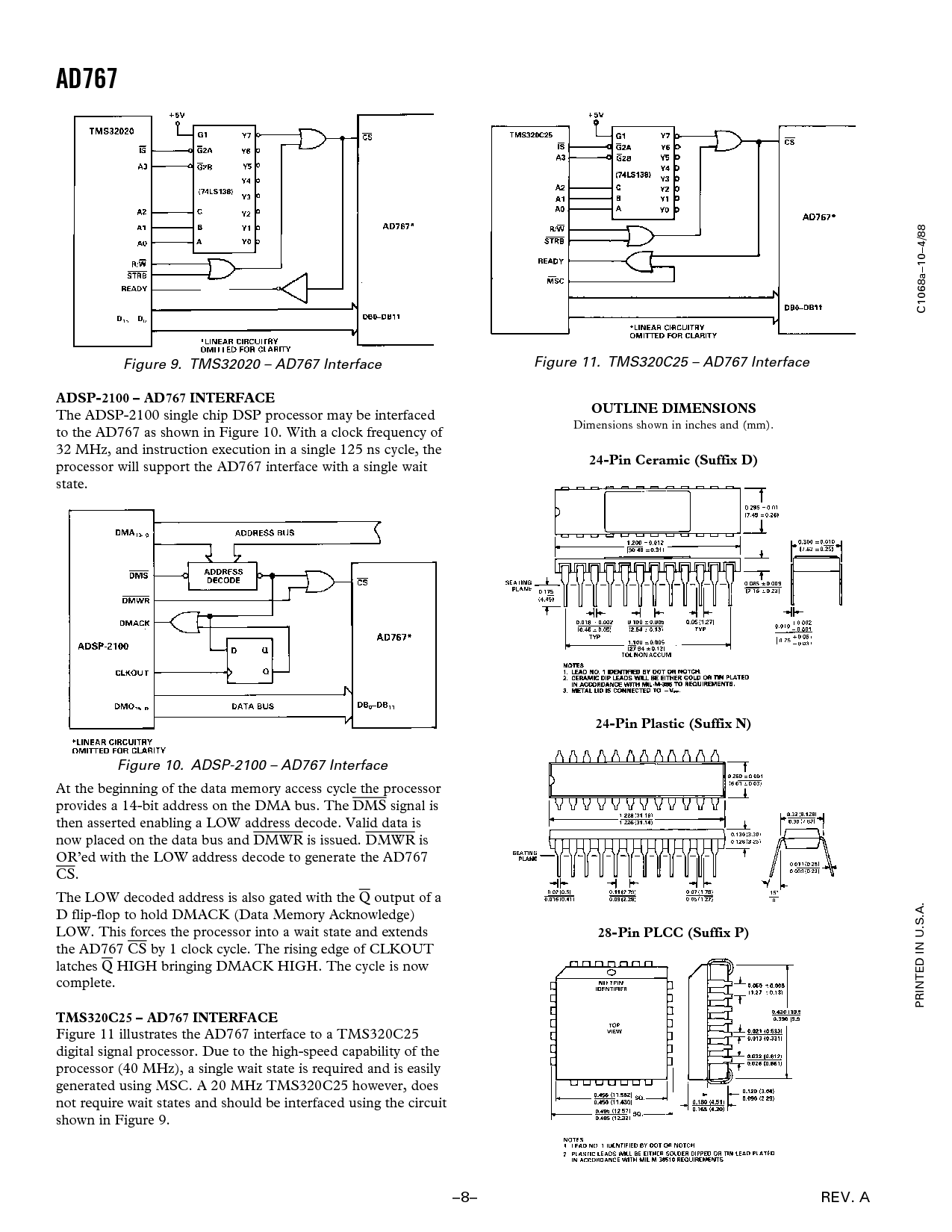

tms320c25 – ad767 接口

图示 11 illustrates 这 ad767 接口 至 一个 tms320c25

数字的 信号 处理器. 预定的 至 这 高-速 能力 的 这

处理器 (40 mhz), 一个 单独的 wait 状态 是 必需的 和 是 容易地

发生 使用 msc. 一个 20 mhz tms320c25 不管怎样, 做

不 需要 wait states 和 应当 是 连接 使用 这 电路

显示 在 图示 9.

图示 11. tms320c25 – ad767 接口

外形 维度

维度 显示 在 英寸 和 (mm).

24-管脚 陶瓷的 (后缀 d)

24-管脚 塑料 (后缀 n)

28-管脚 plcc (后缀 p)