参数 度量 信息

(持续)

典型 应用

产品 信息

一般 应用 指导原则 和 hints 为 LVDS 驱动器

和 接受者 将 是 建立 在 这 下列的 应用

注释: LVDS Owner’s 手工的 (lit #550062-001), an808,

an977, an971, an916, an805, an903.

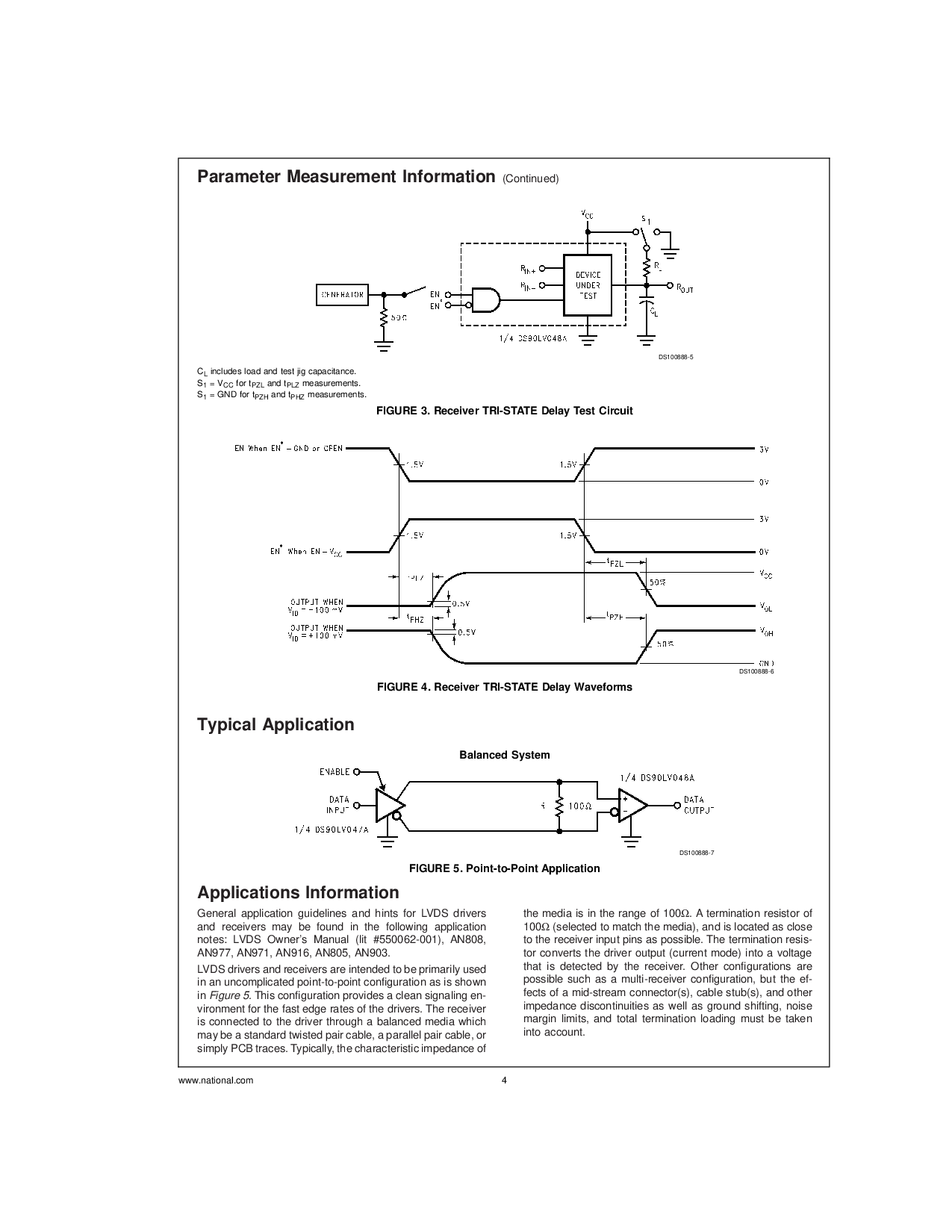

LVDS 驱动器 和 接受者 是 将 至 是 primarily 使用

在 一个 uncomplicated 要点-至-要点 配置 作 是 显示

在

图示 5

. 这个 配置 提供 一个 clean signaling en-

vironment 为 这 快 边缘 比率 的 这 驱动器. 这 接受者

是 连接 至 这 驱动器 通过 一个 保持平衡 媒介 这个

将 是 一个 标准 twisted 一双 缆索, 一个 并行的 一双 缆索, 或者

simply PCB 查出. 典型地, 这 典型的 阻抗 的

这 媒介 是 在 这 范围 的 100

Ω

. 一个 末端 电阻 的

100

Ω

(选择 至 相一致 这 媒介), 和 是 located 作 关闭

至 这 接受者 输入 管脚 作 可能. 这 末端 resis-

tor converts 这 驱动器 输出 (电流 模式) 在 一个 电压

那 是 发现 用 这 接受者. 其它 配置 是

可能 此类 作 一个 multi-接受者 配置, 但是 这 ef-

fects 的 一个 mid-stream 连接器(s), 缆索 stub(s), 和 其它

阻抗 discontinuities 作 好 作 地面 shifting, 噪音

余裕 限制, 和 总的 末端 加载 必须 是 带去

在 账户.

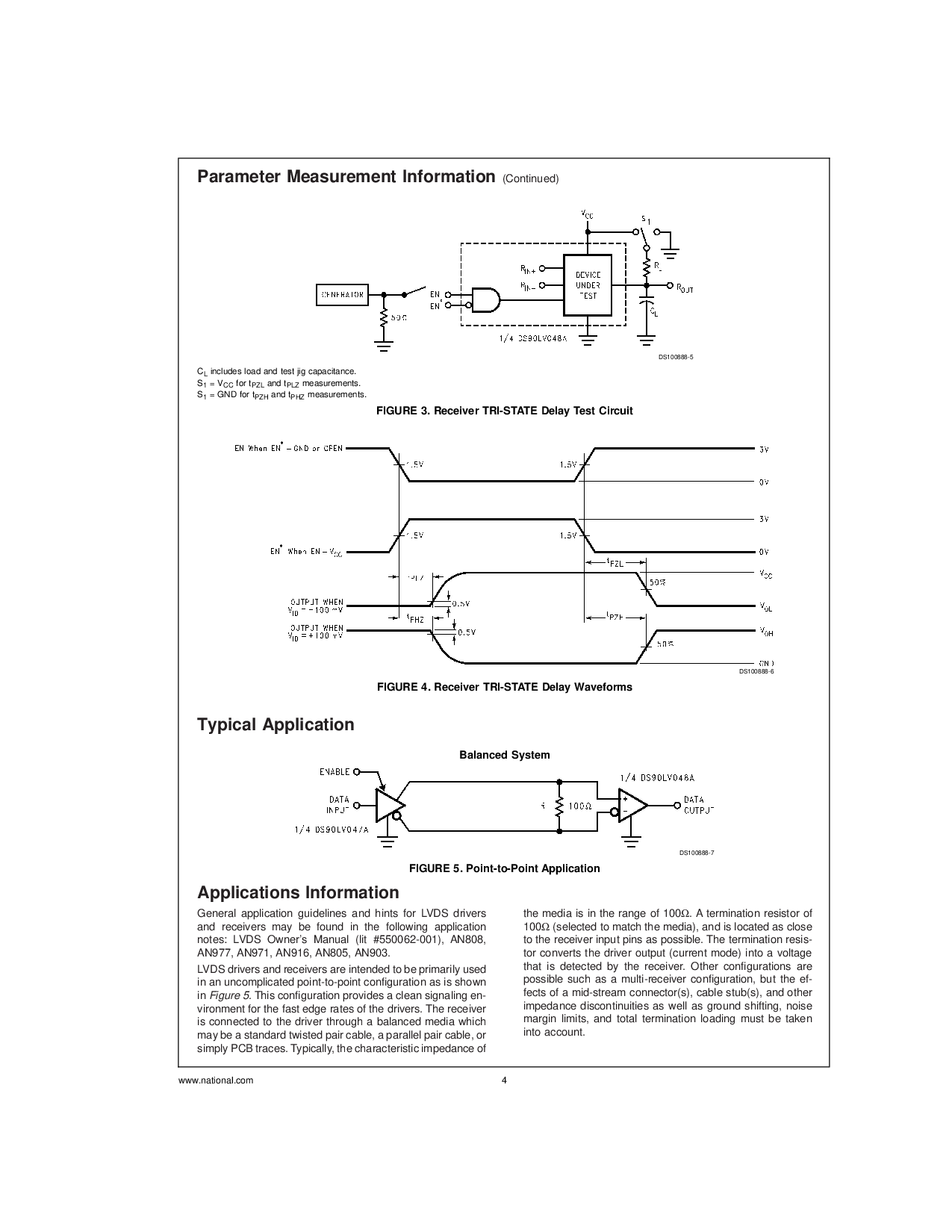

ds100888-5

C

L

包含 加载 和 测试 jig 电容.

S

1

=V

CC

为 t

PZL

和 t

PLZ

度量.

S

1

= 地 为 t

PZH

和 t

PHZ

度量.

图示 3. 接受者 触发-状态 延迟 测试 电路

ds100888-6

图示 4. 接受者 触发-状态 延迟 波形

保持平衡 系统

ds100888-7

图示 5. 要点-至-要点 应用

www.国家的.com 4