4

商业的 和 工业的

温度 范围

idt72v223/233/243/253/263/273/283/293 3.3v 高 密度 supersync ii

TM

narrow 总线 先进先出

512 x 18, 1k x 9/18, 2k x 9/18, 4k x 9/18, 8k x 9/18, 16k x 9/18, 32k x 9/18, 64k x 9/18, 128k x 9

不 有 至 是 asserted 为 accessing 这 第一 文字. 不管怎样, subsequent

words 写 至 这 先进先出 做 需要 一个 低 在

REN

为 进入. 这 状态 的

这 fwft/si 输入 在 主控 重置 确定 这 定时 模式 在 使用.

为 产品 需要 更多 数据 存储 capacity 比 一个 单独的 先进先出

能 提供, 这 fwft 定时 模式 准许 depth expansion 用 chaining fifos

在 序列 (i.e. 这 数据 输出 的 一个 先进先出 是 连接 至 这 相应的

数据 输入 的 这 next). 非 外部 逻辑 是 必需的.

这些 fifos 有 five 标记 管脚,

EF

/

或者

(empty 标记 或者 输出 准备好),

FF

/

IR

(全部 标记 或者 输入 准备好),

HF

(half-全部 标记),

PAE

(可编程序的

almost-empty 标记) 和

PAF

(可编程序的 almost-全部 标记). 这

EF

和

FF

功能 是 选择 在 idt 标准 模式. 这

IR

和

或者

功能 是

选择 在 fwft 模式.

HF

,

PAE

和

PAF

是 总是 有 为 使用,

irrespective 的 定时 模式.

PAE

和

PAF

能 是 编写程序 independently 至 转变 在 任何 要点 在

记忆. 可编程序的 补偿 决定 这 标记 切换 门槛 和 能

是 承载 用 二 方法: 并行的 或者 串行. 第八 default 补偿 settings 是 也

提供, 所以 那

PAE

能 是 设置 至 转变 在 一个 predefined 号码 的 locations

从 这 empty boundary 和 这

PAF

门槛 能 也 是 设置 在 类似的

predefined 值 从 这 全部 boundary. 这 default 补偿 值 是 设置 在

主控 重置 用 这 状态 的 这 fsel0, fsel1, 和

LD

管脚.

为 串行 程序编制,

SEN

一起 和

LD

在 各自 rising 边缘 的 wclk,

是 使用 至 加载 这 补偿 寄存器 通过 这 串行 输入 (si). 为 并行的

程序编制,

WEN

一起 和

LD

在 各自 rising 边缘 的 wclk, 是 使用

至 加载 这 补偿 寄存器 通过 d

n

.

REN

一起 和

LD

在 各自 rising 边缘

的 rclk 能 是 使用 至 读 这 补偿 在 并行的 从 q

n

regardless 的 whether

串行 或者 并行的 补偿 加载 有 被 选择.

在 主控 重置 (

MRS

) 这 下列的 events 出现: 这 读 和

写 pointers 是 设置 至 这 第一 location 的 这 先进先出. 这 fwft 管脚 选择

idt 标准 模式 或者 fwft 模式.

这 partial 重置 (

PRS

) 也 sets 这 读 和 写 pointers 至 这 第一

location 的 这 记忆. 不管怎样, 这 定时 模式, 可编程序的 标记

程序编制 方法, 和 default 或者 编写程序 补偿 settings 存在

在之前 partial 重置 仍然是 不变. 这 flags 是 updated 符合 至 这

定时 模式 和 补偿 在 效应.

PRS

是 有用的 为 resetting 一个 设备 在 mid-

运作, 当 reprogramming 可编程序的 flags 将 是 不想要的.

它 是 也 可能 至 选择 这 定时 模式 的 这

PAE

(可编程序的 almost-

empty 标记) 和

PAF

(可编程序的 almost-全部 标记) 输出. 这 定时

模式 能 是 设置 至 是 也 异步的 或者 同步的 为 这

PAE

和

PAF

flags.

如果 异步的

PAE

/

PAF

配置 是 选择, 这

PAE

是 asserted

低 在 这 低-至-高 转变 的 rclk.

PAE

是 重置 至 高 在 这 低-

描述 (持续)

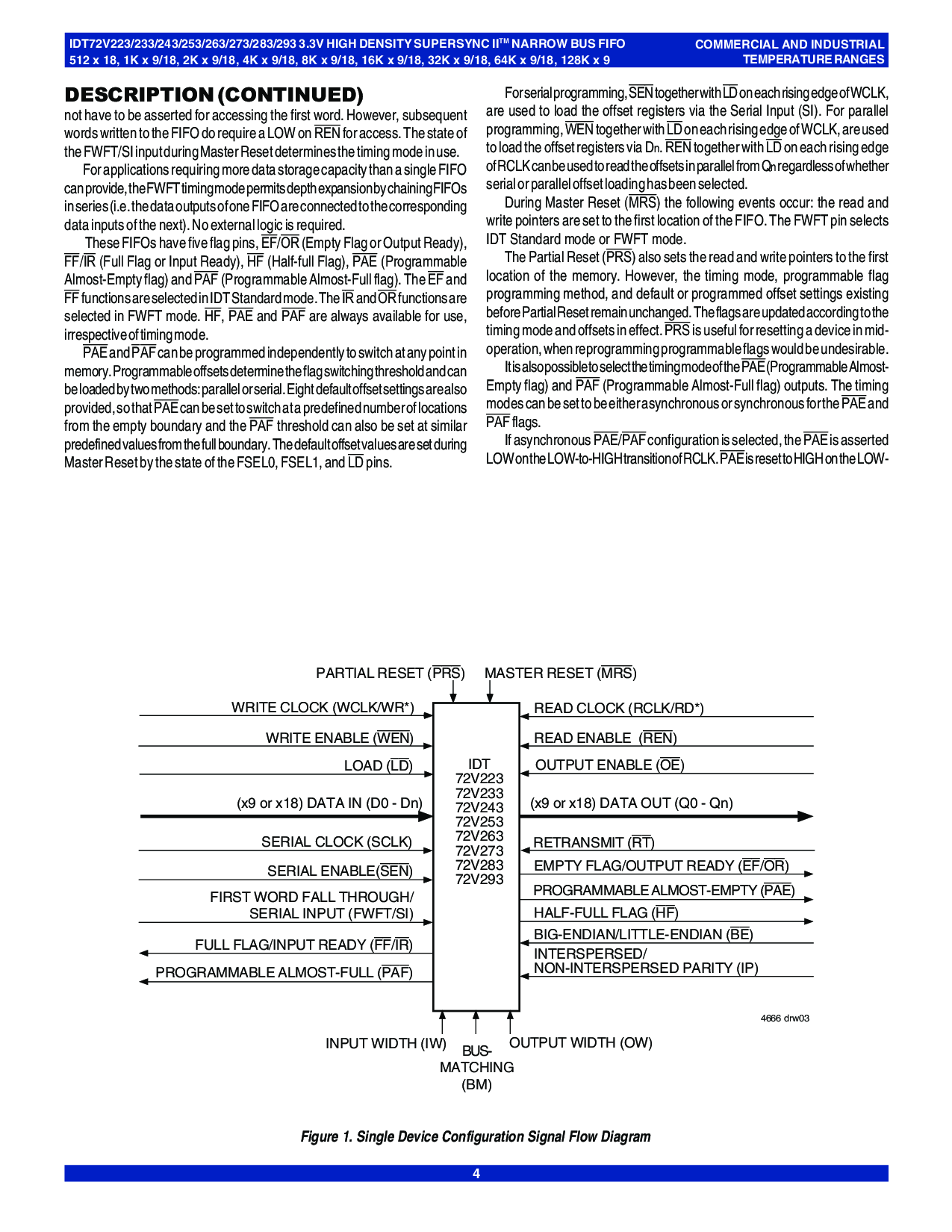

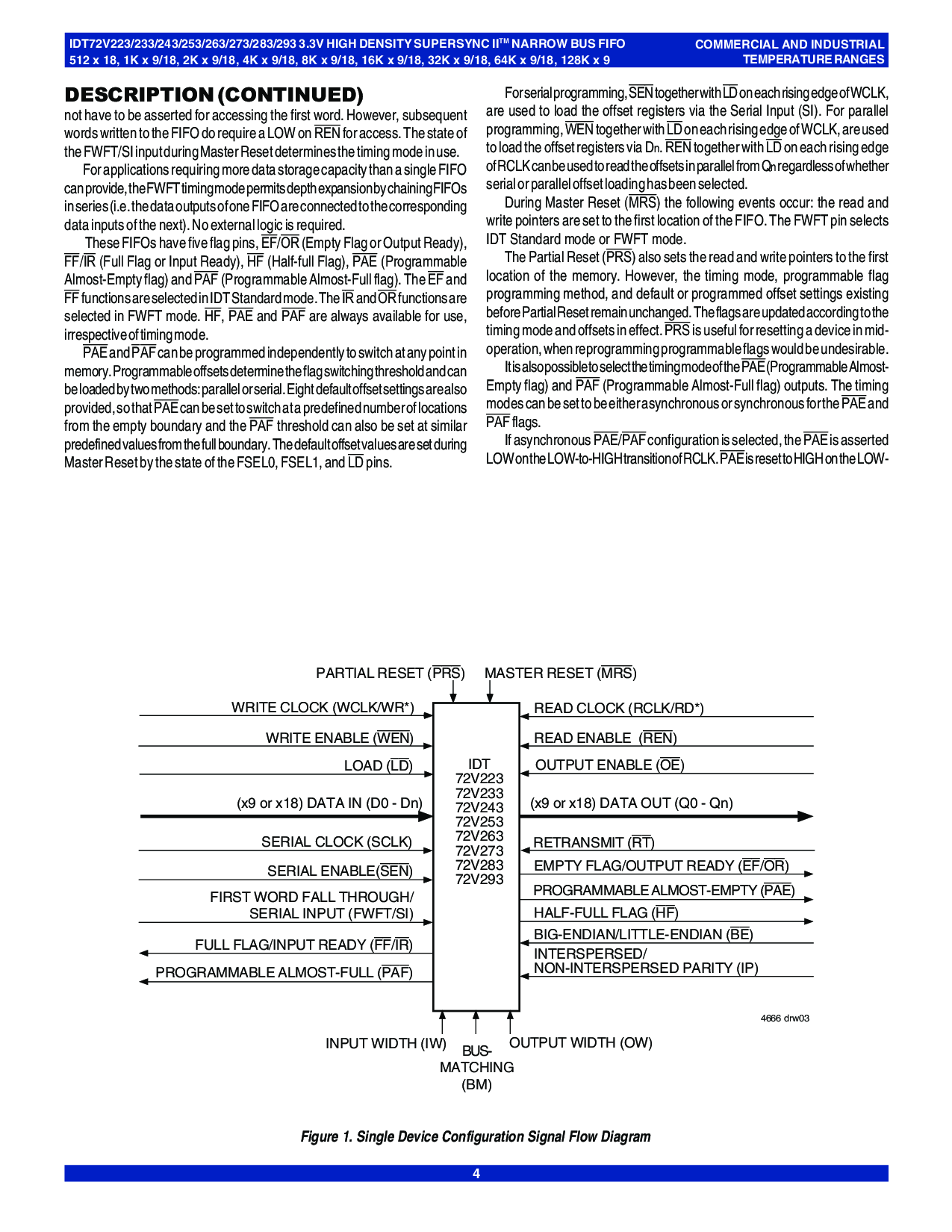

主控 重置 (

MRS

)

读 时钟 (rclk/rd*)

读 使能 (

REN

)

输出 使能 (

OE

)

empty 标记/输出 准备好 (

EF

/

或者

)

可编程序的 almost-empty (

PAE

)

写 时钟 (wclk/wr*)

写 使能 (

WEN

)

加载 (

LD

)

全部 标记/输入 准备好 (

FF

/

IR

)

可编程序的 almost-全部 (

PAF

)

partial 重置 (

PRS

)

第一 文字 下降 通过/

串行 输入 (fwft/si)

retransmit (

RT

)

4666 drw03

half-全部 标记 (

HF

)

串行 使能(

SEN

)

输入 宽度 (iw)

输出 宽度 (ow)

big-endian/little-endian (

是

)

interspersed/

非-interspersed parity (ip)

总线-

相一致

(bm)

串行 时钟 (sclk)

(x9 或者 x18) 数据 输出 (q0 - qn)(x9 或者 x18) 数据 在 (d0 - dn)

IDT

72V223

72V233

72V243

72V253

72V263

72V273

72V283

72V293

图示 1. 单独的 设备 配置 信号 流动 图解