1998 Apr 09 6

飞利浦 半导体 产品 规格

多媒体 桥, 高 效能

scaler 和 pci 电路 (spci)

SAA7146A

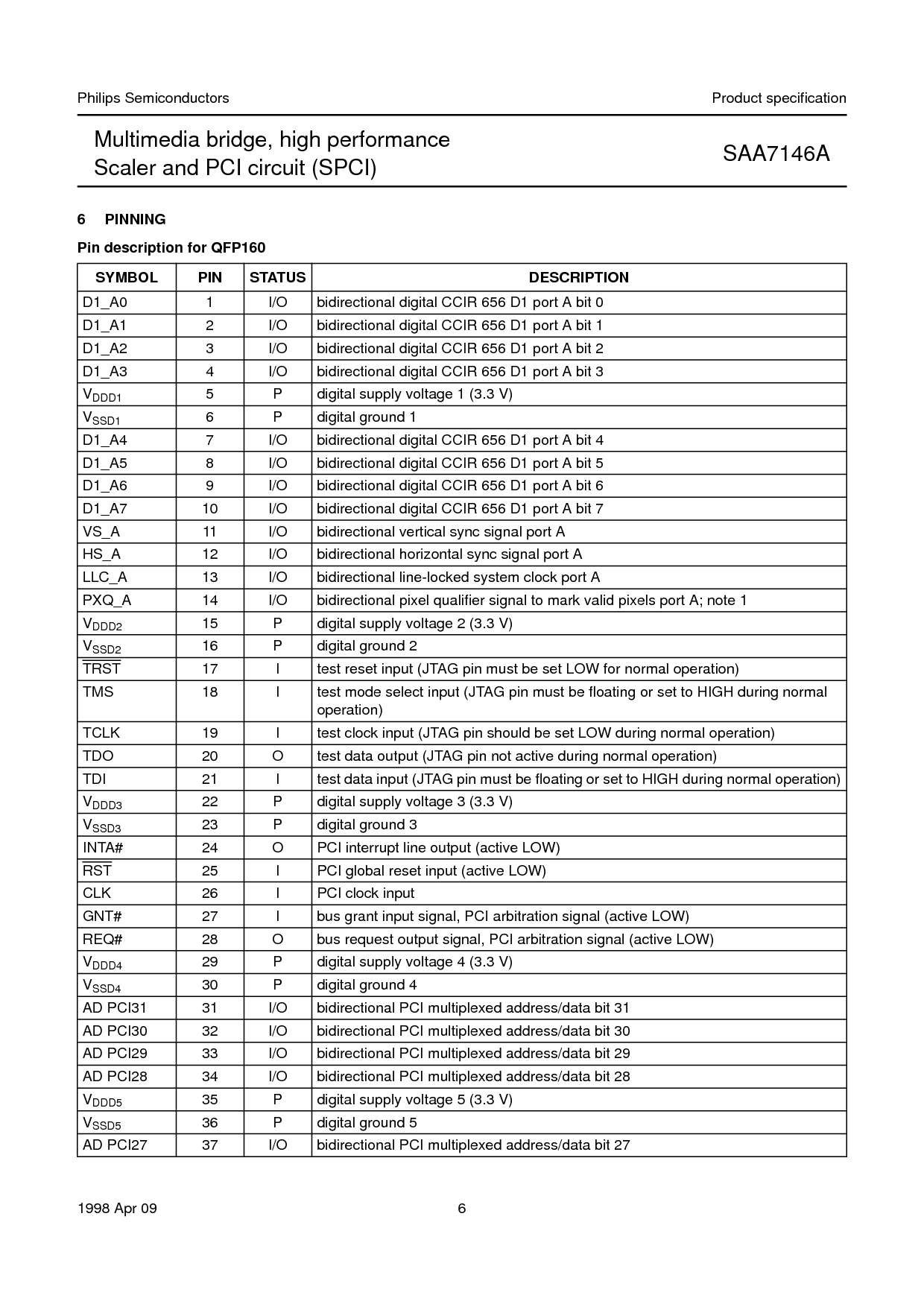

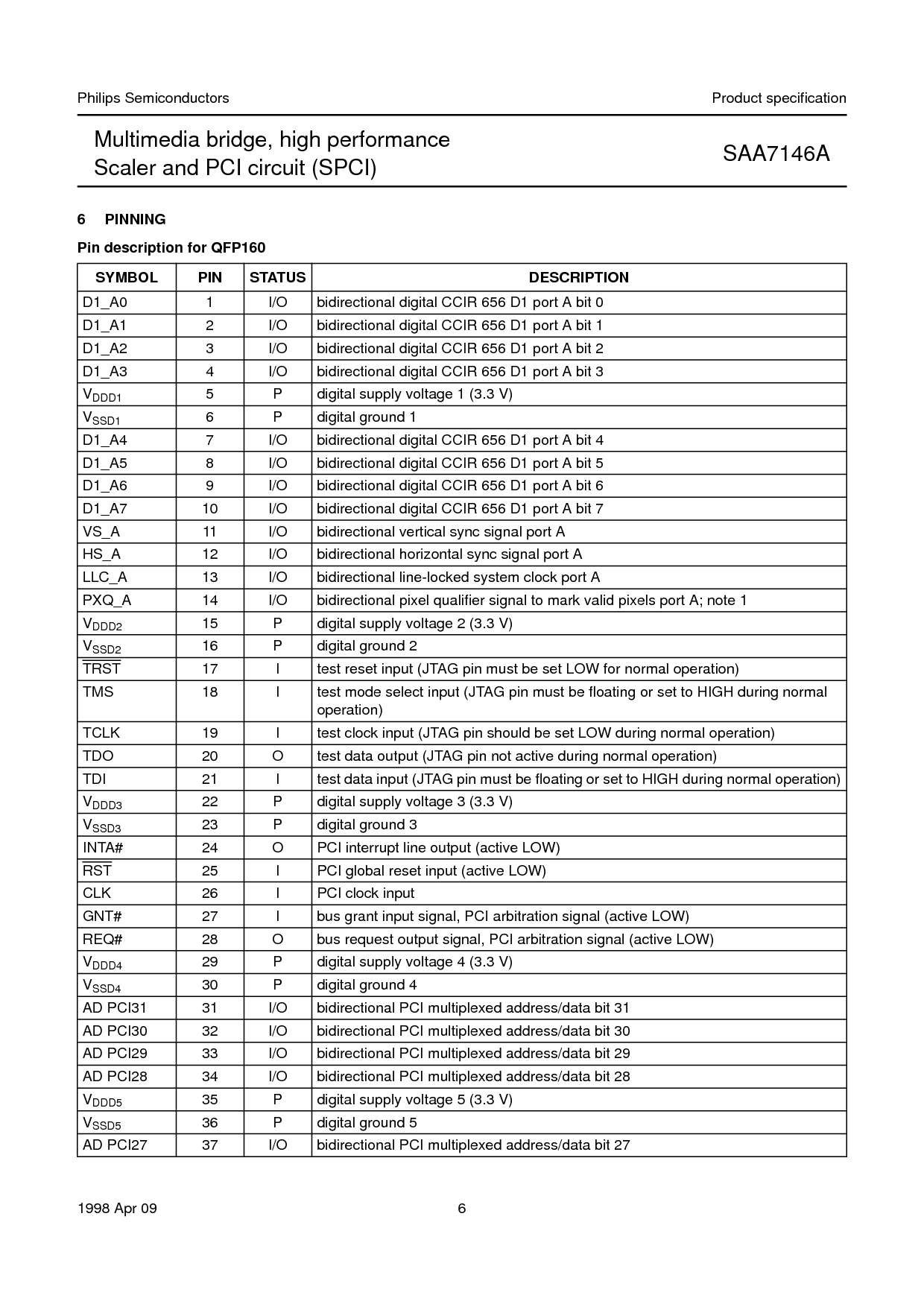

6 固定

管脚 描述 为 qfp160

标识 管脚 状态 描述

d1_a0 1 i/o 双向的 数字的 ccir 656 d1 端口 一个 位 0

d1_a1 2 i/o 双向的 数字的 ccir 656 d1 端口 一个 位 1

d1_a2 3 i/o 双向的 数字的 ccir 656 d1 端口 一个 位 2

d1_a3 4 i/o 双向的 数字的 ccir 656 d1 端口 一个 位 3

V

DDD1

5 P 数字的 供应 电压 1 (3.3 v)

V

SSD1

6 P 数字的 地面 1

d1_a4 7 i/o 双向的 数字的 ccir 656 d1 端口 一个 位 4

d1_a5 8 i/o 双向的 数字的 ccir 656 d1 端口 一个 位 5

d1_a6 9 i/o 双向的 数字的 ccir 656 d1 端口 一个 位 6

d1_a7 10 i/o 双向的 数字的 ccir 656 d1 端口 一个 位 7

vs_一个 11 i/o 双向的 vertical 同步 信号 端口 一个

hs_一个 12 i/o 双向的 horizontal 同步 信号 端口 一个

llc_一个 13 i/o 双向的 线条-锁 系统 时钟 端口 一个

pxq_一个 14 i/o 双向的 pixel qualifier 信号 至 mark 有效的 pixels 端口 一个; 便条 1

V

DDD2

15 P 数字的 供应 电压 2 (3.3 v)

V

SSD2

16 P 数字的 地面 2

TRST 17 I 测试 重置 输入 (jtag 管脚 必须 是 设置 低 为 正常的 运作)

TMS 18 I 测试 模式 选择 输入 (jtag 管脚 必须 是 floating 或者 设置 至 高 在 正常的

运作)

TCLK 19 I 测试 时钟 输入 (jtag 管脚 应当 是 设置 低 在 正常的 运作)

TDO 20 O 测试 数据 输出 (jtag 管脚 不 起作用的 在 正常的 运作)

TDI 21 I 测试 数据 输入 (jtag 管脚 必须 是 floating 或者 设置 至 高 在 正常的 运作)

V

DDD3

22 P 数字的 供应 电压 3 (3.3 v)

V

SSD3

23 P 数字的 地面 3

INTA# 24 O pci 中断 线条 输出 (起作用的 低)

RST 25 I pci global 重置 输入 (起作用的 低)

CLK 26 I pci 时钟 输入

GNT# 27 I 总线 grant 输入 信号, pci arbitration 信号 (起作用的 低)

REQ# 28 O 总线 要求 输出 信号, pci arbitration 信号 (起作用的 低)

V

DDD4

29 P 数字的 供应 电压 4 (3.3 v)

V

SSD4

30 P 数字的 地面 4

ad pci31 31 i/o 双向的 pci 多路复用 地址/数据 位 31

ad pci30 32 i/o 双向的 pci 多路复用 地址/数据 位 30

ad pci29 33 i/o 双向的 pci 多路复用 地址/数据 位 29

ad pci28 34 i/o 双向的 pci 多路复用 地址/数据 位 28

V

DDD5

35 P 数字的 供应 电压 5 (3.3 v)

V

SSD5

36 P 数字的 地面 5

ad pci27 37 i/o 双向的 pci 多路复用 地址/数据 位 27