idt54/74fct388915t 70/100/133/150

3.3v 低 skew pll-为基础 cmos 时钟 驱动器 军队 和 商业的 温度 范围

9.8 8

这 频率 relationship 显示 here 是 适用 至 所有 q

输出 (q0, q1, q2, q3 和 q4).

1:2 输入 至 "q" 输出 频率 relation-

SHIP

在 这个 应用, 这 q/2 输出 是 连接 至 这

反馈 输入. 这 内部的 pll 将 线条 向上 这 积极的

edges 的 q/2 和 同步, 因此 这 q/2 频率 将 equal 这

同步 频率. 这 q 输出 (q0-q4,

Q5

) 将 总是 run

在 2x 这 q/2 频率, 和 这 2q 输出 将 run 在 4x 这

q/2 频率.

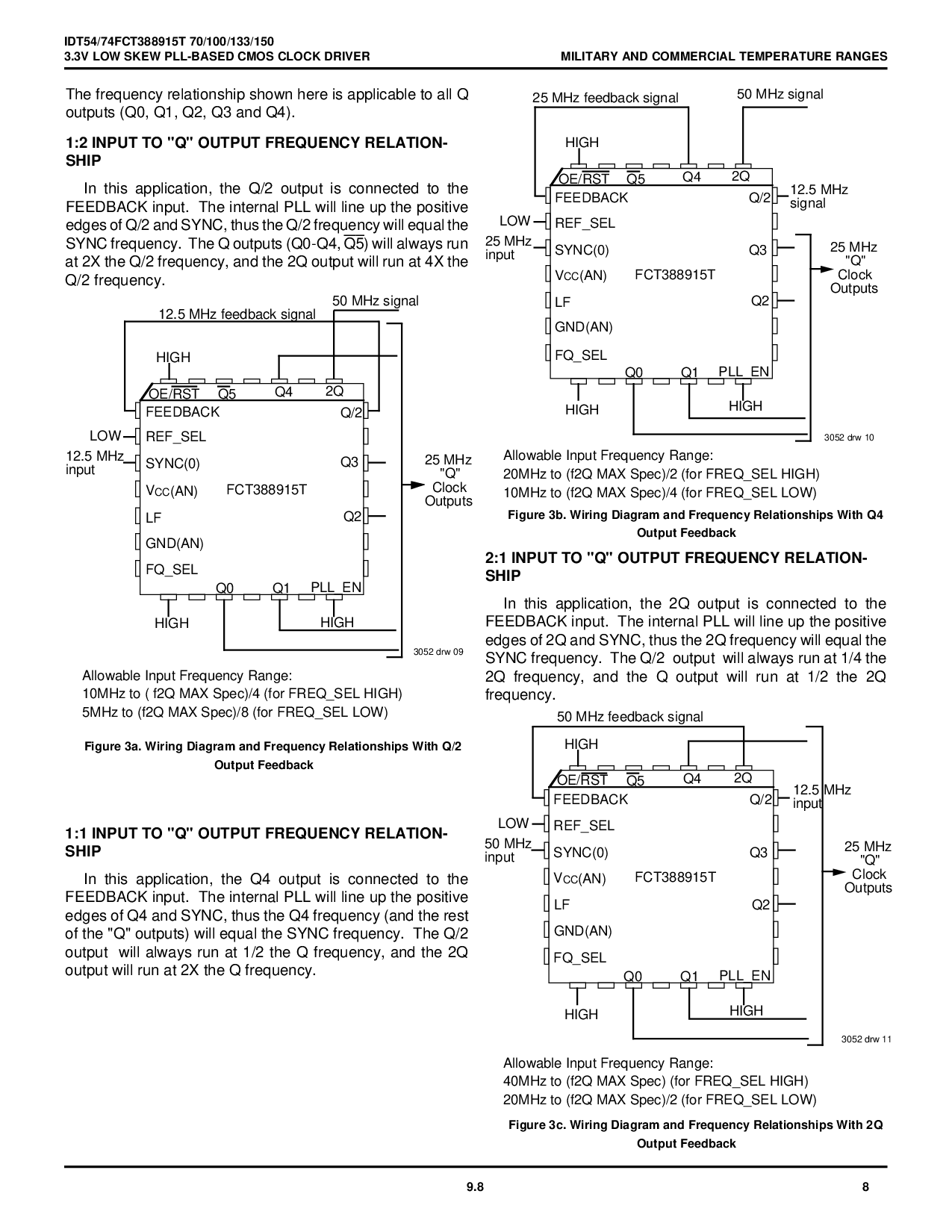

1:1 输入 至 "q" 输出 频率 relation-

SHIP

在 这个 应用, 这 q4 输出 是 连接 至 这

反馈 输入. 这 内部的 pll 将 线条 向上 这 积极的

edges 的 q4 和 同步, 因此 这 q4 频率 (和 这 rest

的 这 "q" 输出) 将 equal 这 同步 频率. 这 q/2

输出 将 总是 run 在 1/2 这 q 频率, 和 这 2q

输出 将 run 在 2x 这 q 频率.

q/2

Q3

Q2

pll_en

Q1Q0

fq_sel

反馈

ref_sel

同步(0)

V

CC

(一个)

LF

地(一个)

Q4

Q5

2Q

FCT388915T

低

50 mhz 信号

25 mhz 反馈 信号

高

高

高

25 mhz

"q"

时钟

输出

25 mhz

输入

12.5 mhz

信号

oe/rst

3052 drw 10

容许的 输入 频率 范围:

40mhz 至 (f2q 最大值 规格) (为 freq_sel high)

20mhz 至 (f2q 最大值 规格)/2 (为 freq_sel low)

容许的 输入 频率 范围:

20mhz 至 (f2q 最大值 规格)/2 (为 freq_sel high)

10mhz 至 (f2q 最大值 规格)/4 (为 freq_sel low)

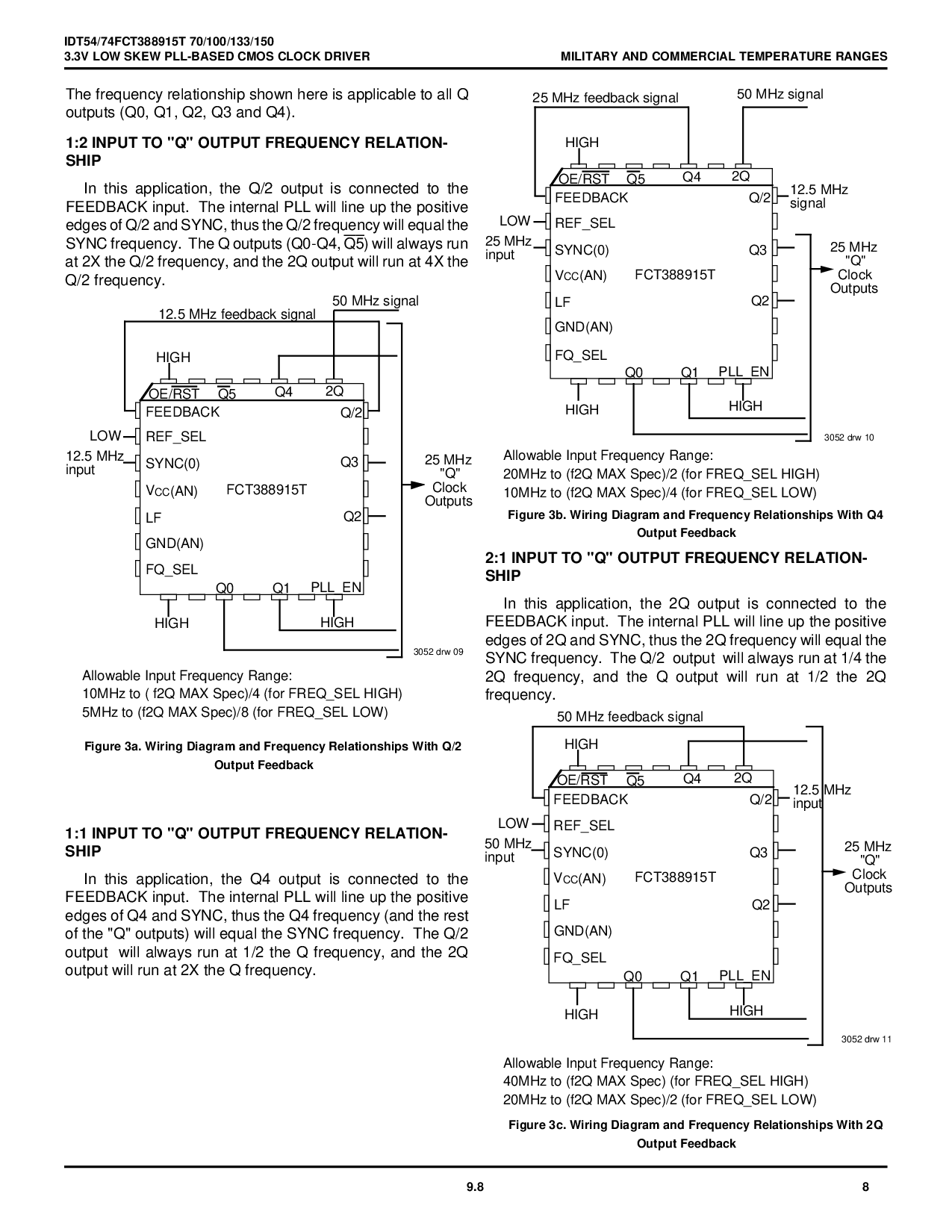

2:1 输入 至 "q" 输出 频率 relation-

SHIP

在 这个 应用, 这 2q 输出 是 连接 至 这

反馈 输入. 这 内部的 pll 将 线条 向上 这 积极的

edges 的 2q 和 同步, 因此 这 2q 频率 将 equal 这

同步 频率. 这 q/2 输出 将 总是 run 在 1/4 这

2q 频率, 和 这 q 输出 将 run 在 1/2 这 2q

频率.

q/2

Q3

Q2

pll_en

Q1Q0

fq_sel

反馈

ref_sel

同步(0)

V

CC

(一个)

LF

地(一个)

Q4

Q5

2Q

FCT388915T

低

50 mhz 反馈 信号

高

高

高

25 mhz

"q"

时钟

输出

50 mhz

输入

12.5 mhz

输入

oe/rst

3052 drw 11

图示 3a. 线路 图解 和 频率 relationships 和 q/2

输出 反馈

图示 3c. 线路 图解 和 频率 relationships 和 2q

输出 反馈

图示 3b. 线路 图解 和 频率 relationships 和 q4

输出 反馈

q/2

Q3

Q2

pll_en

Q1Q0

fq_sel

反馈

ref_sel

同步(0)

V

CC

(一个)

LF

地(一个)

Q4

Q5

2Q

FCT388915T

低

50 mhz 信号

12.5 mhz 反馈 信号

高

高

高

25 mhz

"q"

时钟

输出

12.5 mhz

输入

oe/rst

3052 drw 09

容许的 输入 频率 范围:

10mhz 至 ( f2q 最大值 规格)/4 (为 freq_sel 高)

5mhz 至 (f2q 最大值 规格)/8 (为 freq_sel low)