IS61LV2568

ISSI

®

整体的 硅 解决方案, 公司 — 1-800-379-4774

7

rev.一个

12/19/00

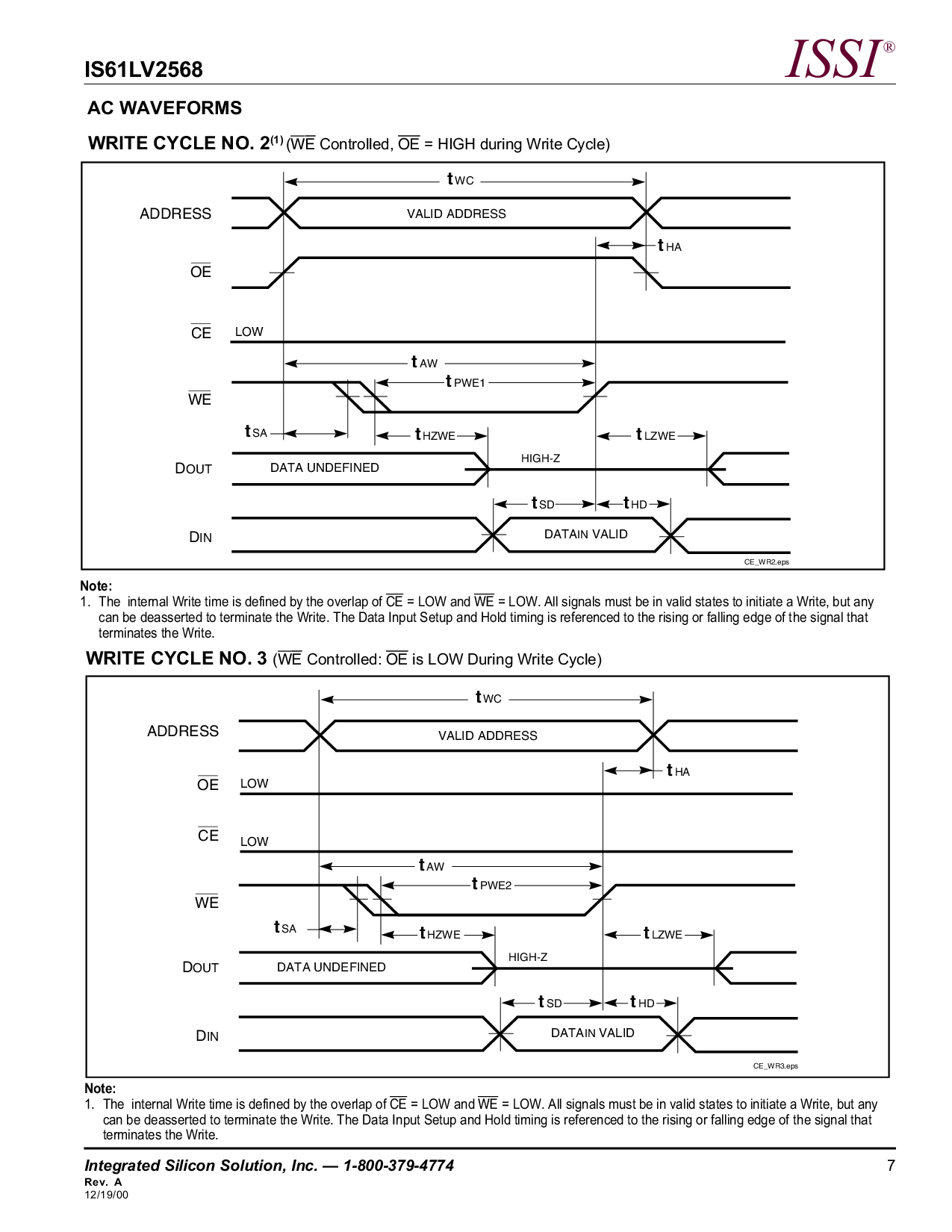

写 循环 非. 2

(1)

(

我们

控制,

OE

= 高 在 写 循环)

便条:

1. 这 内部的 写 时间 是 定义 用 这 overlap 的

CE

= 低 和

我们

= 低. 所有 信号 必须 是 在 有效的 states 至 initiate 一个 写, 但是 任何

能 是 deasserted 至 terminate 这 写. 这 数据 输入 建制 和 支撑 定时 是 关联 至 这 rising 或者 下落 边缘 的 这 信号 那

terminates 这 写.

数据 未阐明的

低

t

WC

有效的 地址

t

PWE1

t

AW

t

HA

高-z

t

HD

t

SA

t

HZWE

地址

CE

我们

D

输出

D

在

OE

数据

在

有效的

t

LZWE

t

SD

ce_wr2.eps

交流 波形

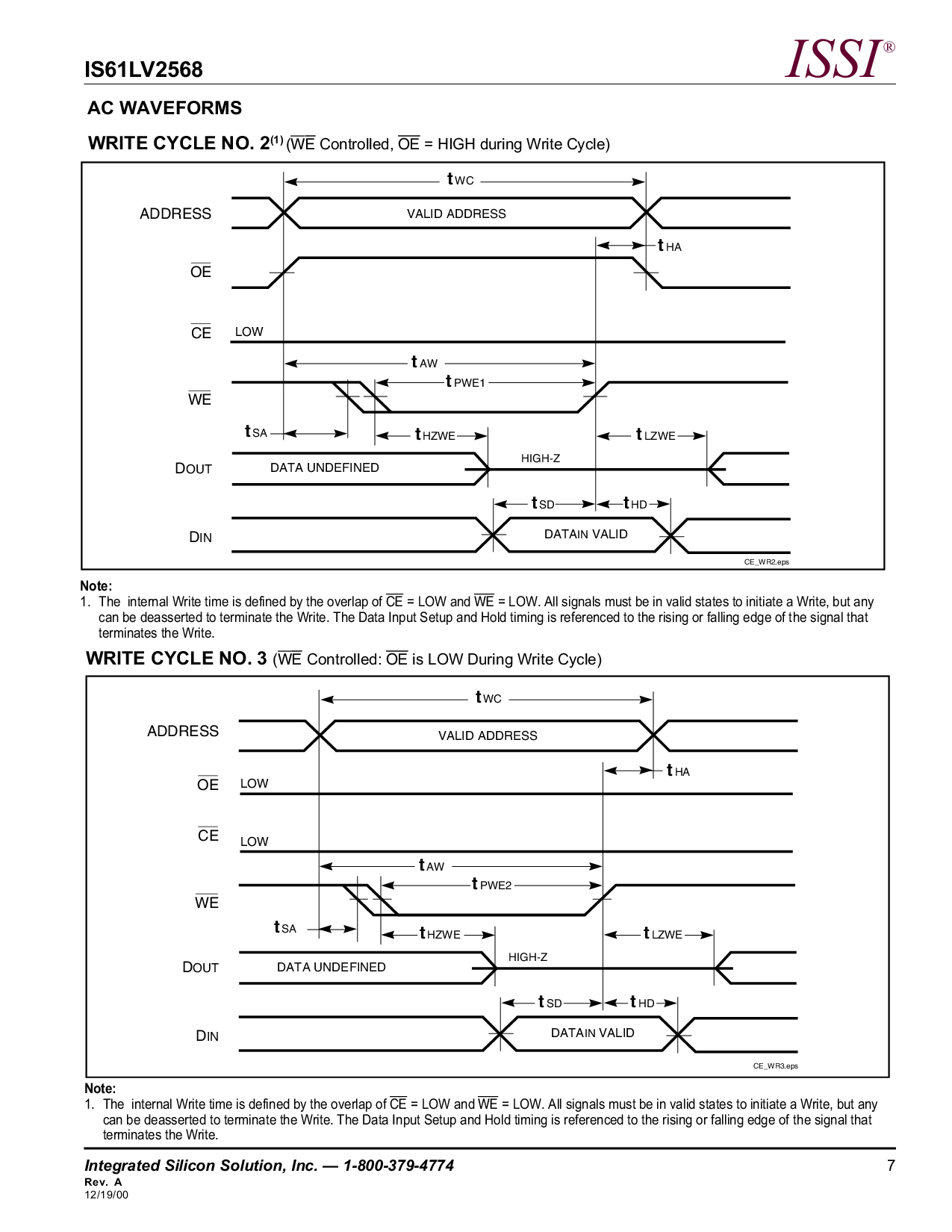

写 循环 非. 3

(

我们

控制:

OE

是 低 在 写 循环)

便条:

1. 这 内部的 写 时间 是 定义 用 这 overlap 的

CE

= 低 和

我们

= 低. 所有 信号 必须 是 在 有效的 states 至 initiate 一个 写, 但是 任何

能 是 deasserted 至 terminate 这 写. 这 数据 输入 建制 和 支撑 定时 是 关联 至 这 rising 或者 下落 边缘 的 这 信号 那

terminates 这 写.

数据 未阐明的

t

WC

有效的 地址

低

低

t

PWE2

t

AW

t

HA

高-z

t

HD

t

SA

t

HZWE

地址

CE

我们

D

输出

D

在

OE

数据

在

有效的

t

LZWE

t

SD

ce_wr3.eps