9397 750 14985 © koninklijke 飞利浦 electronics n.v. 2005. 所有 权利 保留.

初步的 数据 薄板 rev. 01 — 3 october 2005 10 的 38

飞利浦 半导体

lpc2141/42/44/46/48

单独的-碎片 16-位/32-位 微控制器

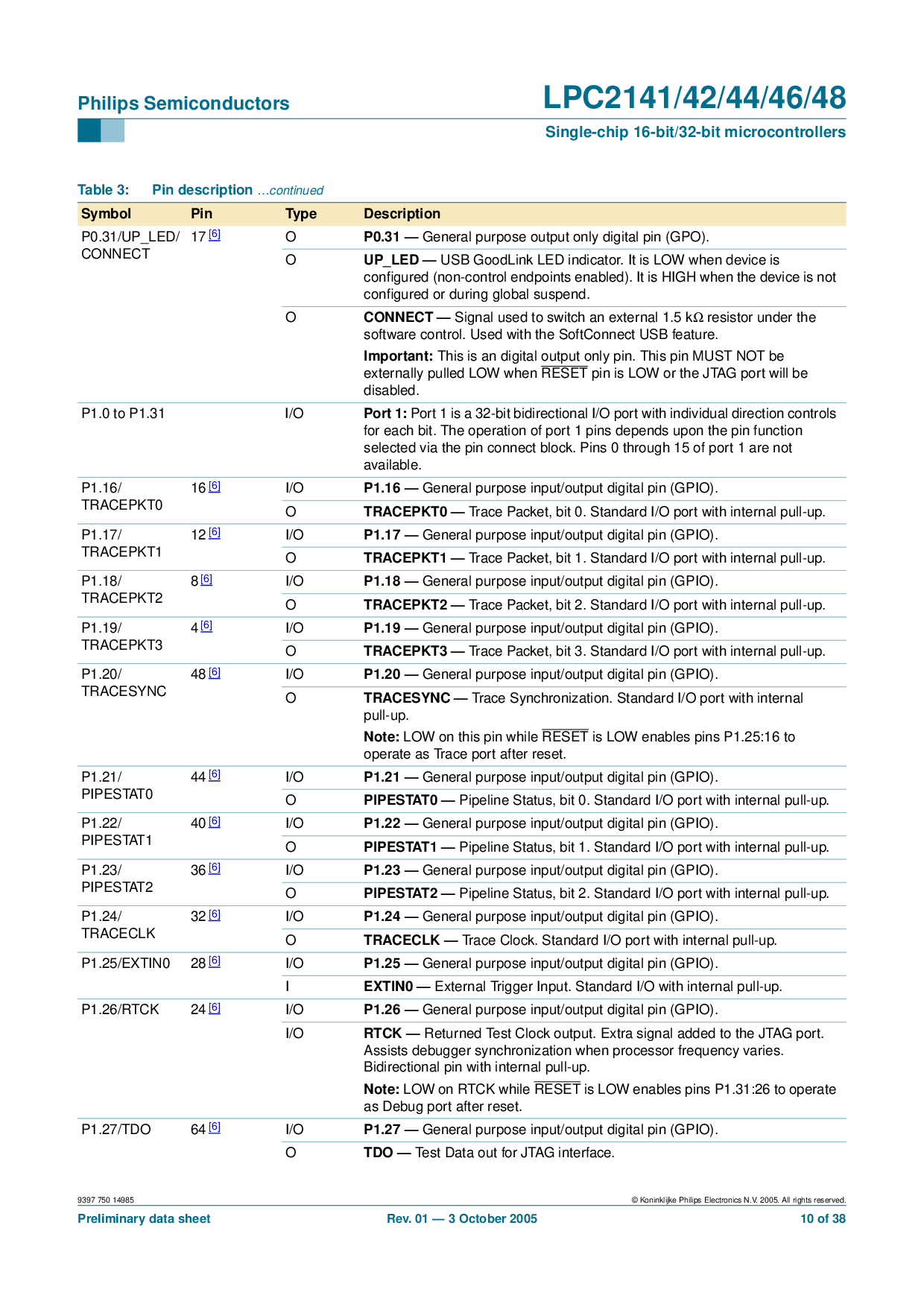

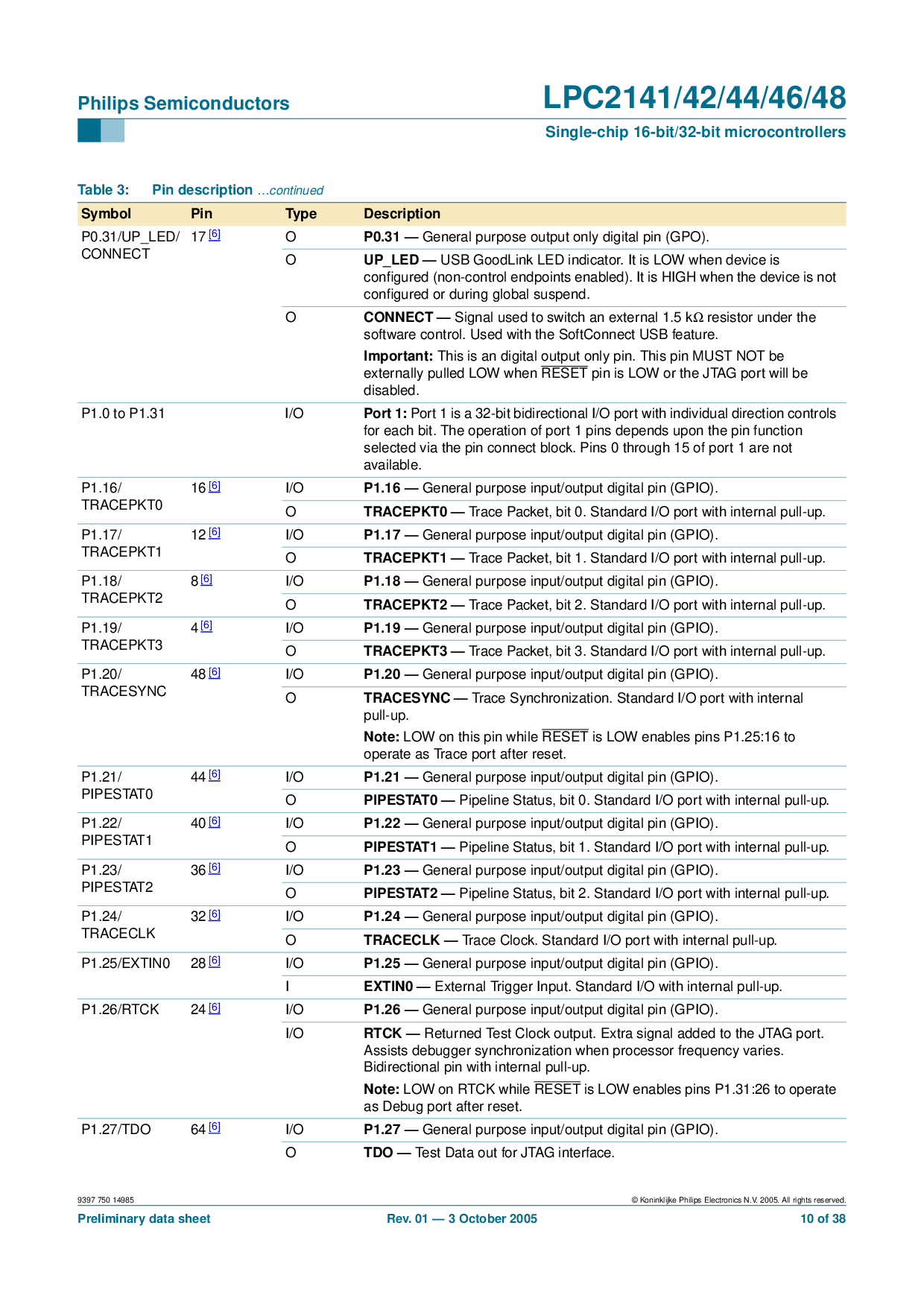

p0.31/向上_led/

连接

17

[6]

O

p0.31 —

一般 目的 输出 仅有的 数字的 管脚 (gpo).

O

向上_led —

usb goodlink led 指示信号. 它 是 低 当 设备 是

configured (非-控制 endpoints 使能). 它 是 高 当 这 设备 是 不

configured 或者 在 global suspend.

O

连接 —

信号 使用 至 转变 一个 外部 1.5 k

Ω

电阻 下面 这

软件 控制. 使用 和 这 softconnect usb 特性.

重要的:

这个 是 一个 数字的 输出 仅有的 管脚. 这个 管脚 必须 不 是

externally 牵引的 低 当

重置 管脚 是 低 或者 这 jtag 端口 将 是

无能.

p1.0 至 p1.31 i/o

Port 1:

端口 1 是 一个 32-位 双向的 i/o 端口 和 单独的 方向 控制

为 各自 位. 这 运作 的 端口 1 管脚 取决于 在之上 这 管脚 函数

选择 通过 这 管脚 连接 块. 管脚 0 通过 15 的 端口 1 是 不

有.

p1.16/

TRACEPKT0

16

[6]

i/o

p1.16 —

一般 目的 输入/输出 数字的 管脚 (gpio).

O

tracepkt0 —

查出 小包装板盒, 位 0. 标准 i/o 端口 和 内部的 拉-向上.

p1.17/

TRACEPKT1

12

[6]

i/o

p1.17 —

一般 目的 输入/输出 数字的 管脚 (gpio).

O

tracepkt1 —

查出 小包装板盒, 位 1. 标准 i/o 端口 和 内部的 拉-向上.

p1.18/

TRACEPKT2

8

[6]

i/o

p1.18 —

一般 目的 输入/输出 数字的 管脚 (gpio).

O

tracepkt2 —

查出 小包装板盒, 位 2. 标准 i/o 端口 和 内部的 拉-向上.

p1.19/

TRACEPKT3

4

[6]

i/o

p1.19 —

一般 目的 输入/输出 数字的 管脚 (gpio).

O

tracepkt3 —

查出 小包装板盒, 位 3. 标准 i/o 端口 和 内部的 拉-向上.

p1.20/

TRACESYNC

48

[6]

i/o

p1.20 —

一般 目的 输入/输出 数字的 管脚 (gpio).

O

tracesync —

查出 同步. 标准 i/o 端口 和 内部的

拉-向上.

便条:

低 在 这个 管脚 当

重置 是 低 使能 管脚 p1.25:16 至

运作 作 查出 端口 之后 重置.

p1.21/

PIPESTAT0

44

[6]

i/o

p1.21 —

一般 目的 输入/输出 数字的 管脚 (gpio).

O

pipestat0 —

pipeline 状态, 位 0. 标准 i/o 端口 和 内部的 拉-向上.

p1.22/

PIPESTAT1

40

[6]

i/o

p1.22 —

一般 目的 输入/输出 数字的 管脚 (gpio).

O

pipestat1 —

pipeline 状态, 位 1. 标准 i/o 端口 和 内部的 拉-向上.

p1.23/

PIPESTAT2

36

[6]

i/o

p1.23 —

一般 目的 输入/输出 数字的 管脚 (gpio).

O

pipestat2 —

pipeline 状态, 位 2. 标准 i/o 端口 和 内部的 拉-向上.

p1.24/

TRACECLK

32

[6]

i/o

p1.24 —

一般 目的 输入/输出 数字的 管脚 (gpio).

O

traceclk —

查出 时钟. 标准 i/o 端口 和 内部的 拉-向上.

p1.25/extin0 28

[6]

i/o

p1.25 —

一般 目的 输入/输出 数字的 管脚 (gpio).

I

extin0 —

外部 触发 输入. 标准 i/o 和 内部的 拉-向上.

p1.26/rtck 24

[6]

i/o

p1.26 —

一般 目的 输入/输出 数字的 管脚 (gpio).

i/o

rtck —

returned 测试 时钟 输出. extra 信号 增加 至 这 jtag 端口.

assists debugger 同步 当 处理器 频率 varies.

双向的 管脚 和 内部的 拉-向上.

便条:

低 在 RTCK 当

重置 是 低 使能 管脚 p1.31:26 至 运作

作 debug 端口 之后 重置.

p1.27/tdo 64

[6]

i/o

p1.27 —

一般 目的 输入/输出 数字的 管脚 (gpio).

O

tdo —

测试 数据 输出 为 jtag 接口.

表格 3: 管脚 描述

…continued

标识 管脚 类型 描述