3

ltc1709-8/ltc1709-9

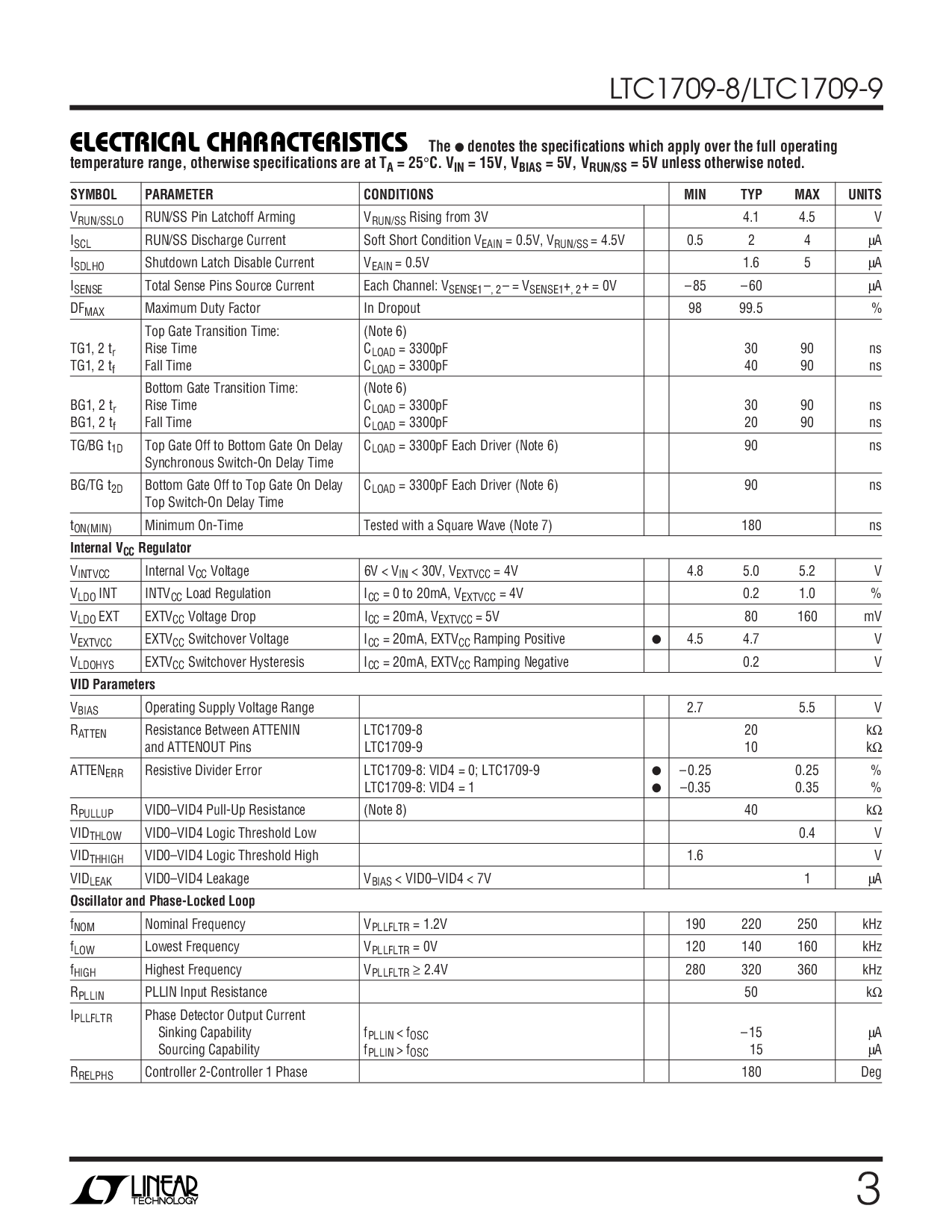

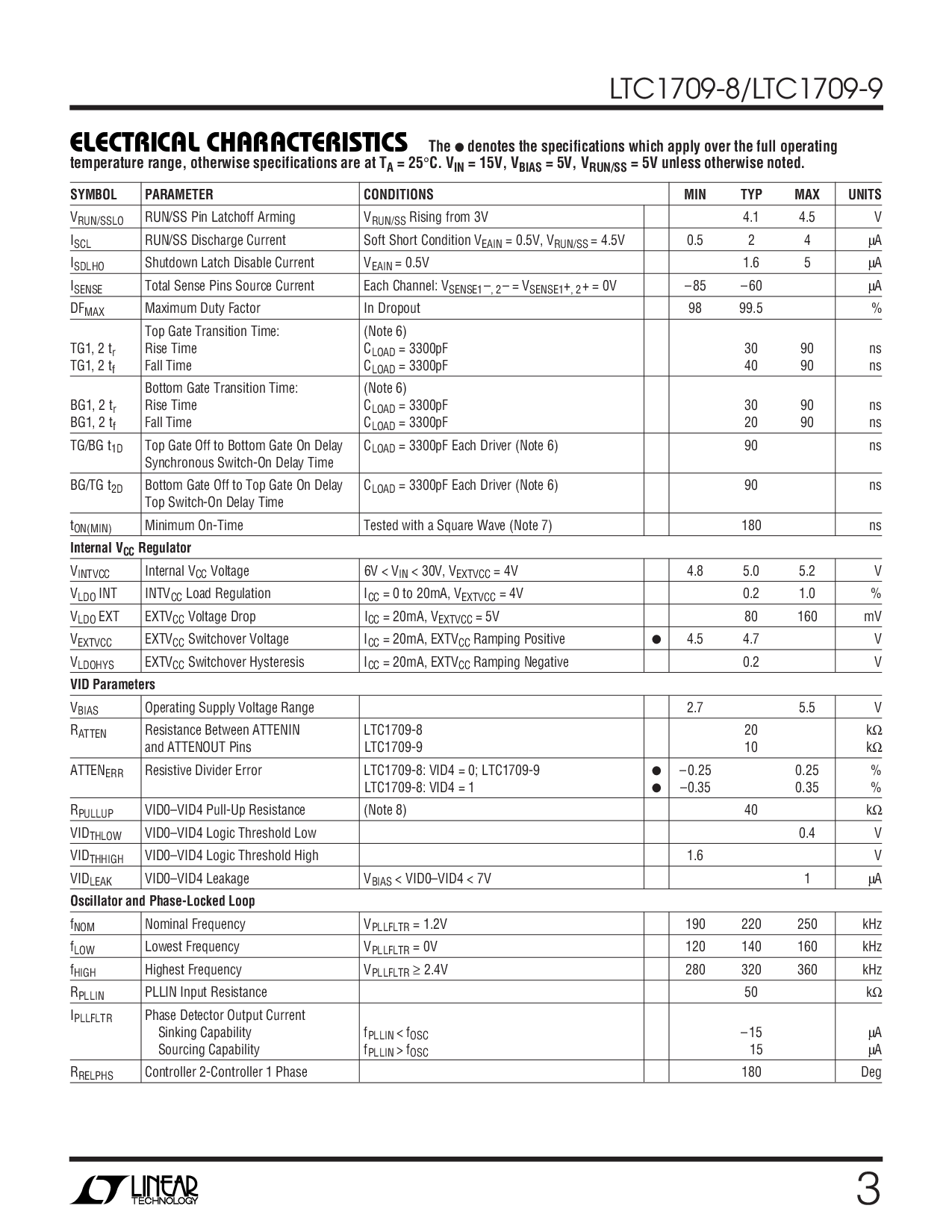

电的 特性

这

●

denotes 这 规格 这个 应用 在 这 全部 运行

温度 范围, 否则 规格 是 在 t

一个

= 25

°

c. v

在

= 15v, v

偏差

= 5v, v

run/ss

= 5v 除非 否则 指出.

标识 参数 情况 最小值 典型值 最大值 单位

V

run/sslo

run/ss 管脚 latchoff arming V

run/ss

rising 从 3v 4.1 4.5 V

I

SCL

run/ss 释放 电流 软 短的 情况 v

EAIN

= 0.5v, v

run/ss

= 4.5v 0.5 2 4

µ

一个

I

SDLHO

关闭 获得 使不能运转 电流 V

EAIN

= 0.5v 1.6 5

µ

一个

I

SENSE

总的 sense 管脚 源 电流 各自 频道: v

SENSE1

–

, 2

– = v

SENSE1

+

, 2

+ = 0v – 85 – 60

µ

一个

DF

最大值

最大 职责 因素 在 落后 98 99.5 %

顶 门 转变 时间: (便条 6)

tg1, 2 t

r

上升 时间 C

加载

= 3300pf 30 90 ns

tg1, 2 t

f

下降 时间 C

加载

= 3300pf 40 90 ns

bottom 门 转变 时间: (便条 6)

bg1, 2 t

r

上升 时间 C

加载

= 3300pf 30 90 ns

bg1, 2 t

f

下降 时间 C

加载

= 3300pf 20 90 ns

tg/bg t

1D

顶 门 止 至 bottom 门 在 延迟 C

加载

= 3300pf 各自 驱动器 (便条 6) 90 ns

同步的 转变-在 延迟 时间

bg/tg t

2D

bottom 门 止 至 顶 门 在 延迟 C

加载

= 3300pf 各自 驱动器 (便条 6) 90 ns

顶 转变-在 延迟 时间

t

在(最小值)

最小 在-时间 测试 和 一个 正方形的 波 (便条 7) 180 ns

内部的 v

CC

调整器

V

INTVCC

内部的 v

CC

电压 6v < v

在

< 30v, v

EXTVCC

= 4v 4.8 5.0 5.2 V

V

LDO

INT INTV

CC

加载 规章制度 I

CC

= 0 至 20ma, v

EXTVCC

= 4v 0.2 1.0 %

V

LDO

EXT EXTV

CC

电压 漏出 I

CC

= 20ma, v

EXTVCC

= 5v 80 160 mV

V

EXTVCC

EXTV

CC

switchover 电压 I

CC

= 20ma, extv

CC

ramping 积极的

●

4.5 4.7 V

V

LDOHYS

EXTV

CC

switchover hysteresis I

CC

= 20ma, extv

CC

ramping 负的 0.2 V

vid 参数

V

偏差

运行 供应 电压 范围 2.7 5.5 V

R

ATTEN

阻抗 在 attenin ltc1709-8 20 k

Ω

和 attenout 管脚 ltc1709-9 10 k

Ω

ATTEN

ERR

resistive 分隔物 错误 ltc1709-8: vid4 = 0; ltc1709-9

●

– 0.25 0.25 %

ltc1709-8: vid4 = 1

●

–0.35 0.35 %

R

PULLUP

vid0–vid4 拉-向上 阻抗 (便条 8) 40 k

Ω

VID

THLOW

vid0–vid4 逻辑 门槛 低 0.4 V

VID

THHIGH

vid0–vid4 逻辑 门槛 高 1.6 V

VID

LEAK

vid0–vid4 泄漏 V

偏差

< vid0–vid4 < 7v 1

µ

一个

振荡器 和 阶段-锁 循环

f

NOM

名义上的 频率 V

PLLFLTR

= 1.2v 190 220 250 kHz

f

低

最低 频率 V

PLLFLTR

= 0v 120 140 160 kHz

f

高

最高的 频率 V

PLLFLTR

≥

2.4v 280 320 360 kHz

R

PLLIN

PLLIN

输入 阻抗 50 k

Ω

I

PLLFLTR

阶段 探测器 输出 电流

sinking 能力 f

PLLIN

< f

OSC

–15

µ

一个

sourcing 能力 f

PLLIN

> f

OSC

15

µ

一个

R

RELPHS

控制 2-控制 1 阶段 180 Deg