11/19

M68AW031A

写 模式

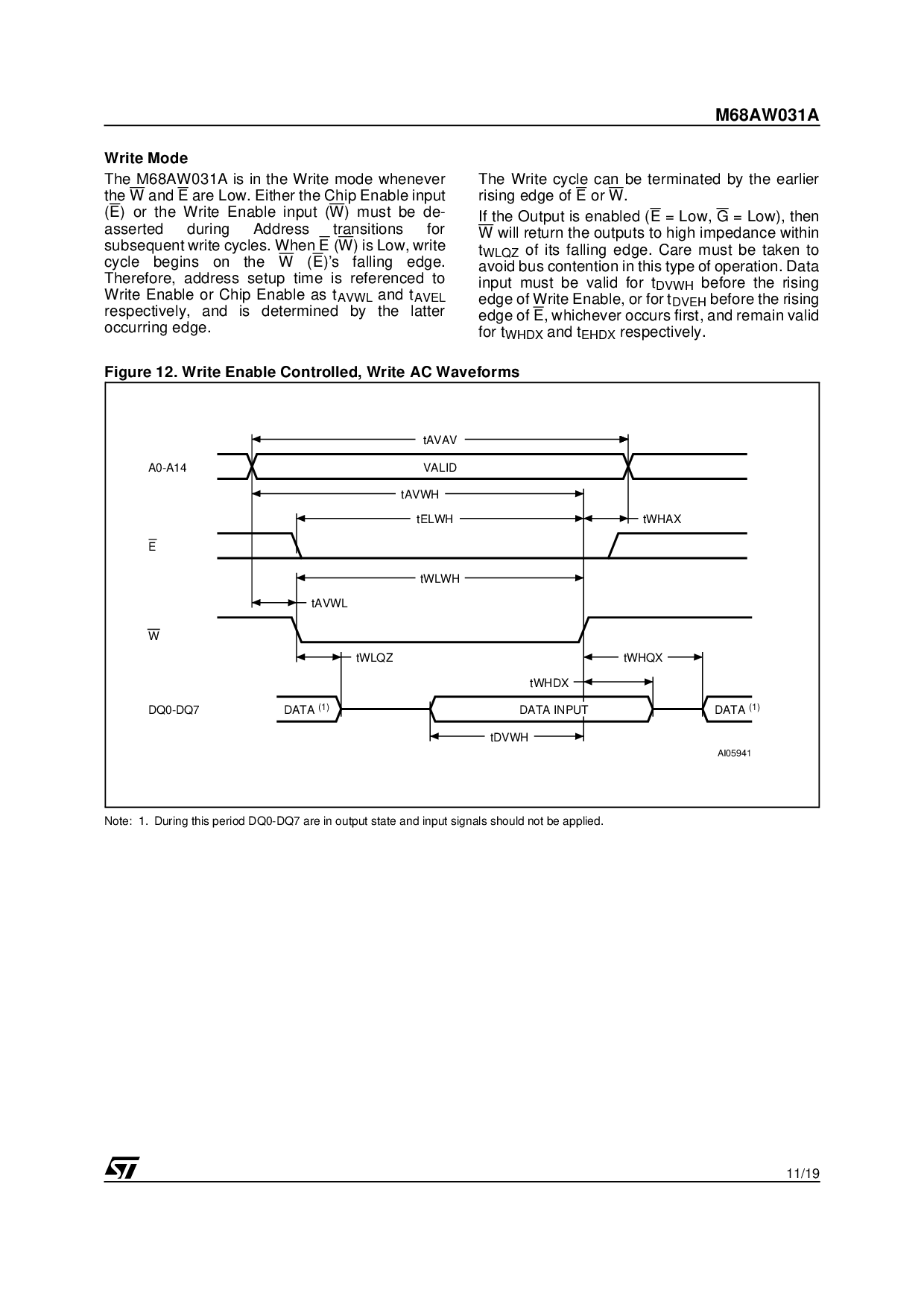

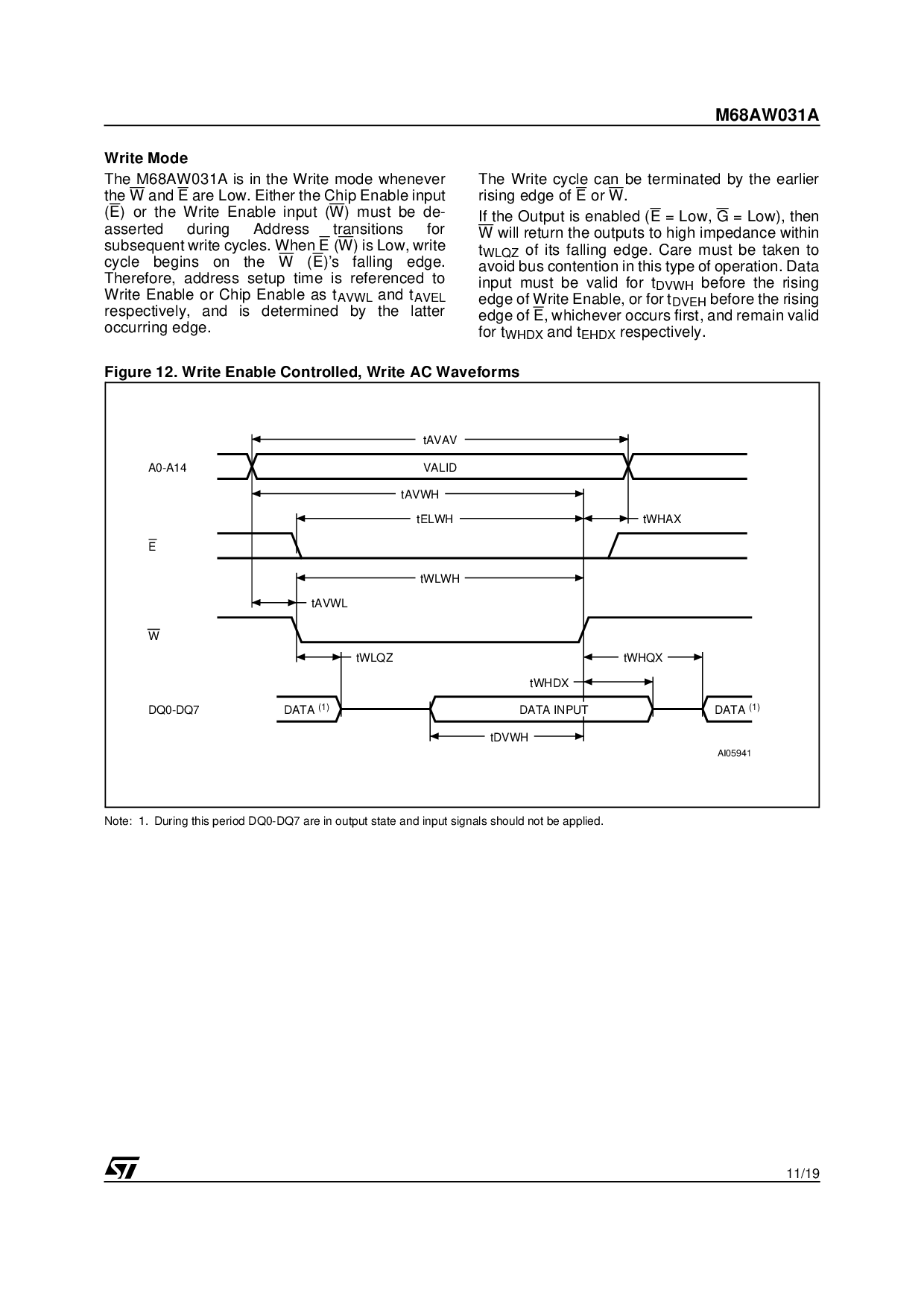

这 m68aw031a 是 在 这 写 模式 whenever

这 w

和 e是 低. 也 这 碎片 使能 输入

(e

) 或者 这 写 使能 输入 (w) 必须 是 de-

asserted 在 地址 transitions 为

subsequent 写 循环. 当 e

(w) 是 低, 写

循环 begins 在 这 w

(e)’s 下落 边缘.

因此, 地址 建制 时间 是 关联 至

写 使能 或者 碎片 使能 作 t

AVWL

和 t

AVEL

各自, 和 是 决定 用 这 latter

occurring 边缘.

这 写 循环 能 是 terminated 用 这 早期

rising 边缘 的 e

或者 w.

如果 这 输出 是 使能 (e

= 低, g= 低), 然后

W

将 返回 这 输出 至 高 阻抗 在里面

t

WLQZ

的 它的 下落 边缘. 小心 必须 是 带去 至

避免 总线 contention 在 这个 类型 的 运作. 数据

输入 必须 是 有效的 为 t

DVWH

在之前 这 rising

边缘 的 写 使能, 或者 为 t

DVEH

在之前 这 rising

边缘 的 e

, whichever occurs 第一, 和 仍然是 有效的

为 t

WHDX

和 t

EHDX

各自.

图示 12. 写 使能 控制, 写 交流 波形

便条: 1. 在 这个 时期 dq0-dq7 是 在 输出 状态 和 输入 信号 应当 不 是 应用.

AI05941

tAVAV

tWHAX

tDVWH

数据 输入

a0-a14

E

W

dq0-dq7

有效的

tAVWH

tWLWH

tAVWL

tWLQZ

tWHDX

tWHQX

tELWH

数据

(1)

数据

(1)