mc10e195 mc100e195

MOTOROLA eclinps 和 eclinps lite

dl140 — rev 4

2–2

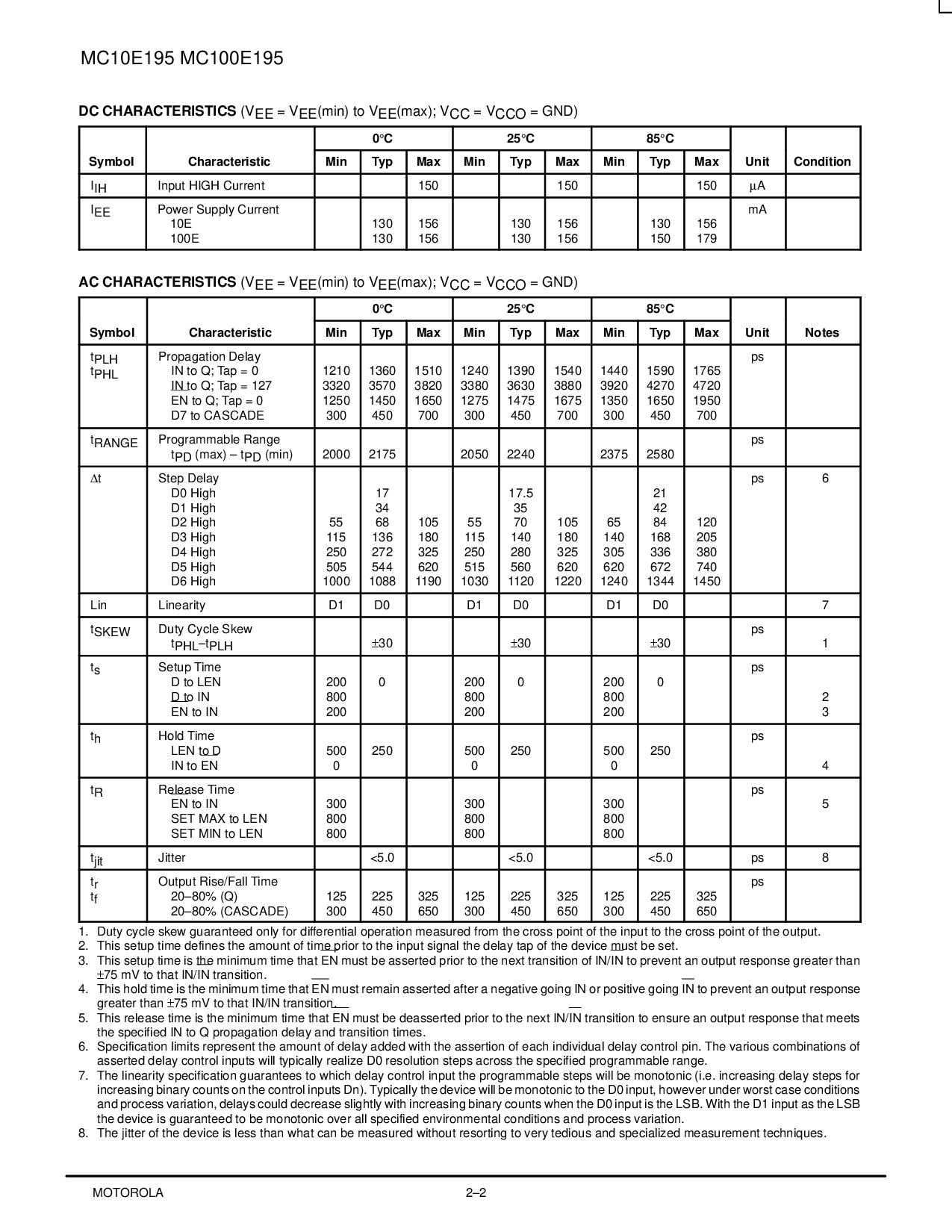

直流 特性

(v

EE

= v

EE

(最小值) 至 v

EE

(最大值); v

CC

= v

CCO

= 地)

0

°

C 25

°

C 85

°

C

标识 典型的 最小值 典型值 最大值 最小值 典型值 最大值 最小值 典型值 最大值 单位 情况

I

IH

输入 高 电流 150 150 150

µ

一个

I

EE

电源 供应 电流

10E

100E

130

130

156

156

130

130

156

156

130

150

156

179

毫安

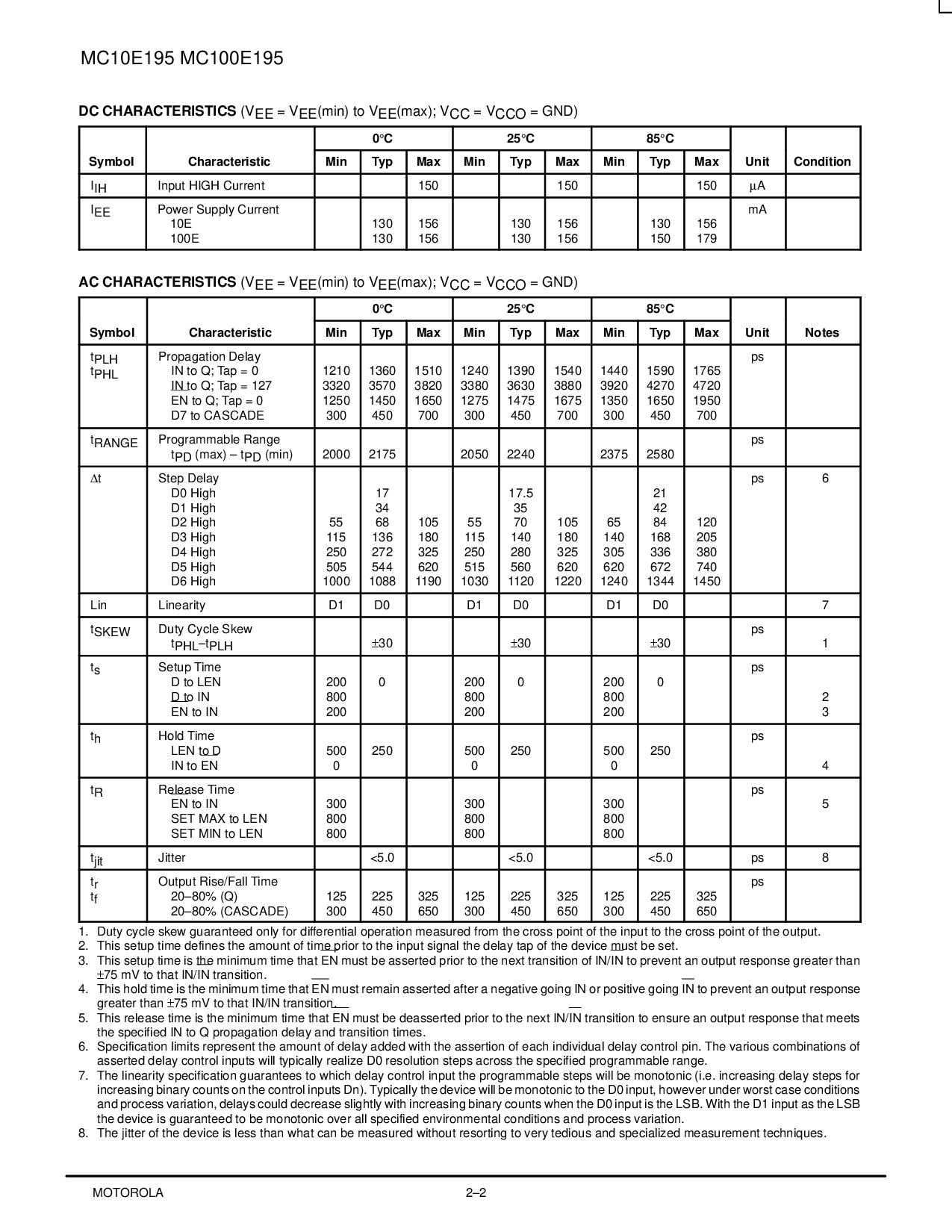

交流 特性

(v

EE

= v

EE

(最小值) 至 v

EE

(最大值); v

CC

= v

CCO

= 地)

0

°

C 25

°

C 85

°

C

标识 典型的 最小值 典型值 最大值 最小值 典型值 最大值 最小值 典型值 最大值 单位 注释

t

PLH

t

PHL

传播 延迟

在 至 q; tap = 0

在 至 q; tap = 127

EN

至 q; tap = 0

d7 至 cascade

1210

3320

1250

300

1360

3570

1450

450

1510

3820

1650

700

1240

3380

1275

300

1390

3630

1475

450

1540

3880

1675

700

1440

3920

1350

300

1590

4270

1650

450

1765

4720

1950

700

ps

t

范围

可编程序的 范围

t

PD

(最大值) – t

PD

(最小值)

2000 2175 2050 2240 2375 2580

ps

∆

t 步伐 延迟

d0 高

d1 高

d2 高

d3 高

d4 高

d5 高

d6 高

55

115

250

505

1000

17

34

68

136

272

544

1088

105

180

325

620

1190

55

115

250

515

1030

17.5

35

70

140

280

560

1120

105

180

325

620

1220

65

140

305

620

1240

21

42

84

168

336

672

1344

120

205

380

740

1450

ps 6

Lin 线性 D1 D0 D1 D0 D1 D0 7

t

SKEW

职责 循环 skew

t

PHL

–t

PLH

±

30

±

30

±

30

ps

1

t

s

建制 时间

d 至 len

d 至 在

EN

至 在

200

800

200

0 200

800

200

0 200

800

200

0

ps

2

3

t

h

支撑 时间

len 至 d

在 至 en

500

0

250 500

0

250 500

0

250

ps

4

t

R

释放 时间

EN

至 在

设置 最大值 至 len

设置 最小值 至 len

300

800

800

300

800

800

300

800

800

ps

5

t

jit

Jitter <5.0 <5.0 <5.0 ps 8

t

r

t

f

输出 上升/下降 时间

20–80% (q)

20–80% (cascade)

125

300

225

450

325

650

125

300

225

450

325

650

125

300

225

450

325

650

ps

1. 职责 循环 skew 有保证的 仅有的 为 differential 运作 量过的 从 这 交叉 要点 的 这 输入 至 这 交叉 要点 的 这 输出.

2. 这个 建制 时间 定义 这 数量 的 时间 较早的 至 这 输入 信号 这 延迟 tap 的 这 设备 必须 是 设置.

3. 这个建制 时间 是 这 最小 时间 那 en

必须 是 asserted 较早的至 这 next 转变 的 在/在至 阻止 一个 输出 回馈 更好 比

±

75 mv 至 那 在/在

转变.

4. 这个支撑 时间 是 这 最小 时间 那 en

必须 仍然是 asserted 之后 一个 负的 going 在 或者 积极的 going 在至 阻止 一个 输出回馈

更好 比

±

75 mv 至 那 在/在转变.

5. 这个释放 时间 是 这 最小时间 那 en

必须 是 deasserted 较早的 至 这 next 在/在转变 至 确保 一个 输出 回馈 那 满足

这指定 在 至 q 传播 延迟 和转变 时间.

6. 规格 限制 代表 这 数量 的 延迟 增加 和 这 assertion 的 各自 单独的 延迟 控制 管脚. 这 各种各样的 结合体 的

asserted 延迟 控制 输入 将 典型地 realize d0 决议 步伐 横过 这 指定 可编程序的 范围.

7. 这 线性 规格 guarantees 至 这个 延迟 控制 输入 这 可编程序的 步伐 将 是 monotonic (i.e. 增加 延迟步伐 为

增加二进制的 counts 在 这 控制 输入dn). typically 这 设备 将 是 monotonic 至 这 d0 输入, 不管怎样 下面 worst 情况 情况

和 处理 变化, 延迟 可以 decrease slightly 和 增加 二进制的 counts当 这 d0 输入 是 这 lsb. 和 这 d1 输入 作 这 lsb

这设备 是 有保证的 至 是 monotonic 在 所有 指定 自然环境的 情况 和 处理 变化.

8. 这 jitter 的 这 设备 是 较少 比 what 能 是 量过的 没有 resorting 至 非常 tedious 和 specialized 度量 技巧.