PCM1748

8

SBAS165

系统 时钟 和 重置

功能

系统 时钟 输入

这 pcm1748 需要 一个 系统 时钟 为 运行 这

数字的 interpolation 过滤 和 multilevel delta-sigma modu-

lators. 这 系统 时钟 是 应用 在 这 sck 输入 (管脚 16).

表格 i 显示 examples 的 系统 时钟 发生率 为

一般 音频的 抽样 比率.

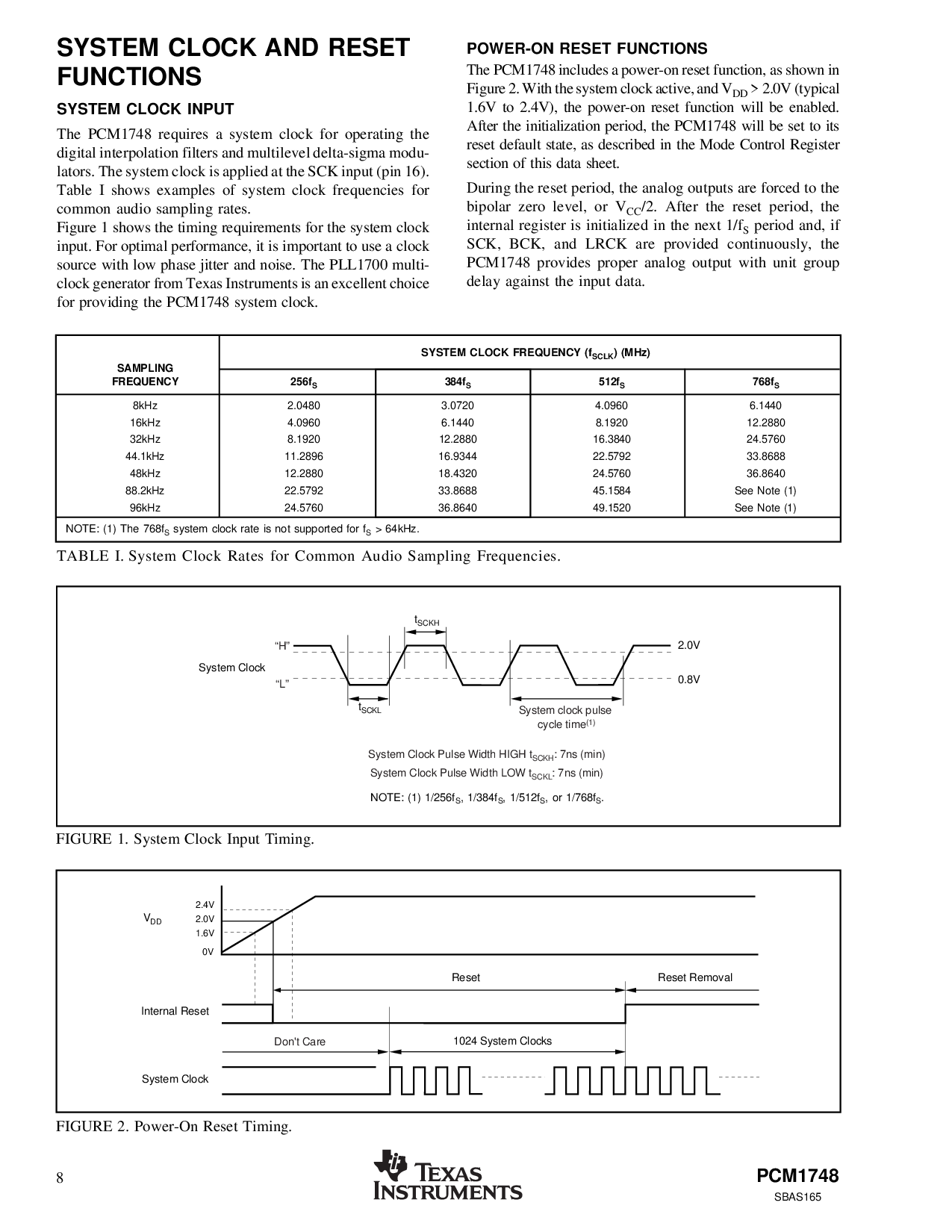

图示 1 显示 这 定时 (所需的)东西 为 这 系统 时钟

输入. 为 最优的 效能, 它 是 重要的 至 使用 一个 时钟

源 和 低 阶段 jitter 和 噪音. 这 pll1700 multi-

时钟 发生器 从 德州 器械 是 一个 极好的 选择

为 供应 这 pcm1748 系统 时钟.

电源-在 重置 功能

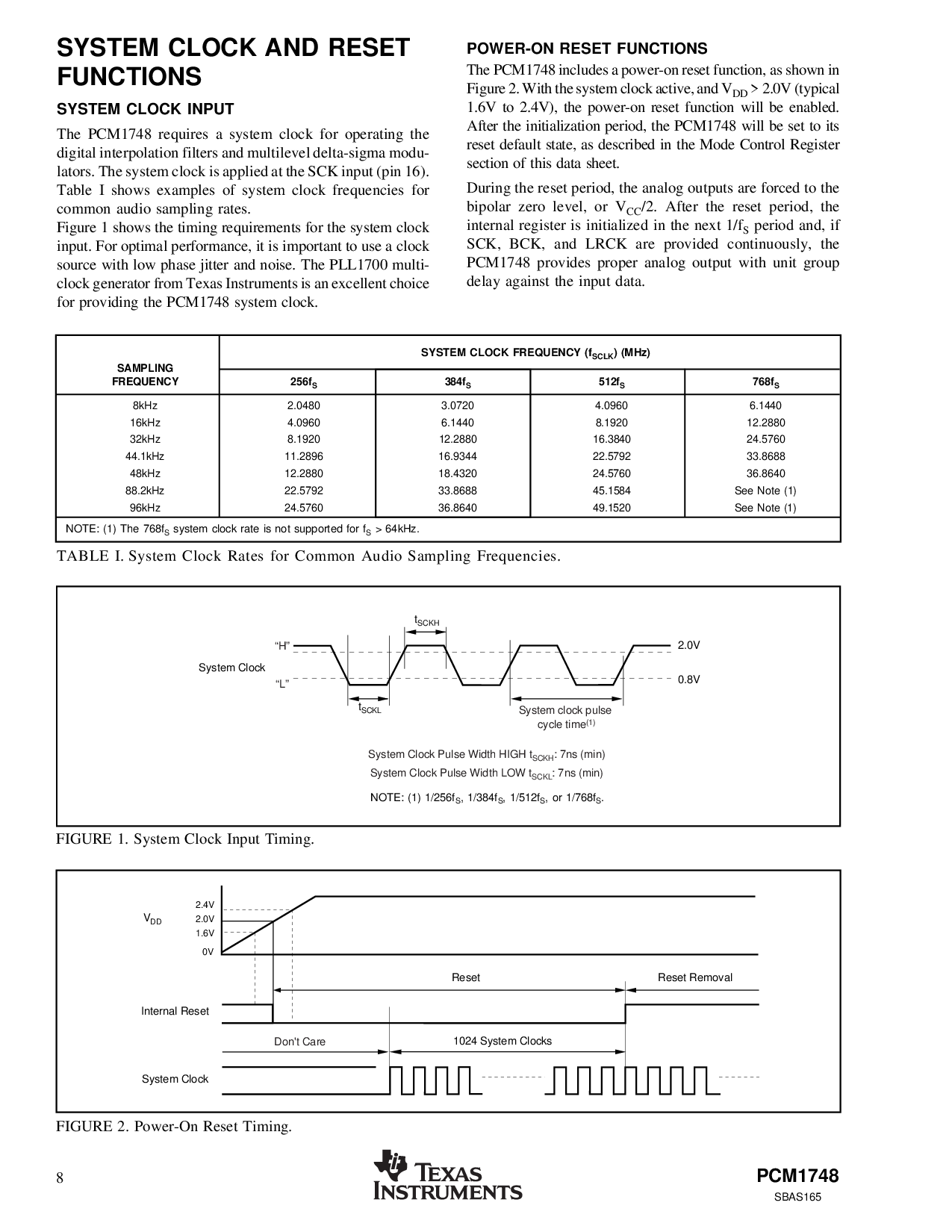

这 pcm1748 包含 一个 电源-在 重置 函数, 作 显示 在

图示 2. 和 这 系统 时钟 起作用的, 和 v

DD

> 2.0v (典型

1.6v 至 2.4v), 这 电源-在 重置 函数 将 是 使能.

之后 这 initialization 时期, 这 pcm1748 将 是 设置 至 它的

重置 default 状态, 作 描述 在 这 模式 控制 寄存器

部分 的 这个 数据 薄板.

在 这 重置 时期, 这 相似物 输出 是 强迫 至 这

双极 零 水平的, 或者 v

CC

/2. 之后 这 重置 时期, 这

内部的 寄存器 是 initialized 在 这 next 1/f

S

时期 和, 如果

sck, bck, 和 lrck 是 提供 continuously, 这

pcm1748 提供 恰当的 相似物 输出 和 单位 组

延迟 相反 这 输入 数据.

图示 1. 系统 时钟 输入 定时.

抽样

频率 256f

S

384f

S

512f

S

768f

S

8kHz 2.0480 3.0720 4.0960 6.1440

16kHz 4.0960 6.1440 8.1920 12.2880

32kHz 8.1920 12.2880 16.3840 24.5760

44.1khz 11.2896 16.9344 22.5792 33.8688

48kHz 12.2880 18.4320 24.5760 36.8640

88.2khz 22.5792 33.8688 45.1584 看 便条 (1)

96kHz 24.5760 36.8640 49.1520 看 便条 (1)

便条: (1) 这 768f

S

系统 时钟 比率 是 不 supported 为 f

S

> 64khz.

表格 i. 系统 时钟 比率 为 一般 音频的 抽样 发生率.

系统 时钟 频率 (f

SCLK

) (mhz)

图示 2. 电源-在 重置 定时.

1024 系统 clocks

重置 重置 除去

V

DD

内部的 重置

2.4v

2.0v

1.6v

0V

系统 时钟

don't 小心

t

SCKH

t

SCKL

2.0v

0.8v

系统 时钟

系统 时钟 脉冲波

循环 时间

(1)

“

H

”

“

L

”

系统 时钟 脉冲波 宽度 高 t

SCKH

: 7ns (最小值)

系统 时钟 脉冲波 宽度 低 t

SCKL

: 7ns (最小值)

便条: (1) 1/256f

S

, 1/384f

S

, 1/512f

S

, 或者 1/768f

S

.