spartan 和 spartan-xl families 地方 可编程序的 门 arrays

ds060 (v1.6) 九月 19, 2001

www.xilinx.com

5

产品 规格

1-800-255-7778

R

.

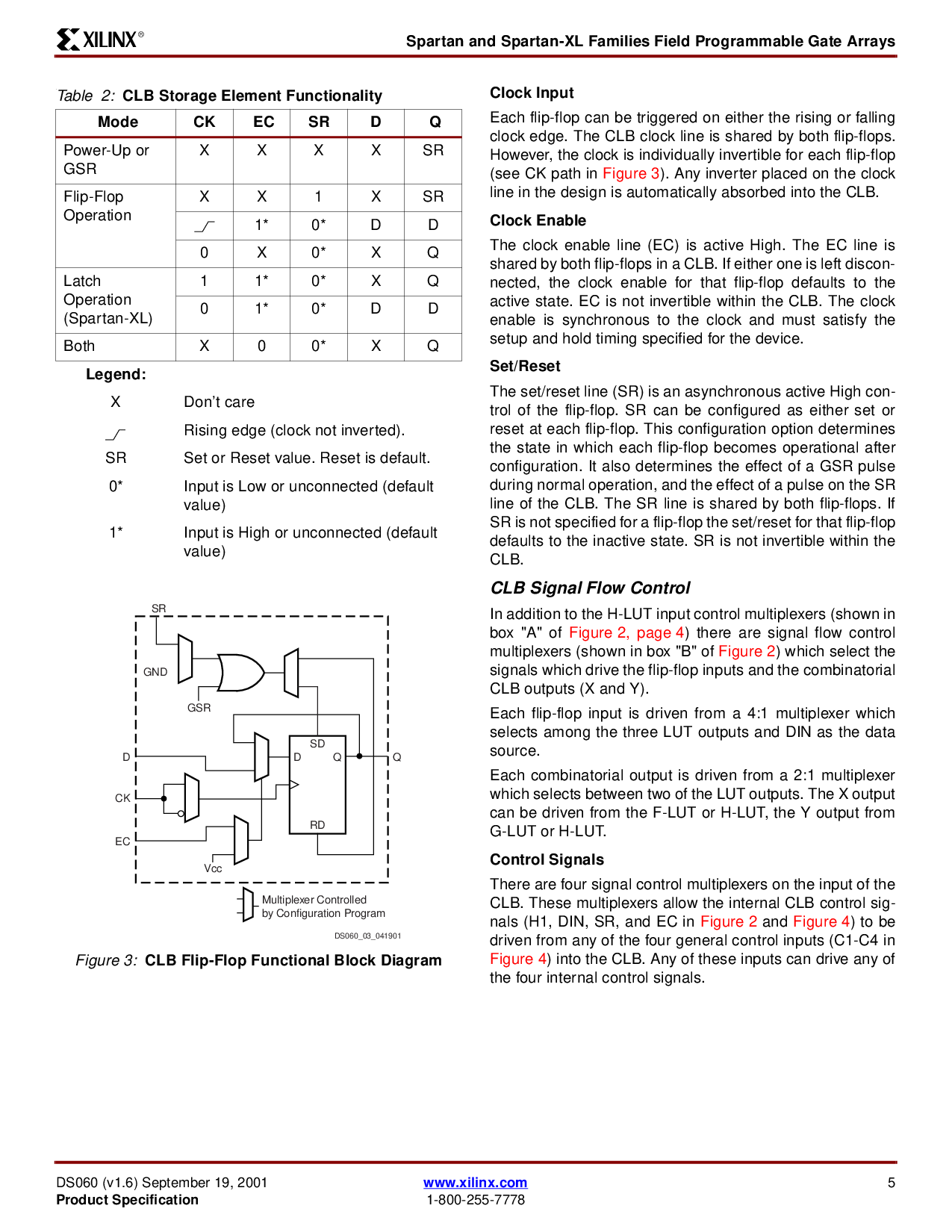

时钟 输入

各自 flip-flop 能 是 triggered 在 也 这 rising 或者 下落

时钟 边缘. 这 clb 时钟 线条 是 shared 用 两个都 flip-flops.

不管怎样, 这 时钟 是 individually invertible 为 各自 flip-flop

(看 ck path 在图示 3). 任何 inverter 放置 在 这 时钟

线条 在 这 设计 是 automatically absorbed 在 这 clb.

时钟 使能

这 时钟 使能 线条 (ec) 是 起作用的 高. 这 ec 线条 是

shared 用 两个都 flip-flops 在 一个 clb. 如果 也 一个 是 left discon-

nected, 这 时钟 使能 为 那 flip-flop defaults 至 这

起作用的 状态. ec 是 不 invertible 在里面 这 clb. 这 时钟

使能 是 同步的 至 这 时钟 和 必须 satisfy 这

建制 和 支撑 定时 指定 为 这 设备.

设置/重置

这 设置/重置 线条 (sr) 是 一个 异步的 起作用的 高 con-

trol 的 这 flip-flop. sr 能 是 配置 作 也 设置 或者

重置 在 各自 flip-flop. 这个 配置 选项 确定

这 状态 在 这个 各自 flip-flop 变为 运算的 之后

配置. 它 也 确定 这 效应 的 一个 gsr 脉冲波

在 正常的 运作, 和 这 效应 的 一个 脉冲波 在 这 sr

线条 的 这 clb. 这 sr 线条 是 shared 用 两个都 flip-flops. 如果

sr 是 不 指定 为 一个 flip-flop 这 设置/重置 为 那 flip-flop

defaults 至 这 inactive 状态. sr 是 不 invertible 在里面 这

clb.

clb 信号 流动 控制

在 增加 至 这 h-lut 输入 控制 multiplexers (显示 在

盒 "一个" 的图示 2, 页 4) 那里 是 信号 流动 控制

multiplexers (显示 在 盒 "b" 的图示 2) 这个 选择 这

信号 这个 驱动 这 flip-flop 输入 和 这 combinatorial

clb 输出 (x 和 y).

各自 flip-flop 输入 是 驱动 从 一个 4:1 多路调制器 这个

选择 among 这 三 lut 输出 和 din 作 这 数据

源.

各自 combinatorial 输出 是 驱动 从 一个 2:1 多路调制器

这个 选择 在 二 的 这 lut 输出. 这 x 输出

能 是 驱动 从 这 f-lut 或者 h-lut, 这 y 输出 从

g-lut 或者 h-lut.

控制 信号

那里 是 四 信号 控制 multiplexers 在 这 输入 的 这

clb. 这些 multiplexers 准许 这 内部的 clb 控制 sig-

nals (h1, din, sr, 和 ec 在图示 2和图示 4) 至 是

驱动 从 任何 的 这 四 一般 控制 输入 (c1-c4 在

图示 4) 在 这 clb. 任何 的 这些 输入 能 驱动 任何 的

这 四 内部的 控制 信号.

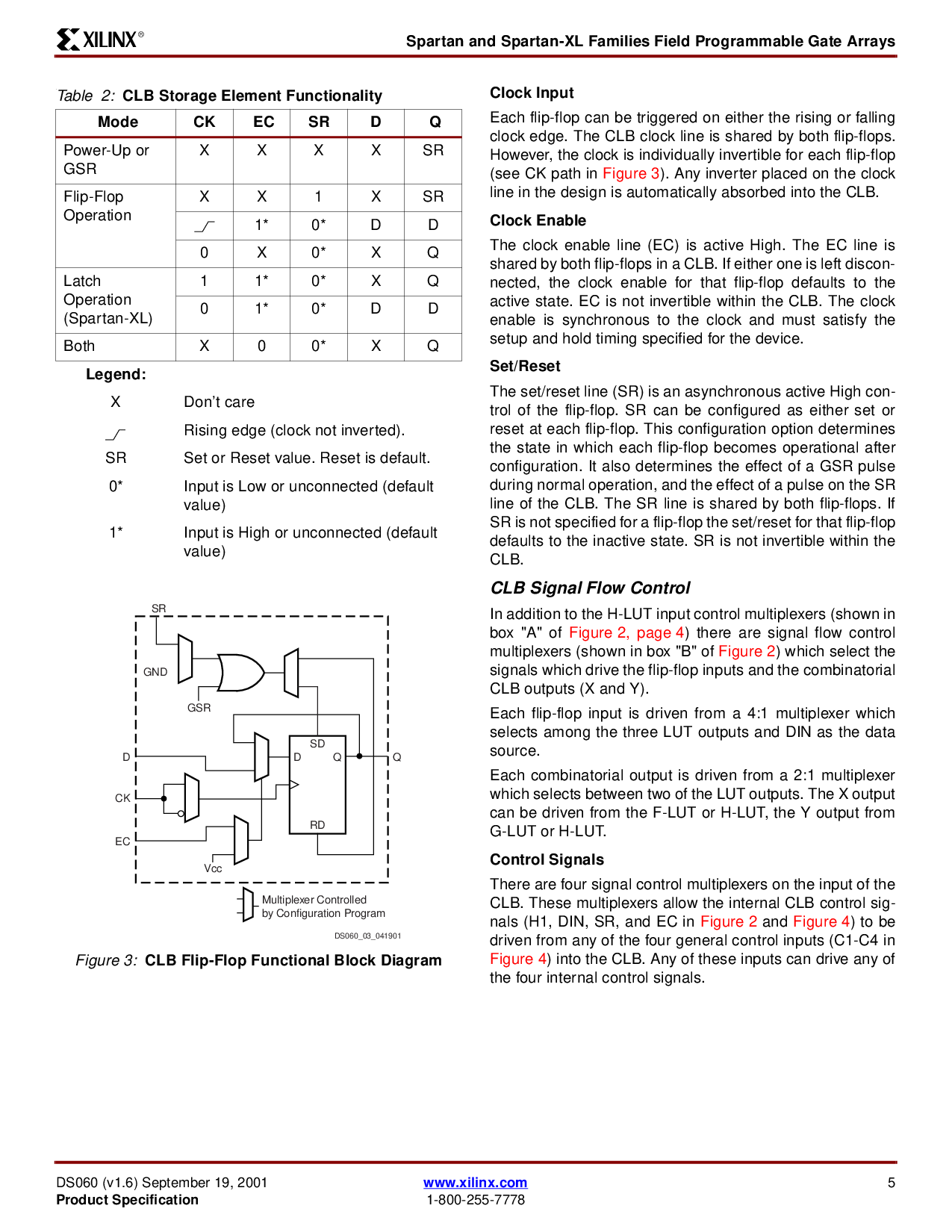

表格 2:

clb 存储 元素 符合实际

模式 CK EC SR D Q

Po我们r-Upor

GSR

XXXXSR

flip-flop

运作

XX1XSR

1* 0* D D

0X0*XQ

获得

运作

(spartan-xl)

11*0*XQ

01*0*DD

两个都 X 0 0* X Q

legend:

XDon

’

t 小心

rising 边缘 (时钟 不 inverted).

SR 设置 或者 重置 值. 重置 是 default.

0* 输入 是 低 或者 unconnected (default

值)

1* 输入 是 高 或者 unconnected (default

值)

图示 3:

clb flip-flop 函数的 块 图解

多路调制器 控制

用 配置 程序

DQQD

地

GSR

Vcc

CK

EC

SR

SD

RD

ds060_03_041901