rev. 0

AD7675

–

6

–

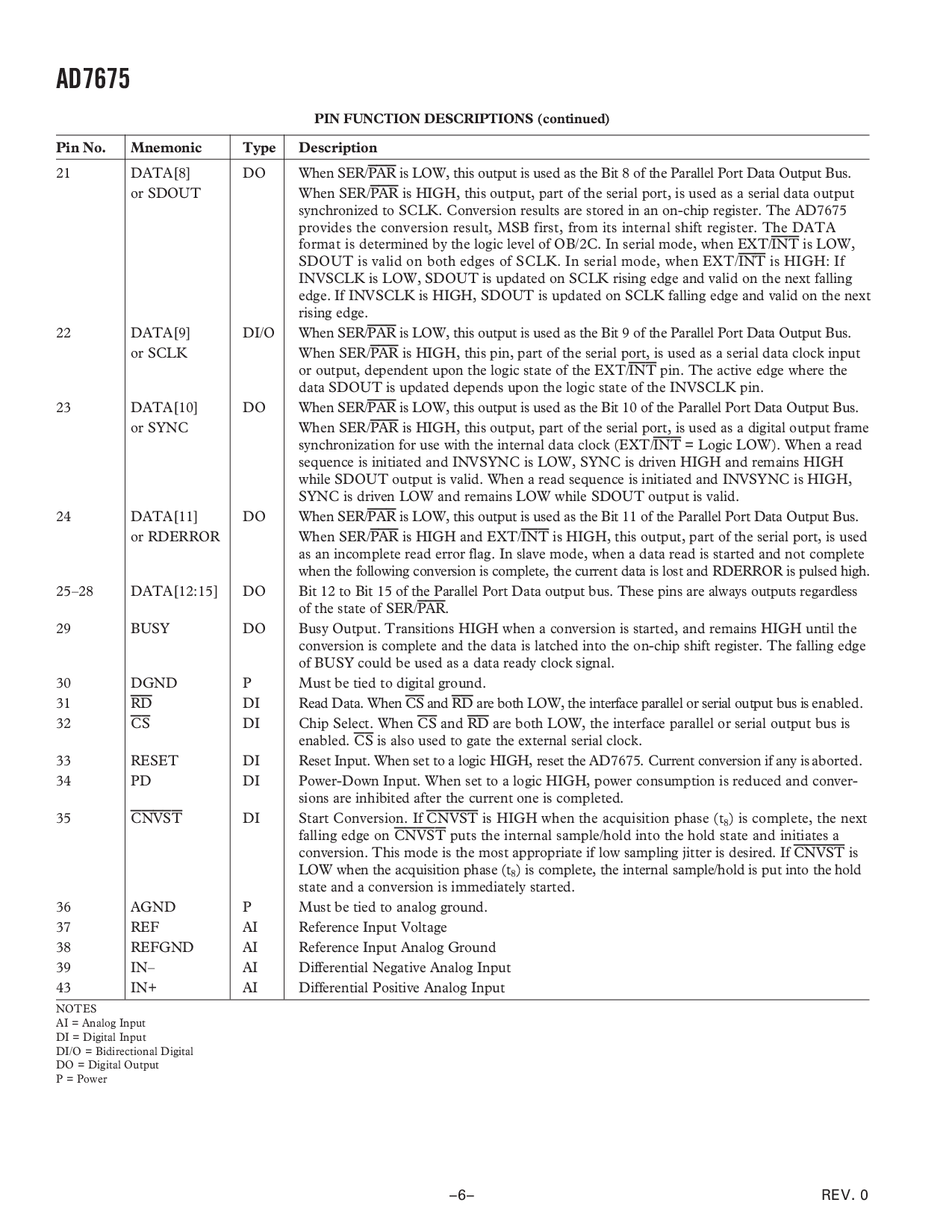

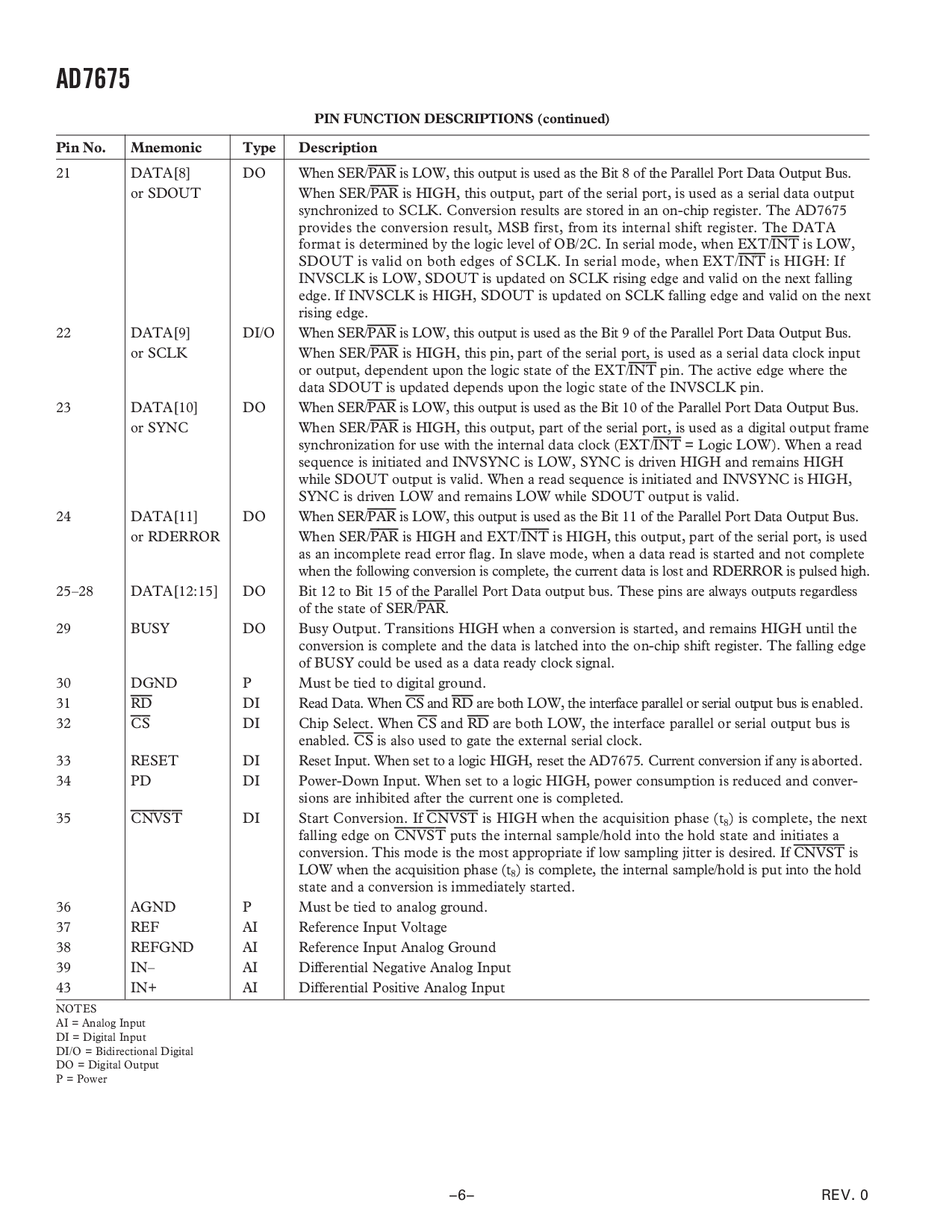

管脚 函数 描述 (持续)

管脚 非. Mnemonic 类型 描述

21 DATA[8] 做 当 ser/

PAR

是 低, 这个 输出 是 使用 作 这 位 8 的 这 并行的 端口 数据 输出 总线.

或者 sdout 当 ser/

PAR

是 高, 这个 输出, 部分 的 这 串行 端口, 是 使用 作 一个 串行 数据 输出

同步 至 sclk. 转换 结果 是 贮存 在 一个 在-碎片 寄存器. 这 ad7675

提供 这 转换 结果, msb 第一, 从 它的 内部的 变换 寄存器. 这 数据

format 是决定 用 这 逻辑 水平的 的 ob/2c. 在 串行 模式, 当 ext/

INT

是 低,

sdout 是 有效的 在 两个都 edges 的 sclk. 在 串行 模式, 当 ext/

INT

是 高: 如果

invsclk 是 低, sdout 是 updated 在 sclk rising 边缘 和 有效的 在 这 next 下落

边缘. 如果 invsclk 是 高, sdout 是 updated 在 sclk 下落 边缘 和 有效的 在 这 next

rising 边缘.

22 DATA[9] di/o 当 ser/

PAR

是 低, 这个 输出 是 使用 作 这 位 9 的 这 并行的 端口 数据 输出 总线.

或者 sclk 当 ser/

PAR

是 高, 这个 管脚, 部分 的 这 串行 端口, 是 使用 作 一个 串行 数据 时钟 输入

或者 输出, 依赖 在之上 这 逻辑 状态 的 这 ext/

INT

管脚. 这 起作用的 边缘 在哪里 这

数据 sdout 是 updated 取决于 在之上 这 逻辑 状态 的 这 invsclk 管脚.

23 DATA[10] 做 当 ser/

PAR

是 低, 这个 输出 是 使用 作 这 位 10 的 这 并行的 端口 数据 输出 总线.

或者 同步 当 ser/

PAR

是 高, 这个 输出, 部分 的 这 串行 端口, 是 使用 作 一个 数字的 输出 框架

同步 为 使用 和 这 内部的 数据 时钟 (ext/

INT

= 逻辑 低). 当 一个 读

sequence 是 initiated 和 invsync 是 低, 同步 是 驱动 高 和 仍然是 高

当 sdout 输出 是 有效的. 当 一个 读 sequence 是 initiated 和 invsync 是 高,

同步 是 驱动 低 和 仍然是 低 当 sdout 输出 是 有效的.

24 DATA[11] 做 当 ser/

PAR

是 低, 这个 输出 是 使用 作 这 位 11 的 这 并行的 端口 数据 输出 总线.

或者 rderror 当 ser/

PAR

是 高 和 ext/

INT

是 高, 这个 输出, 部分 的 这 串行 端口, 是 使用

作 一个 incomplete 读 错误 标记. 在 从动装置 模式, 当 一个 数据 读 是 started 和 不 完全

当 这 下列的 转换 是 完全, 这 电流 数据 是 lost 和 rderror 是 搏动 高.

25–28 data[12:15] 做 位 12 至 位 15 的 这 并行的 端口 数据 输出 总线. 这些 管脚 是 总是 输出 regardless

的 这 状态 的 ser/

PAR

.

29 BUSY 做 busy 输出. transitions 高 当 一个 转换 是 started, 和 仍然是 高 直到 这

转换 是 完全 和 这 数据 是 latched 在 这 在-碎片 变换 寄存器. 这 下落 边缘

的 busy 可以 是 使用 作 一个 数据 准备好 时钟 信号.

30 DGND P 必须 是 系 至 数字的 地面.

31

RD

DI 读 数据. 当

CS

和

RD

是 两个都 低, 这 接口 并行的 或者 串行 输出 总线 是使能.

32

CS

DI 碎片 选择. 当

CS

和

RD

是 两个都 低, 这 接口 并行的 或者 串行 输出 总线 是

使能.

CS

是 也 使用 至 门 这 外部 串行 时钟.

33 重置 DI 重置 输入. 当 设置 至 一个 逻辑 高, 重置 这 ad7675. 电流 转换 如果 任何 是aborted.

34 PD DI 电源-向下 输入. 当 设置 至 一个 逻辑 高, 电源 消耗量 是 减少 和 变换器-

sions 是 inhibited 之后 这 电流 一个 是 完成.

35

CNVST

DI

开始 转换. 如果

CNVST

是 高 当 这 acquisition 阶段 (t

8

) 是 完全, 这 next

下落 边缘 在

CNVST

puts 这 内部的 样本/支撑 在 这 支撑 状态 和 initiates 一个

转换. 这个 模式 是 这 大多数 适合的 如果 低 抽样 jitter 是 desired. 如果

CNVST

是

低 当 这 acquisition 阶段 (t

8

) 是 完全, 这 内部的 样本/支撑 是 放 在 这 支撑

状态 和 一个 转换 是 立即 started.

36 AGND P 必须 是 系 至 相似物 地面.

37 REF AI 涉及 输入 电压

38 REFGND AI 涉及 输入 相似物 地面

39 IN– AI 差别的 负的 相似物 输入

43 IN+ AI 差别的 积极的 相似物 输入

注释

ai = 相似物 输入

di = 数字的 输入

di/o = 双向的 数字的

做 = 数字的 输出

p = 电源