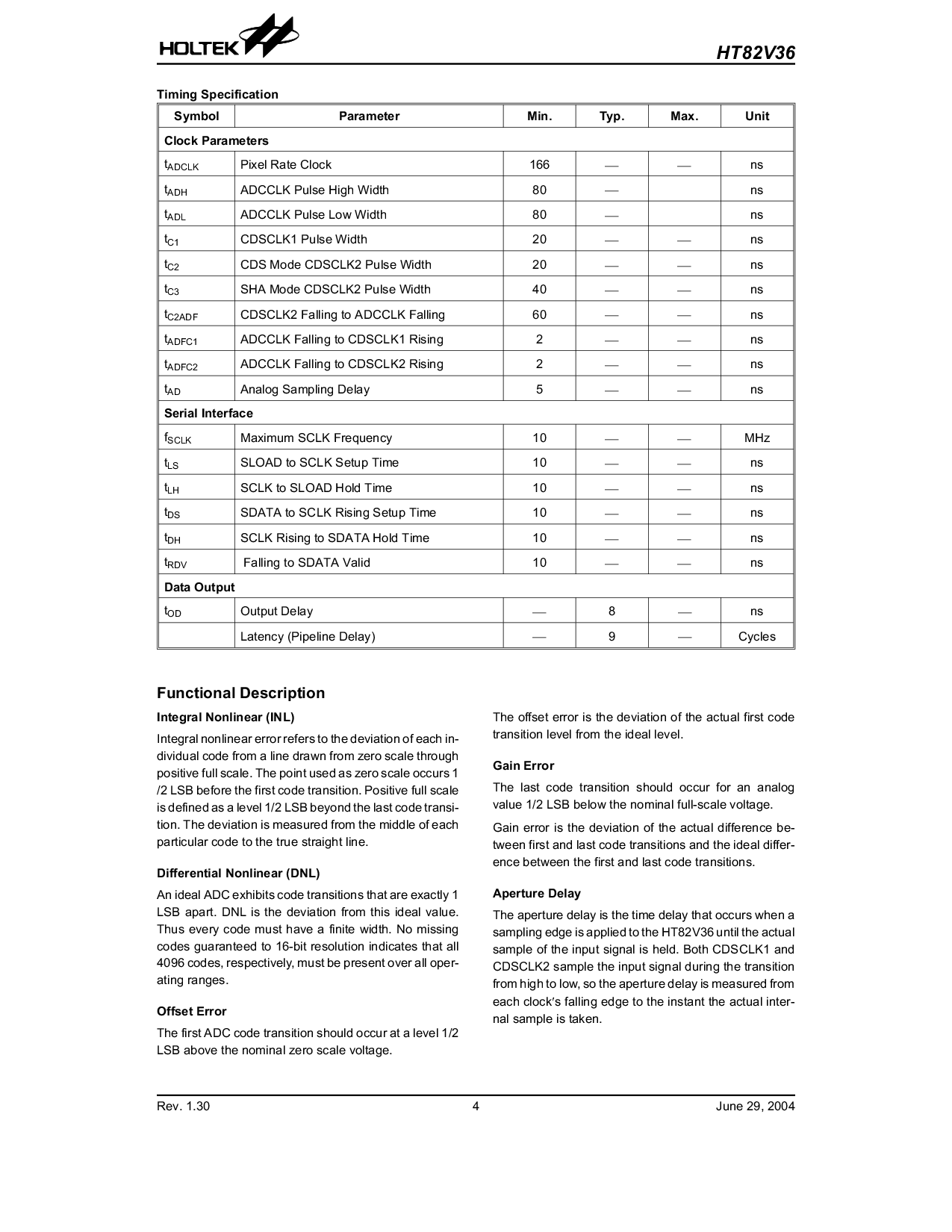

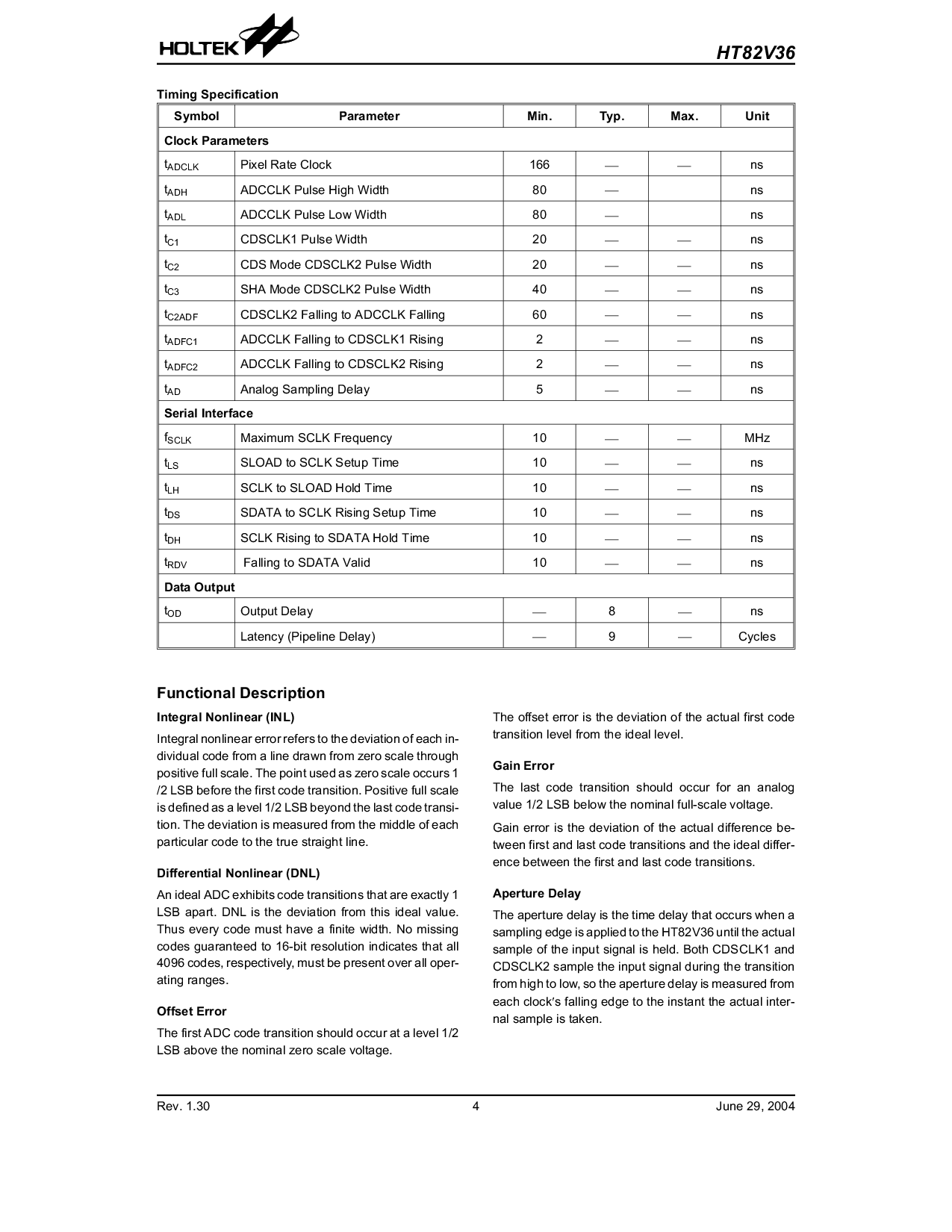

定时 规格

标识 参数 最小值 典型值 最大值 单位

时钟 参数

t

ADCLK

Pixel 比率 时钟 166

ns

t

ADH

ADCCLK 脉冲波 高 宽度 80

ns

t

ADL

ADCCLK 脉冲波 低 宽度 80

ns

t

C1

CDSCLK1 脉冲波 宽度 20

ns

t

C2

CDS 模式 CDSCLK2 脉冲波 宽度 20

ns

t

C3

SHA 模式 CDSCLK2 脉冲波 宽度 40

ns

t

C2ADF

CDSCLK2 下落 至 ADCCLK 下落 60

ns

t

ADFC1

ADCCLK 下落 至 CDSCLK1 Rising 2

ns

t

ADFC2

ADCCLK 下落 至 CDSCLK2 Rising 2

ns

t

AD

相似物 抽样 延迟 5

ns

串行 接口

f

SCLK

最大 SCLK 频率 10

MHz

t

LS

SLOAD 至 SCLK 建制 时间 10

ns

t

LH

SCLK 至 SLOAD 支撑 时间 10

ns

t

DS

SDATA 至 SCLK Rising 建制 时间 10

ns

t

DH

SCLK Rising 至 SDATA 支撑 时间 10

ns

t

RDV

下落 至 SDATA 有效的 10

ns

数据 输出

t

OD

输出 延迟

8

ns

Latency (pipeline 延迟)

9

循环

HT82V36

rev. 1.30 4 六月 29, 2004

函数的 描述

Integral 非线性的 (inl)

Integral 非线性的 错误 谈及 至 这 背离 的 各自 在

-

dividual 代号 从 一个 线条 描绘 从 零 规模 通过

积极的 全部 规模. 这 要点 使用 作 零 规模 occurs 1

/

2 LSB 在之前 这 第一 代号 转变. 积极的 全部 规模

是 定义 作 一个 水平的 1

/

2 LSB 在之外 这 last 代号 transi

-

tion. 这 背离 是 量过的 从 这 middle 的 各自

particular 代号 至 这 真实 笔直地 线条.

差别的 非线性的 (dnl)

一个 完美的 模数转换器 exhibits 代号 transitions 那 是 exactly 1

LSB apart. DNL 是 这 背离 从 这个 完美的 值.

因此 每 代号 必须 有 一个 finite 宽度. 非 missing

代号 有保证的 至 16-位 决议 indicates 那 所有

4096 代号, 各自, 必须 是 呈现 在 所有 oper

-

ating 范围.

补偿 错误

这 第一 模数转换器 代号 转变 应当 出现 在 一个 水平的 1

/

2

LSB 在之上 这 名义上的 零 规模 电压.

这 补偿 错误 是 这 背离 的 这 真实的 第一 代号

转变 水平的 从 这 完美的 水平的.

增益 错误

这 last 代号 转变 应当 出现 为 一个 相似物

值 1

/

2 LSB 在下 这 名义上的 全部-规模 电压.

增益 错误 是 这 背离 的 这 真实的 区别 是

-

tween 第一 和 last 代号 transitions 和 这 完美的 differ

-

ence 在 这 第一 和 last 代号 transitions.

Aperture 延迟

这 aperture 延迟 是 这 时间 延迟 那 occurs 当 一个

抽样 边缘 是 应用 至 这 HT82V36 直到 这 真实的

样本 的 这 输入 信号 是 使保持. 两个都 CDSCLK1 和

CDSCLK2 样本 这 输入 信号 在 这 转变

从 高 至 低, 所以 这 aperture 延迟 是 量过的 从

各自 时钟

s 下落 边缘 至 这 instant 这 真实的 inter

-

nal 样本 是 带去.