TDA7478

4/8

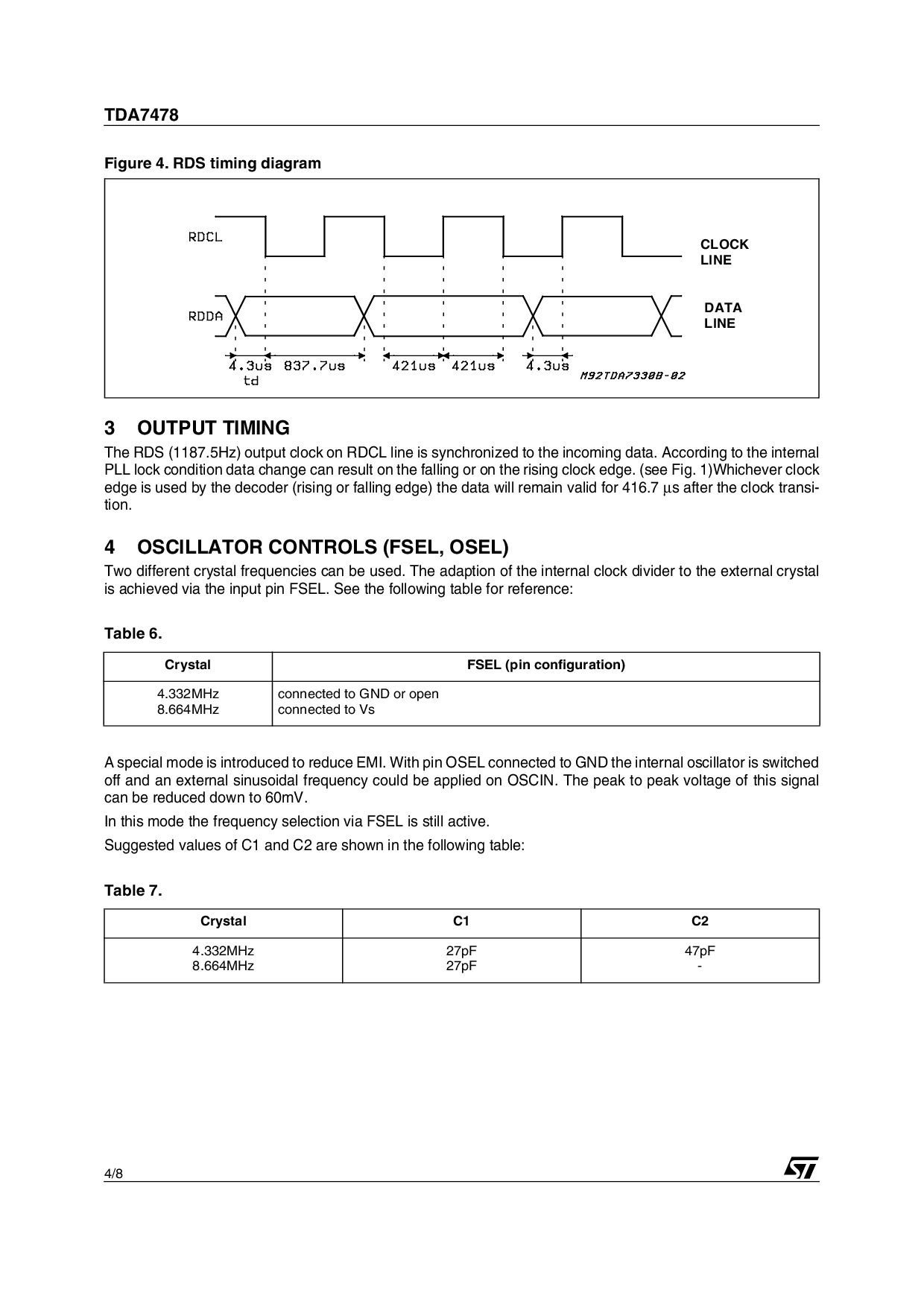

图示 4. rds 定时 图解

3 输出 定时

这 rds (1187.5hz) 输出 时钟 在 rdcl 线条 是 同步 至 这 新当选的 数据. 符合 至 这 内部的

pll 锁 情况 数据 改变 能 结果 在 这 下落 或者 在 这 rising 时钟 边缘. (看 图. 1)whichever 时钟

边缘 是 使用 用 这 解码器 (rising 或者 下落 边缘) 这 数据 将 仍然是 有效的 为 416.7

µ

s 之后 这 时钟 transi-

tion.

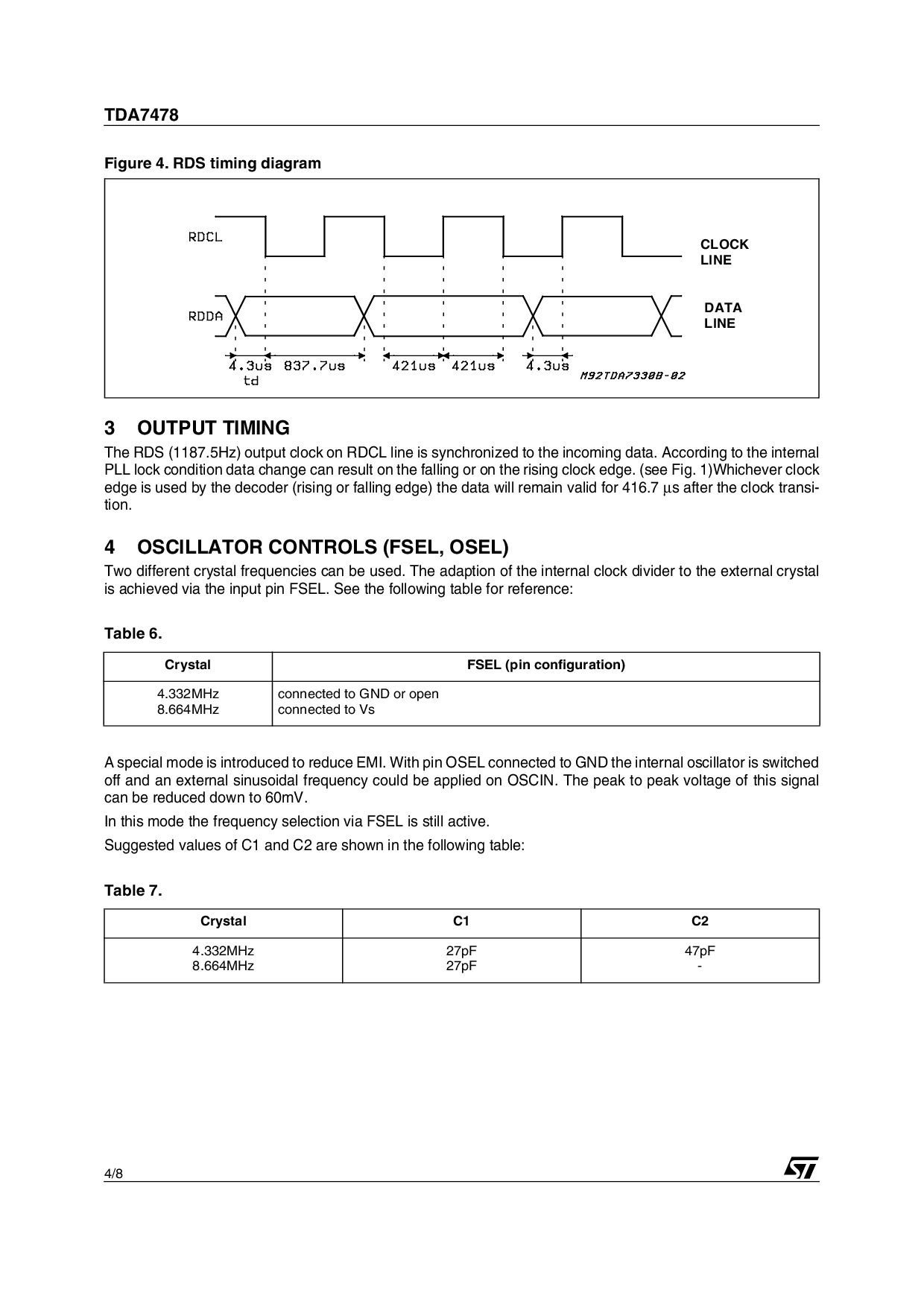

4 振荡器 控制 (fsel, osel)

二 不同的 结晶 发生率 能 是 使用. 这 adaption 的 这 内部的 时钟 分隔物 至 这 外部 结晶

是 达到 通过 这 输入 管脚 fsel. 看 这 下列的 表格 为 涉及:

表格 6.

一个 特定的 模式 是 introduced 至 减少 emi. 和 管脚 osel 连接 至 地 这 内部的 振荡器 是 切换

止 和 一个 外部 sinusoidal 频率 可以 是 应用 在 oscin. 这 顶峰 至 顶峰 电压 的 这个 信号

能 是 减少 向下 至 60mv.

在 这个 模式 这 频率 选择 通过 fsel 是 安静的 起作用的.

建议的 值 的 c1 和 c2 是 显示 在 这 下列的 表格:

表格 7.

结晶 fsel (管脚 配置)

4.332mhz

8.664mhz

连接 至 地 或者 打开

连接 至 vs

结晶 C1 C2

4.332mhz

8.664mhz

27pF

27pF

47pF

-

时钟

线条

数据

线条