6.42

IDT709179L

高-速 32k x 9 同步的 pipelined 双-端口 静态的 内存 工业的 和 商业的 温度 ranges

9

初步的

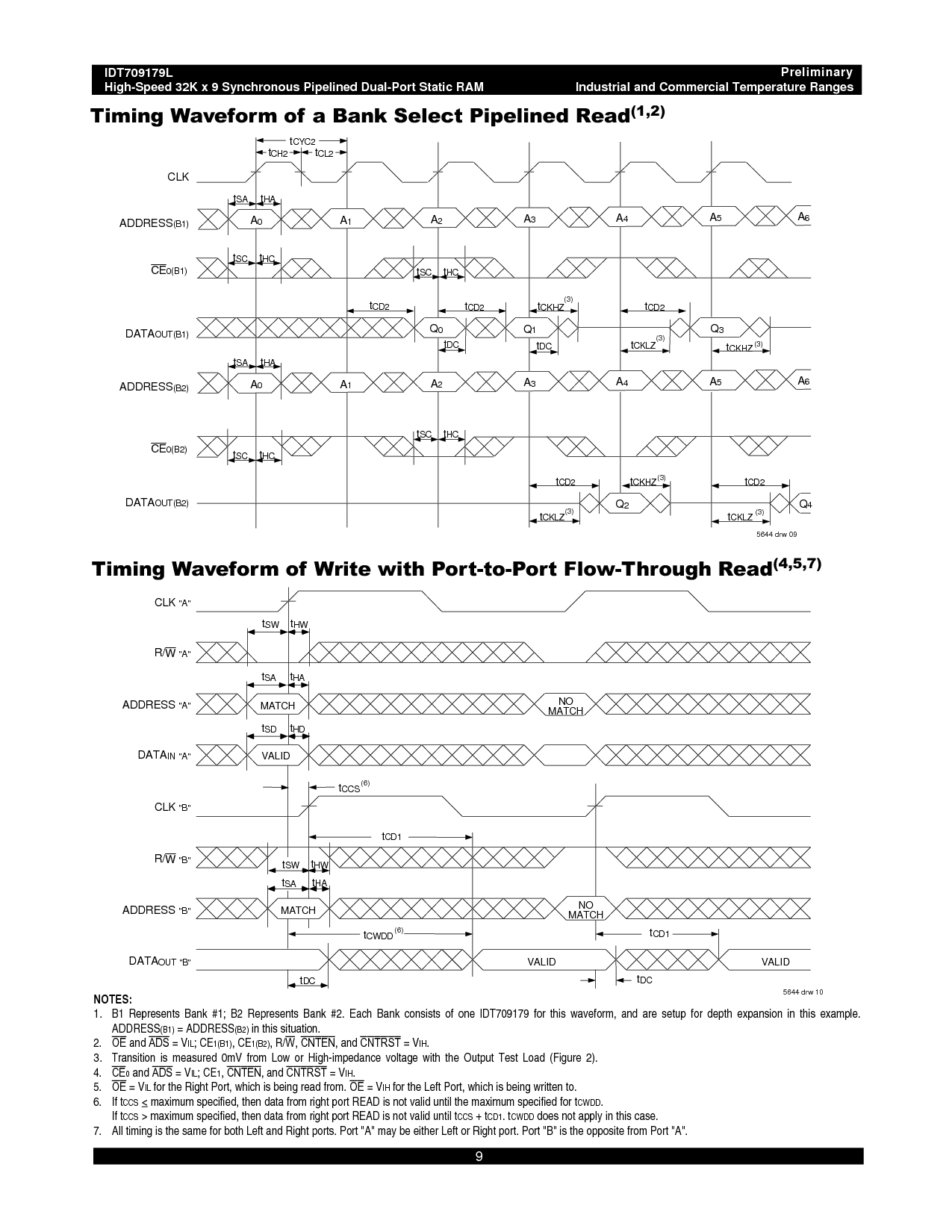

注释:

1. b1 代表 bank #1; b2 代表 bank #2. 各自 bank 组成 的 一个 idt709179 为 这个 波形, 和 是 建制 为 depth expansion 在 这个 例子.

地址

(b1)

= 地址

(b2)

在 这个 situation.

2.

OE

和

ADS

= v

IL

; ce

1(b1)

, ce

1(b2)

, r/

W

,

CNTEN

, 和

CNTRST

= v

IH

.

3. 转变 是 量过的 0mv 从 低 或者 高-阻抗 电压 和 这 输出 测试 加载 (图示 2).

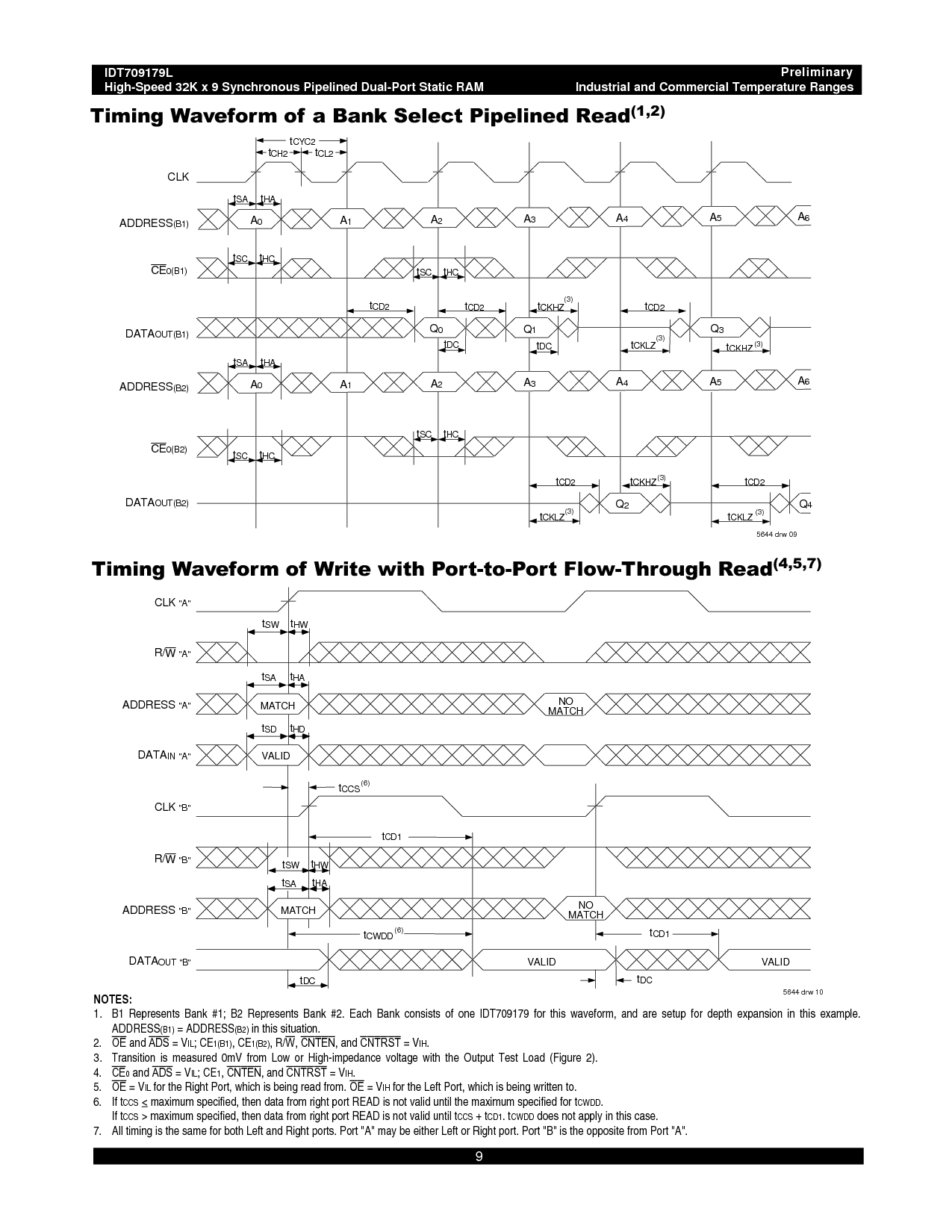

4.

CE

0

和

ADS

= v

IL

; ce

1

,

CNTEN

, 和

CNTRST

= v

IH

.

5.

OE

= v

IL

为 这 正确的 端口, 这个 是 正在 读 从.

OE

= v

IH

为 这 left 端口, 这个 是 正在 写 至.

6. 如果 t

CCS

< 最大 指定, 然后 数据 从 正确的 端口 读 是 不 有效的 直到 这 最大 指定 为 t

CWDD

.

如果 t

CCS

> 最大 指定, 然后 数据 从 正确的 端口 读 是 不 有效的 直到 t

CCS

+ t

CD1

. t

CWDD

做 不 应用 在 这个 情况.

7. 所有 定时 是 这 一样 为 两个都 left 和 正确的 端口. 端口 "一个" 将 是 也 left 或者 正确的 端口. 端口 "b" 是 这 opposite 从 端口 "a".

t

SC

t

HC

CE

0(b1)

地址

(b1)

一个

0

一个

1

一个

2

一个

3

一个

4

一个

5

t

SA

t

HA

CLK

5644 drw 09

Q

0

Q

1

Q

3

数据

输出(b1)

t

CH2

t

CL2

t

CYC2

(3)

地址

(b2)

一个

0

一个

1

一个

2

一个

3

一个

4

一个

5

t

SA

t

HA

CE

0(b2)

数据

输出(b2)

Q

2

Q

4

t

CD2

t

CD2

t

CKHZ

t

CD2

t

CKLZ

t

直流

t

CKHZ

t

CD2

t

CKLZ

(3)

(3)

t

SC

t

HC

(3)

t

CKHZ

(3)

t

CKLZ

(3)

t

CD2

一个

6

一个

6

t

直流

t

SC

t

HC

t

SC

t

HC

数据

在 "一个"

CLK

"b"

r/

W

"b"

地址

"一个"

r/

W

"一个"

CLK

"一个"

地址

"b"

非

相一致

相一致

非

相一致

相一致

有效的

t

CWDD

t

CD1

t

直流

数据

输出 "b"

5644 drw 10

有效的

有效的

t

SW

t

HW

t

SA

t

HA

t

SD

t

HD

t

HW

t

CD1

t

CCS

t

直流

t

SA

t

SW

t

HA

(6)

(6)