ADP3412

–7–

rev. 0

在哪里

f

最大值

是 这 最大 切换 频率 的 这 控制-

ler. 这 顶峰 surge 电流 比率 应当 是 审查 在-电路,

自从 这个 是 依赖 在 这 源 阻抗 的 这 5 v sup-

ply, 和 这 等效串联电阻 的 c

BST

.

延迟 电容 选择

这 延迟 电容, c

DLY

, 是 使用 至 增加 一个 额外的 延迟

当 这 低-一侧 场效应晶体管 驱动 转变 止 和 当 这 高-一侧

驱动开始 至 转变 在. 这 延迟 电容 adds 1 ns/pf 的

额外的 时间 至 这 20 ns 的 fixed 延迟.

如果 一个 延迟 电容 是 必需的, 看 为 一个 好的 质量 陶瓷的

电容 和 一个 npo 或者 cog dielectric, 或者 为 一个 好的 质量

mica 电容. 两个都 类型 的 电容 是 有 在 这 1 pF

至 100 pf 范围 和 有 极好的 温度 和 泄漏

特性.

1

2

3

4

8

7

6

5

BST

在

DLY

VCC

DRVH

SW

PGND

DRVL

U2

ADP3412

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

VID4

VID3

VID2

VID1

VCC

REF

CS

–

PWM1

VID0

竞赛

FB

CT

PWM2

CS+

PWRGND

地

U1

ADP3160

U3

ADP3412

1

2

3

4

8

7

6

5

BST

在

DLY

VCC

DRVH

SW

PGND

DRVL

C15

C14C13

C12

V

在

12V

V

在

RTN

270

F

4

os-con 16v

R

一个

60.4k

R

B

10k

C

OC

1.4nf

R

Z

1.1k

c11 c16 c17 c18 c19 c20 c21 c22

1200

F

8

os-con 2.5v

11m

等效串联电阻 (各自)

V

cc(核心)

1.1v

–

1.85v

53.4a

V

cc(核心)

RTN

Q3

FDB7030L

D1

MBR052LTI

Q5

2N3904

L2

600nH

L1

600nH

Q1

FDB7030L

Q2

FDB8030L

C10

1

F

D2

MBR052LTI

C7

15pF

C5

1

F

Z1

ZMM5236BCT

R5

2.4k

R8

330

C23

330pF

C22

1nF

C4

4.7

F

R6

10

C21

15nF

C26

4.7

F

C8

15pF

C6

1

F

C9

1

F

R7

20

R4

4m

C2

100pF

C1

150pF

R1

1k

Q4

FDB8030L

+

+

+ + + + + +

从

CPU

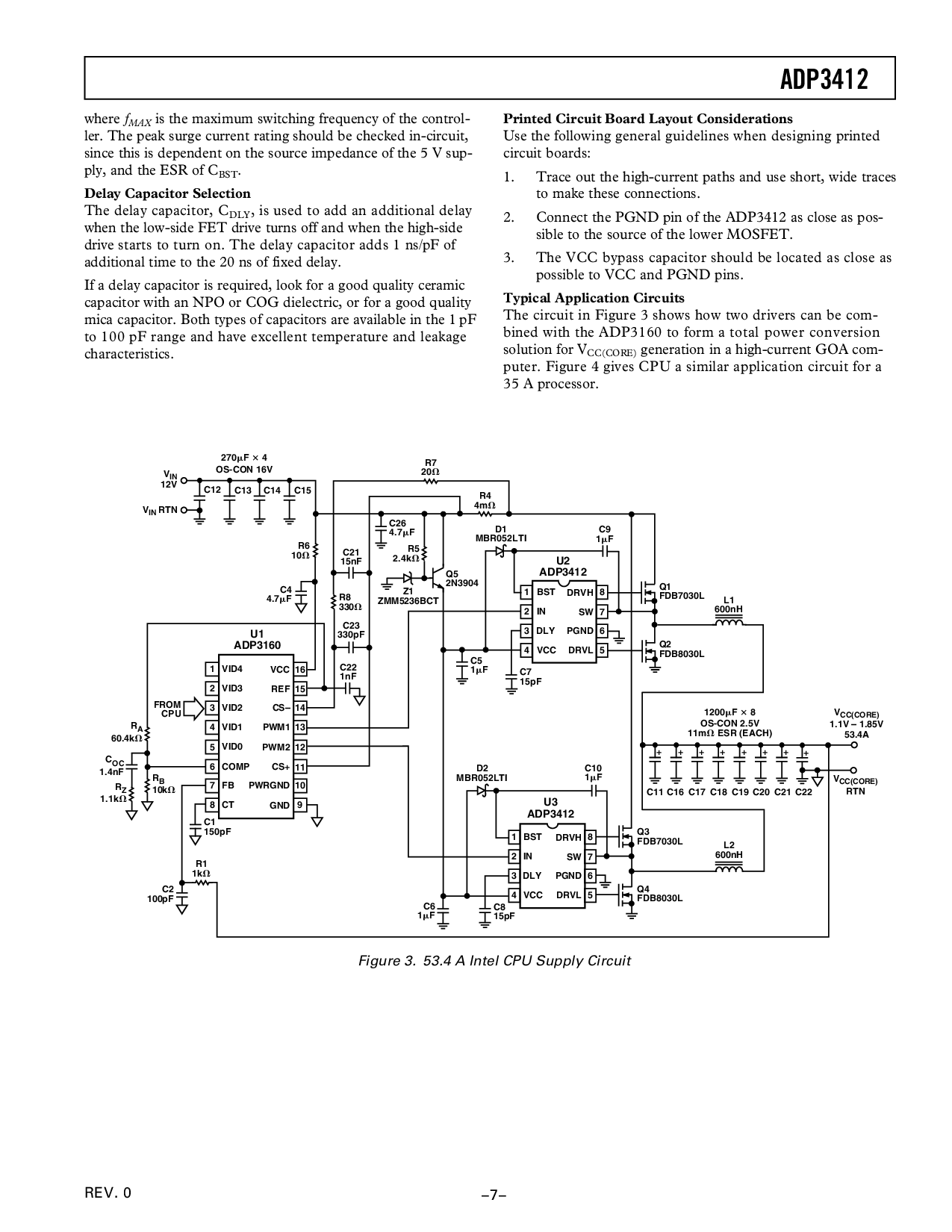

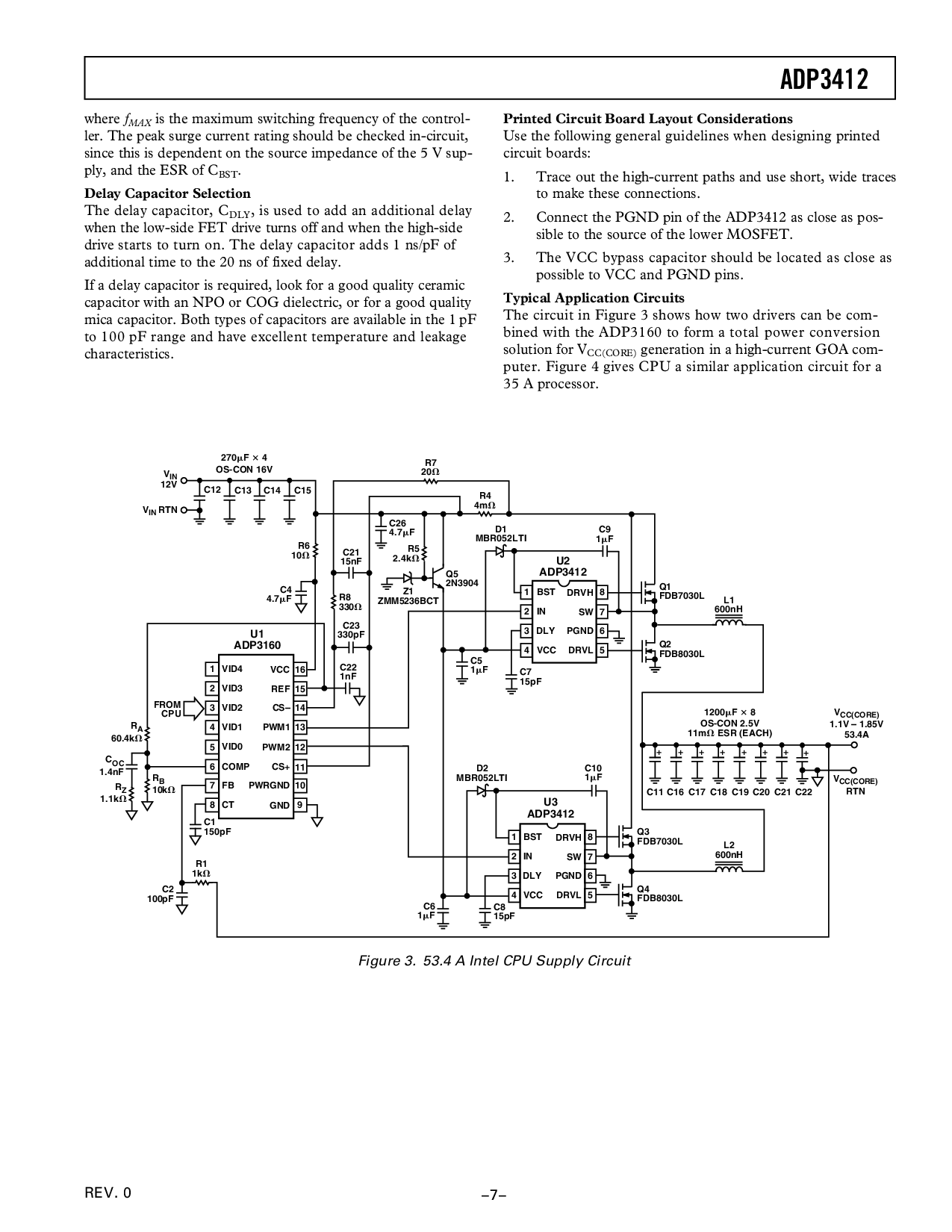

图示 3. 53.4 一个 intel cpu 供应 电路

打印 电路 板 布局 仔细考虑

使用 这 following 一般 指导原则 当 designing printed

电路 boards:

1. 查出 输出 这 高-电流 paths 和 使用 短的, 宽 查出

至 制造 这些 连接.

2. 连接 这 pgnd 管脚 的 这 adp3412 作 关闭 作 pos-

sible 至 这 源 的 这 更小的 场效应晶体管.

3. 这 vcc 绕过 电容 应当 是 located 作 关闭 作

可能 至 vcc 和 pgnd 管脚.

典型 应用 电路

这 电路 在 图示 3 显示 如何 二 驱动器 能 是 com-

bined 和 这 adp3160 至 表格 一个总的 电源 转换

解决方案 为 v

cc(核心)

一代 在 一个 高-电流 goa com-

puter. 图示 4 给 cpu 一个 类似的 应用 电路 为 一个

35 一个 处理器.