at49bv008a(t)/8192a(t)

3

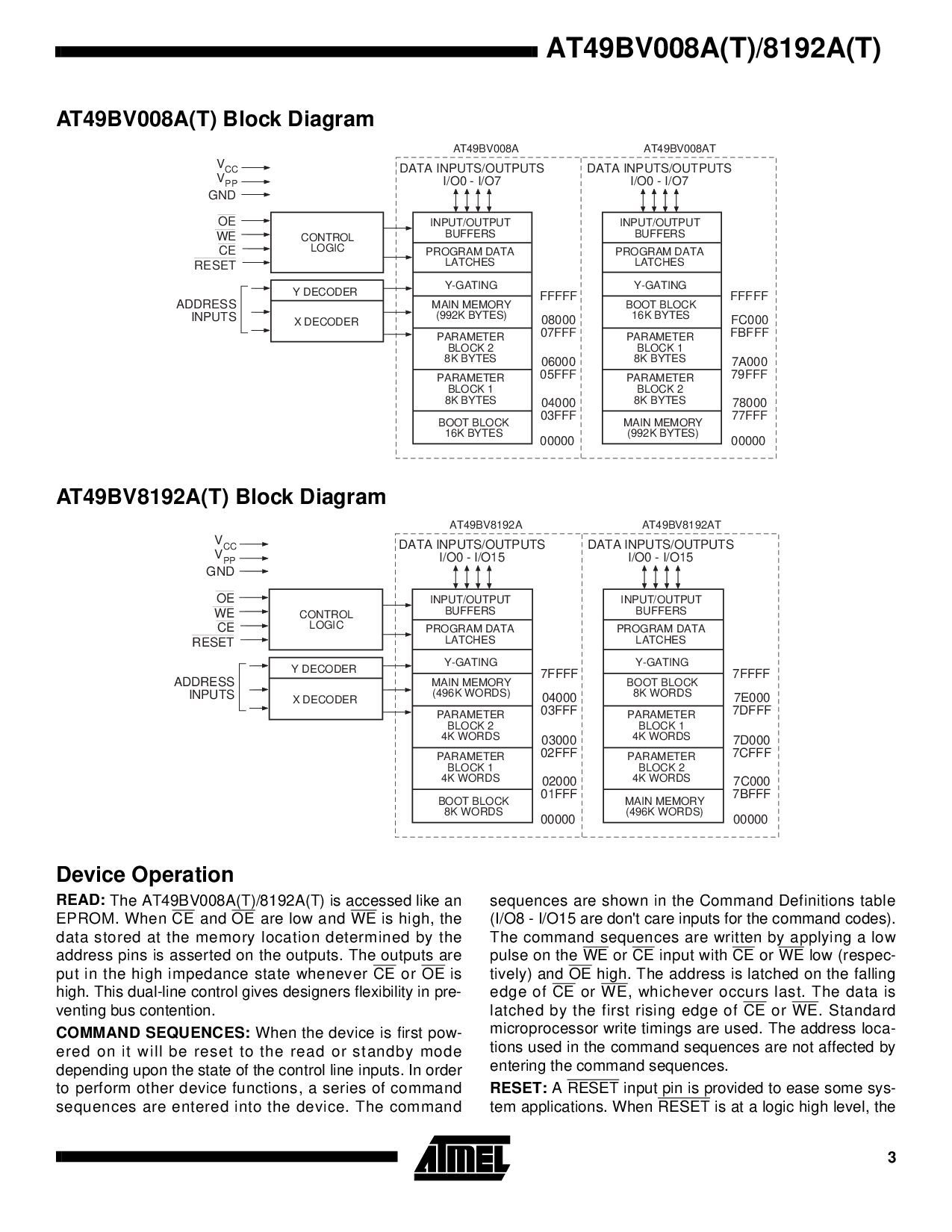

at49bv008a(t) 块 图解

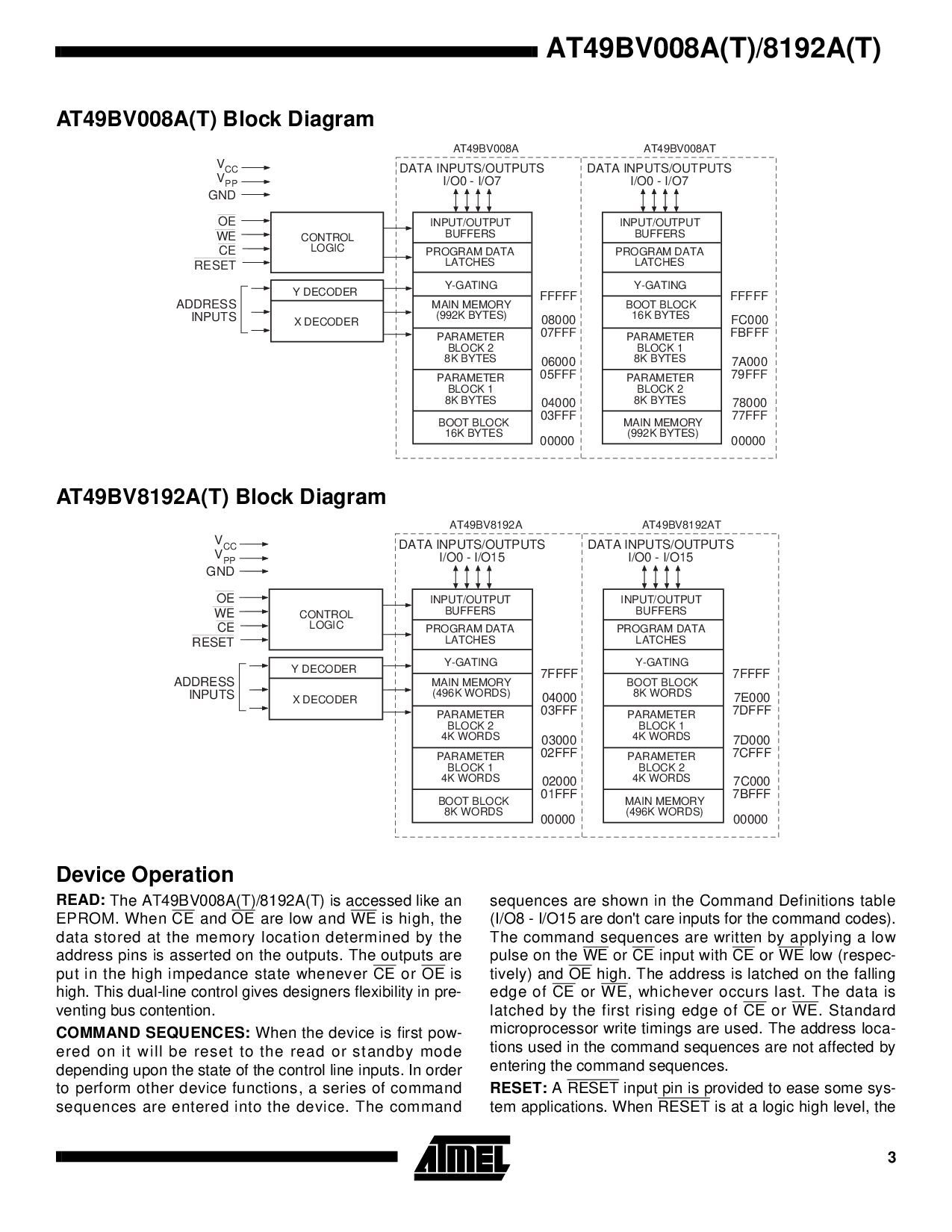

at49bv8192a(t) 块 图解

设备 运作

读:

这 at49bv008a(t)/8192a(t) 是 accessed 像 一个

非易失存储器. 当 ce

和 oe是 低 和 我们 是 高, 这

数据 贮存 在 这 记忆 location 决定 用 这

地址 管脚 是 asserted 在 这 输出. 这 输出 是

放 在 这 高 阻抗 状态 whenever ce

或者 oe是

高. 这个 双-线条 控制 给 designers flexibility 在 前-

venting 总线 contention.

command sequences:

当 这 设备 是 第一 pow-

ered 在 它 将 是 重置 至 这 读 或者 备用物品 模式

取决于 在之上 这 状态 的 这 控制 线条 输入. 在 顺序

至 执行 其它 设备 功能, 一个 序列 的 command

sequences 是 entered 在 这 设备. 这 command

sequences 是 显示 在 这 command 定义 表格

(i/o8 - i/o15 是 don't 小心 输入 为 这 command 代号).

这 command sequences 是 写 用 应用 一个 低

脉冲波 在 这 我们

或者 ce输入 和 ce或者 我们低 (respec-

tively) 和 oe

高. 这 地址 是 latched 在 这 下落

边缘 的 ce

或者 我们, whichever occurs last. 这 数据 是

latched 用 这 第一 rising 边缘 的 ce

或者 我们. 标准

微处理器 写 timings 是 使用. 这 地址 loca-

tions 使用 在 这 command sequences 是 不 影响 用

进去 这 command sequences.

重置:

一个 重置

输入 管脚 是 提供 至 使容易 一些 sys-

tem 产品. 当 重置

是 在 一个 逻辑 高 水平的, 这

V

PP

V

CC

地

OE

控制

逻辑

数据 输入/输出

i/o0 - i/o7

数据 输入/输出

i/o0 - i/o7

我们

CE

重置

地址

输入

y 解码器

输入/输出

缓存区

输入/输出

缓存区

程序 数据

LATCHES

程序 数据

LATCHES

y-gating

AT49BV008A AT49BV008AT

y-gating

FFFFF FFFFF

主要的 记忆

(992k 字节)

激励 块

16k 字节

参数

块 2

8k 字节

参数

块 1

8k 字节

参数

块 1

8k 字节

参数

块 2

8k 字节

激励 块

16k 字节

主要的 记忆

(992k 字节)

08000

07FFF

FC000

FBFFF

06000

05FFF

7A000

79FFF

x 解码器

04000

03FFF

78000

77FFF

00000 00000

V

PP

V

CC

地

OE

控制

逻辑

数据 输入/输出

i/o0 - i/o15

数据 输入/输出

i/o0 - i/o15

我们

CE

重置

地址

输入

y 解码器

输入/输出

缓存区

输入/输出

缓存区

程序 数据

LATCHES

程序 数据

LATCHES

y-gating

AT49BV8192A AT49BV8192AT

y-gating

7FFFF 7FFFF

主要的 记忆

(496k words)

激励 块

8k words

参数

块 2

4k words

参数

块 1

4k words

参数

块 1

4k words

参数

块 2

4k words

激励 块

8k words

主要的 记忆

(496k words)

04000

03FFF

7E000

7DFFF

03000

02FFF

7D000

7CFFF

x 解码器

02000

01FFF

7C000

7BFFF

00000 00000