IC42S16400

2

整体的 电路 解决方案 公司

dr034-0e 12/02/2003

icsi reserves 这 正确的 至 制造 改变 至 它的 产品 在 任何 时间 没有 注意 在 顺序 至 改进 设计 和 供应 这 是st 可能 产品. 我们 假设 非 责任 为 任何 errors

这个 将 呈现 在 这个 发行. © 版权 2000, 整体的 电路 解决方案 公司

特性

• 单独的 3.3v (

±

0.3v) 电源 供应

• 高 速 时钟 循环 时间 -6: 166mhz,

-7: 133mhz<3-3-3>

• 全部地 同步的 运作 关联 至 时钟

rising 边缘

• 可能 至 assert 随机的 column 进入 在

每 循环

• 四方形 内部的 banks contorlled 用 a12 &放大; a13

(bank 选择)

• 字节 控制 用 ldqm 和 udqm 为

IC42S16400

• 可编程序的 wrap sequence (sequential /

interleave)

• 可编程序的 burst 长度 (1, 2, 4, 8 和 全部

页)

• 可编程序的

CAS

latency (2 和 3)

• 自动 precharge 和 控制 precharge

• cbr (自动) refresh 和 自 refresh

• lvttl 兼容 输入 和 输出

• 4,096 refresh 循环 / 64ms

• burst 末端 用 burst 停止 和 precharge

command

• 包装 400mil 54-管脚 tsop-2 和 60ball(64m)

vf-bga

• 铅(含铅的)-自由 包装 是 有

描述

这 ic42s16400 是 高-速 67,108,864-位 syn-

chronous 动态 随机的-进入 memories, orga-

nized 作 1,048,576 x 16 x 4 (文字 x 位 x bank),

各自.

这 同步的 drams 达到 高-速 数据

转移 使用 这 pipeline architecture 和 时钟

频率 向上 至 166mhz 为 -6. 所有 输入 和 输出 是

同步 和 这 积极的 边缘 的 这 时钟.这

同步的 drams 是 兼容 和 低 电压

ttl (lvttl).这些 产品 是 packaged 在 54-管脚

tsop-2和 60ball(64m) vf-bga.

1m x 16 位 x 4 banks (64-mbit)

同步的 动态 内存

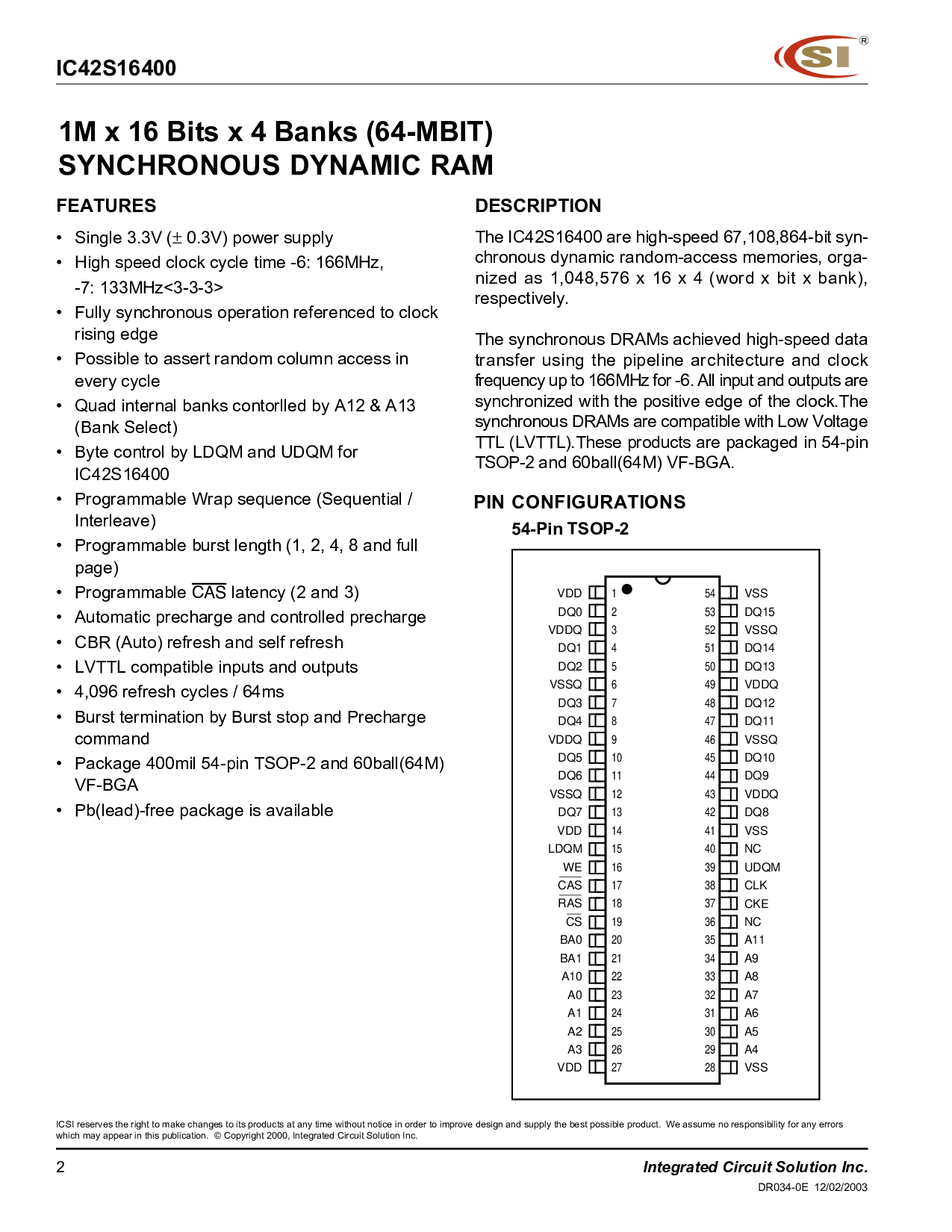

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

VDD

DQ0

VDDQ

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

VDD

LDQM

我们

CAS

RAS

CS

BA0

BA1

A10

A0

A1

A2

A3

VDD

VSS

DQ15

VSSQ

DQ14

DQ13

VDD

Q

DQ12

DQ11

VSSQ

DQ10

DQ9

VDD

Q

DQ8

VSS

NC

UDQ

M

CLK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

VSS

管脚 配置

54-管脚 tsop-2