83021AMI

www.icst.com/产品/hiperclocks.html

rev. b 六月 30, 2004

6

整体的

电路

系统, 公司

ICS83021I

1-

至

-1

2.5v 3.3v d

IFFERENTIAL

-

至

-lvcmos/lvttl t

RANSLATOR

一个

PPLICATION

I

NFORMATION

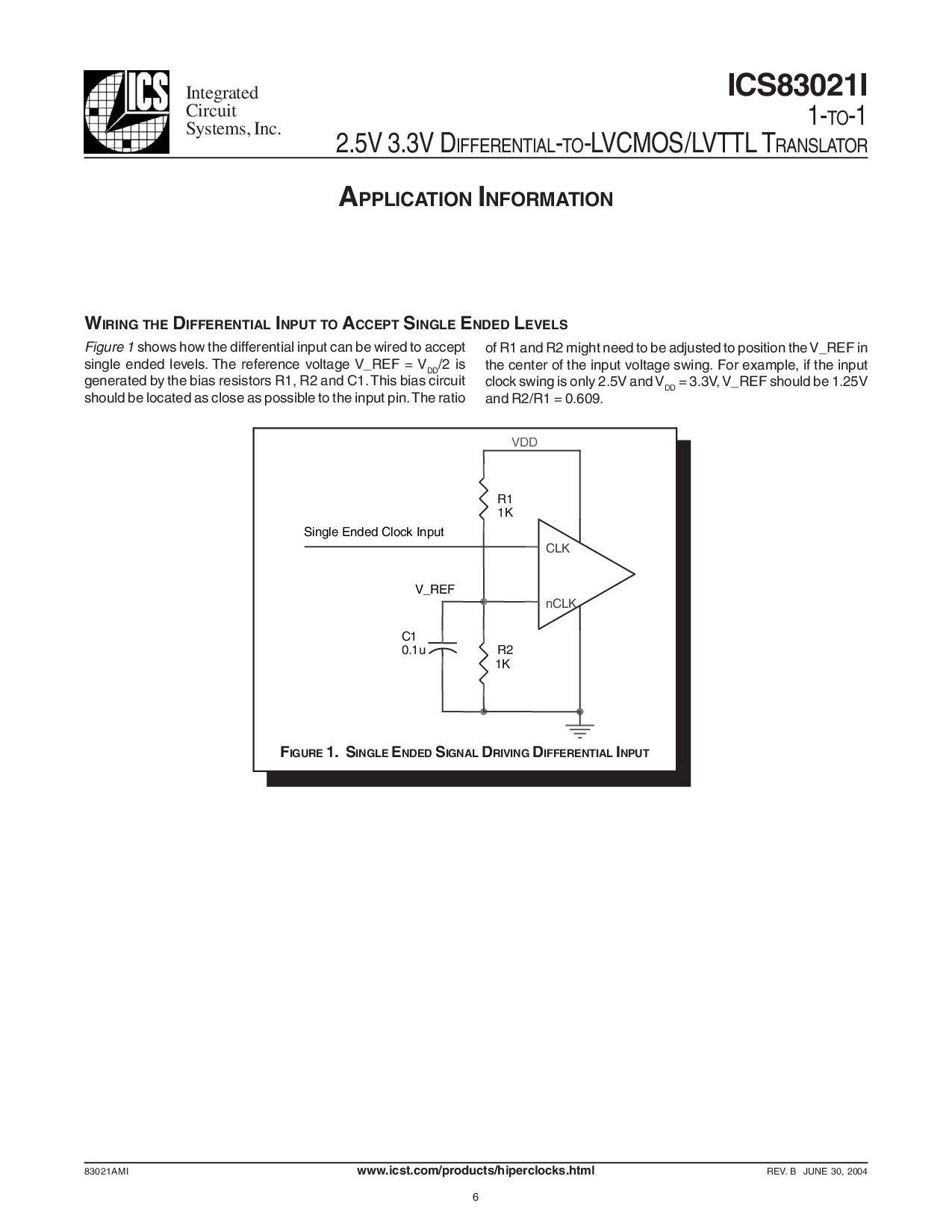

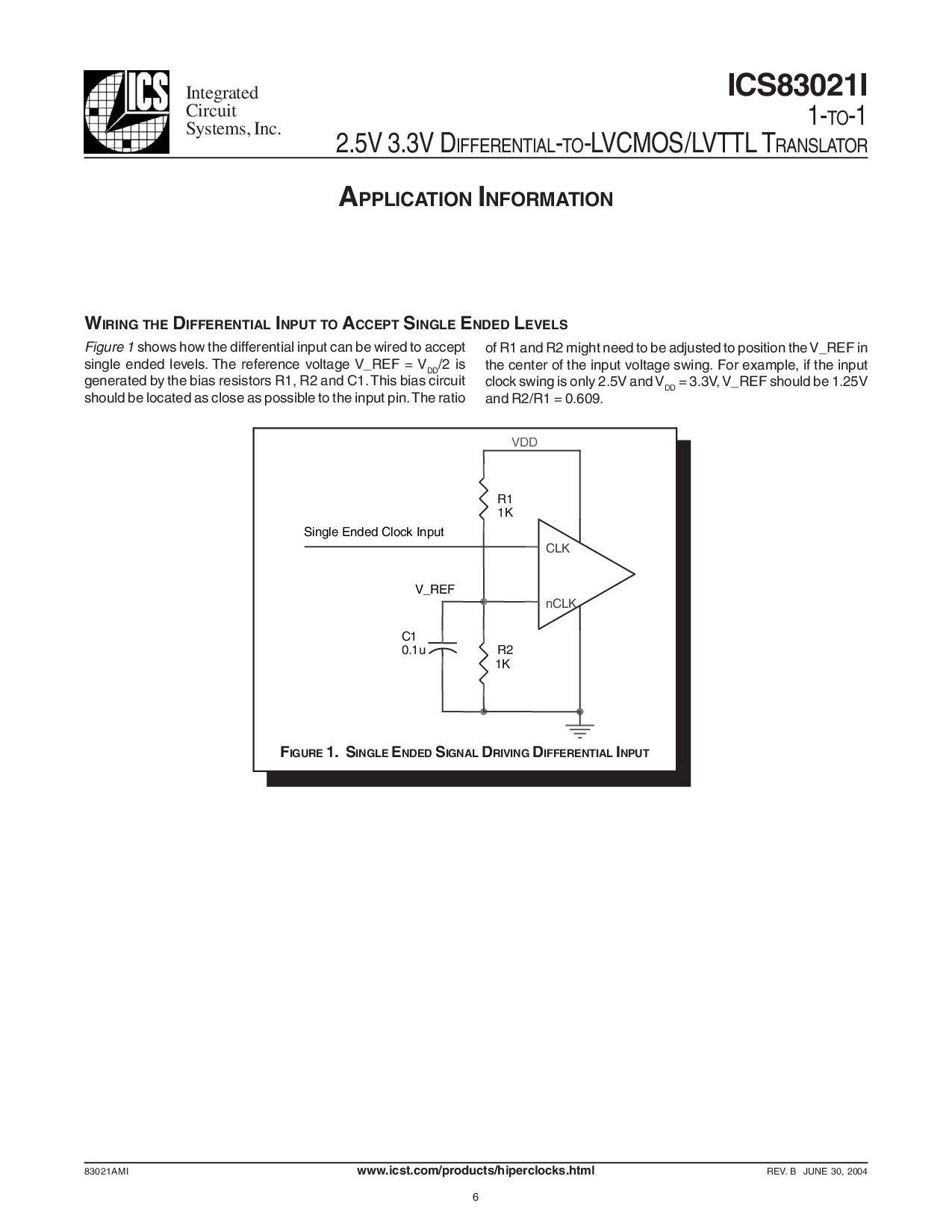

图示 1

显示 如何 这 差别的 输入 能 是 连线的 至 接受

单独的 结束 水平. 这 涉及 电压 v_ref = v

DD

/2 是

发生 用 这 偏差 电阻器 r1, r2 和 c1. 这个 偏差 电路

应当 是 located 作 关闭 作 可能 至 这 输入 管脚. 这 比率

F

IGURE

1. s

INGLE

E

NDED

S

IGNAL

D

RIVING

D

IFFERENTIAL

I

NPUT

W

IRING

这

D

IFFERENTIAL

I

NPUT

至

一个

CCEPT

S

INGLE

E

NDED

L

EVELS

的 r1 和 r2 might 需要 至 是 调整 至 位置 这 v_ref 在

这 中心 的 这 输入 电压 摆动. 为 例子, 如果 这 输入

时钟 摆动 是 仅有的 2.5v 和 v

DD

= 3.3v, v_ref 应当 是 1.25v

和 r2/r1 = 0.609.

v_ref

R1

1K

C1

0.1u

R2

1K

单独的 结束 时钟 输入

CLK

nCLK

VDD