© 1999 仙童 半导体 公司 DS009471 www.fairchildsemi.com

april 1988

修订 十一月 1999

74f109 双 jk 积极的 边缘-triggered flip-flop

74F109

双 jk

积极的 边缘-triggered flip-flop

一般 描述

这 f109 组成 的 二 高-速, 完全地 indepen-

dent 转变 clocked jk

flip-flops. 这 clocking 运作

是 独立 的 上升 和 下降 时间 的 这 时钟 波形.

这 jk

设计 准许 运作 作 一个 d-类型 flip-flop (谈及

至 f74 数据 薄板) 用 连接 这 j 和 k

输入.

异步的 输入:

低 输入 至 s

D

sets q 至 高 水平的

低 输入 至 c

D

sets q 至 低 水平的

clear 和 设置 是 独立 的 时钟

同时发生的 低 在 c

D

和 s

D

制造

两个都 q 和 q

高

订货 代号:

设备 也 有 在 录音带 和 卷轴. 具体说明 用 appending 后缀 letter “x” 至 这 订货 代号.

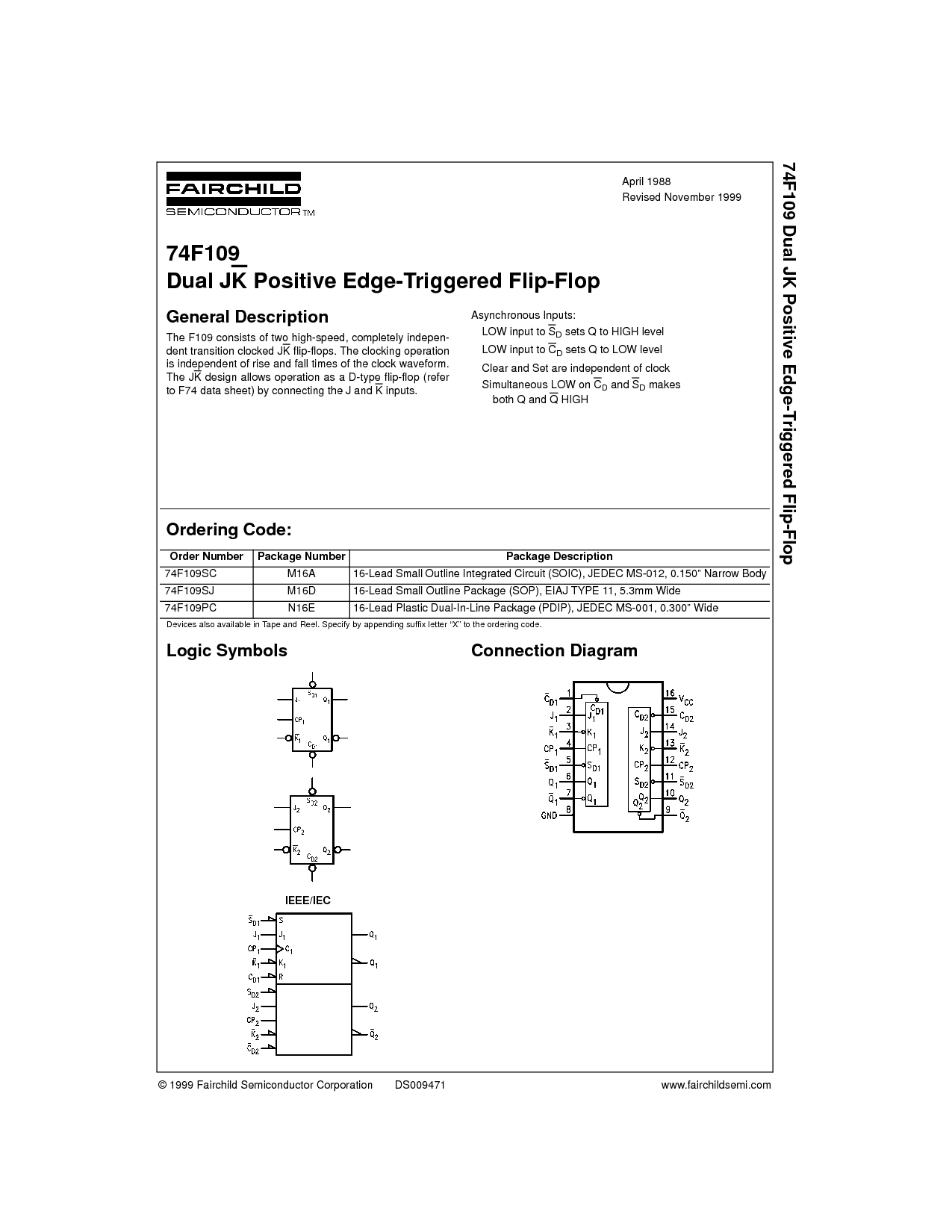

逻辑 symbols

ieee/iec

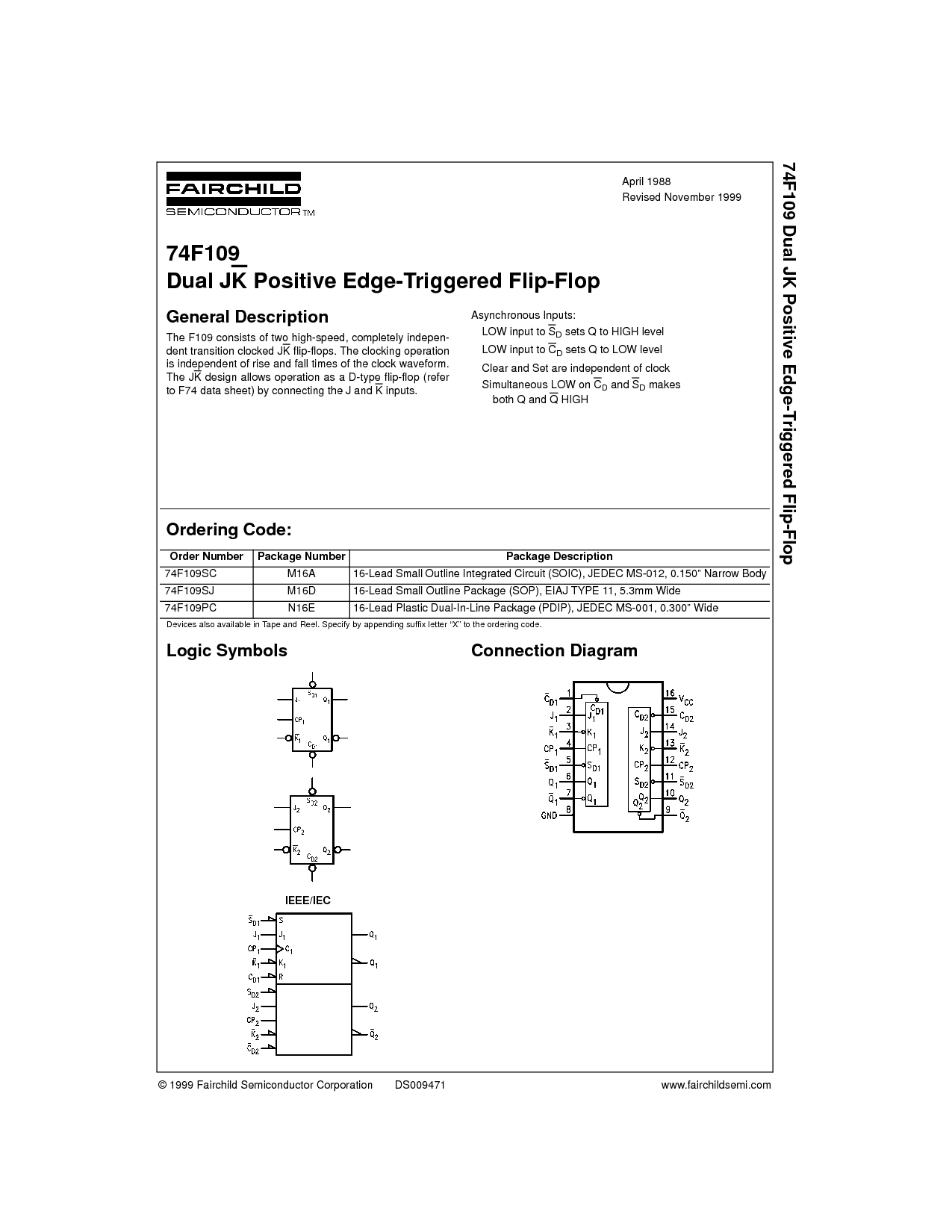

连接 图解

顺序 号码 包装 号码 包装 描述

74f109sc m16a

16-含铅的 小 外形 整体的 电路 (soic), 电子元件工业联合会 ms-012, 0.150

”

narrow 身体

74F109SJ M16D 16-含铅的 小 外形 包装 (sop), eiaj 类型 11, 5.3mm 宽

74F109PC N16E 16-含铅的 塑料 双-在-线条 包装 (pdip), 电子元件工业联合会 ms-001, 0.300

”

宽