整体的

电路

系统, 公司

一般 描述 特性

ICS9219

0931b—10/25/04

块 图解

直接 rambus™ 时钟 发生器 lite

ICS9219

是 一个 高-速 时钟 发生器 供应 400 或者

533 mhz 差别的 时钟 源 为 直接 rambus

记忆 系统.

ICS9219

takes 一个 结晶 作 一个 输入

涉及 源, 和 生产 这 差别的 输出

时钟 必需的 为 这 rambus 频道.

ICS9219

提供

一个 解决方案 为 一个 broad 范围 的 直接 rambus 记忆

产品.

ICS9219

能 是 使用 在 单独的 或者 双

rambus 途径. 一个 额外的 lvcmos 输出, 这个

提供 一个 涉及 时钟 在 这 结晶 频率 为 这

其它 系统 blocks 是 也 包含.

• 兼容 和 所有 直接 rambus

TM

为基础 ics

• 提供 差别的 时钟 源 为 直接

Rambus

记忆 系统 和 1ghz 数据 转移

比率 能力

• 循环 至 循环 jitter 是 较少 比 100ps

• 3.3v

+ 4% 供应

• lvcmos ref 时钟 @ 结晶 频率

• 输出 边缘 比率 控制 至 降低 emi

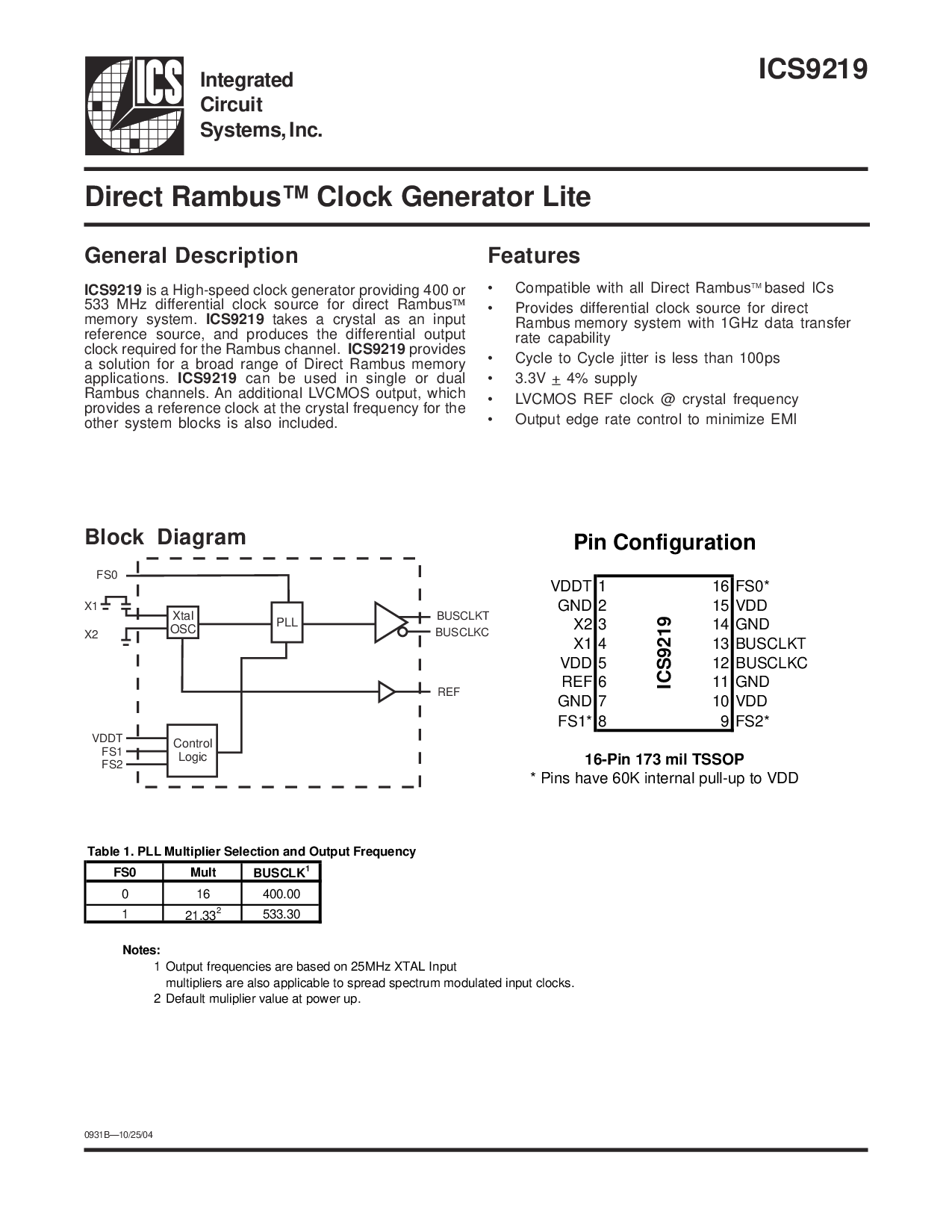

PLL

控制

逻辑

Xtal

OSC

FS0

X1

X2

FS1

VDDT

FS2

BUSCLKT

BUSCLKC

REF

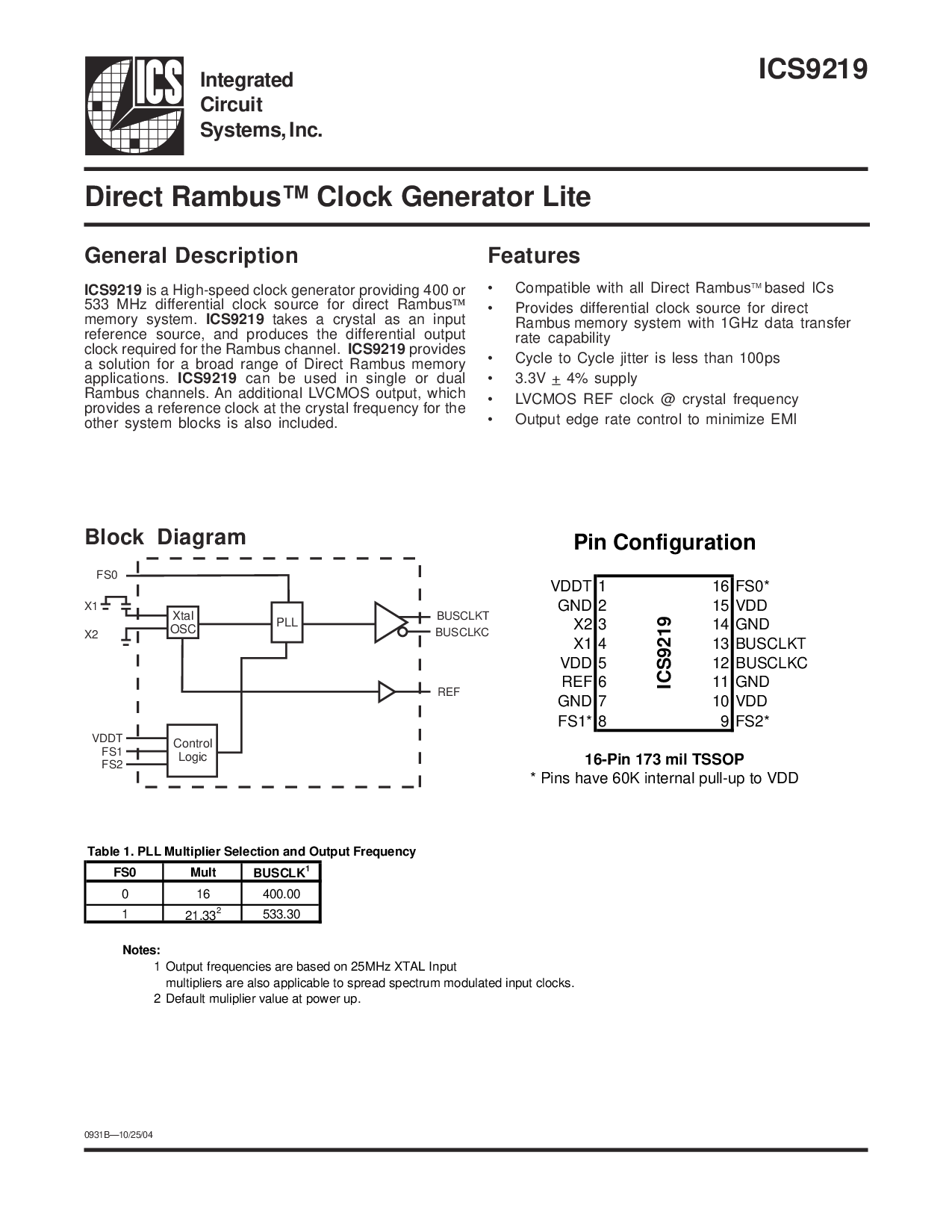

VDDT 1 16 FS0*

地 2 15 VDD

X2 3 14 地

X1 4 13 BUSCLKT

VDD 5 12 BUSCLKC

REF 6 11 地

地 7 10 VDD

FS1* 8 9 FS2*

ICS9219

管脚 配置

16-管脚 173 mil tssop

* 管脚 有 60k 内部的 拉-向上 至 vdd

表格 1. pll 乘法器 selection 和 输出 频率

FS0 Mult

BUSCLK

1

0 16 400.00

1

21.33

2

533.30

注释:

1Out

put frequencies 是 为基础 在 25mhz xtal 在put

multi

pliers 是 也 一个pplicable 至 sp读 spectrum modulated 在put clocks.

2 default muli

plier 值 在power up.