3-42

足够的 至 全部地 承担 这 电容 每 循环. 在 一个 典型

应用 在哪里 f

OSC

= 10khz 和 c = c

1

= c

2

= 10

µ

f:

自从 这 esrs 的 这 电容 是 reflected 在 这 输出

阻抗 multiplied 用 一个 因素 的 5, 一个 高 值 可以

可能地 swamp 输出 一个 低 1/f

打气

x c

1

) 期, rendering

一个 增加 在 切换 频率 或者 filter 电容

ineffective. 典型 electrolytic 电容 将 有 ESRs 作

高 作 10

Ω

.

输出 波纹

等效串联电阻 也 affects 这 波纹 电压 seen 在 这 输出. 这

总的 波纹 是 决定 用 2 电压, 一个 和 b, 作 显示 在

图示 15. 段 一个 是 这 电压 漏出 横过 这 等效串联电阻 的

C

2

在 这 instant 它 变得 从 正在 charged 用 c

1

(电流

flowing 在 c

2

) 至 正在 释放 通过 这 加载

(电流 flowing 输出 的 c

2

). 这 巨大 的 这个 电流

改变 是 2 x i

输出

, hence 这 总的 漏出 是 2 x i

输出

x

等效串联电阻

C2

v. 段 B 是 这 电压 改变 横过 C

2

在

时间 t

2

, 这 half 的 这 循环 当 c

2

供应 电流 这

加载. 这 漏出 在 B 是 I

输出

xt

2

/c

2

v. 这 顶峰-至-顶峰 波纹

电压 是 这 总 的 这些 电压 drops:

又一次, 一个 低 等效串联电阻 电容 将 结果 在 一个 高等级的

效能 输出.

paralleling 设备

任何 号码 的 icl7660s 电压 转换器 将 是

paralleled 至 减少 输出 阻抗. 这 reservoir

电容, c

2

, serves 所有 设备 当 各自 设备 需要

它的 自己的 打气 电容, c

1

. 这 resultant 输出 阻抗

将 是 大概:

cascading 设备

这 ICL7660S 将 是 倾泻 作 显示 至 生产 大

负的 multiplication 的 这 最初的 供应 电压. 不管怎样,

预定的 至 这 finite efficiency 的 各自 设备, 这 实际的 限制 是

10 设备 为 明亮的 负载. 这 输出 电压 是 defined 用:

V

输出

= -n(v

在

),

在哪里 n 是 一个 integer representing 这 号码 的 设备

倾泻. 这 结果 输出 阻抗 将 是

大概 这 weighted 总 的 这 单独的 icl7660s

R

输出

值.

changing 这 icl7660s 振荡器 频率

它 将 是 desirable 在 一些 产品, 预定的 至 噪音 或者 其它

仔细考虑, 至 改变 这 振荡器 频率. 这个 能 是

达到 simply 用 一个 的 一些 方法 描述 在下.

用 连接 这 boost 管脚 (管脚 1) 至 v+, 这 振荡器

承担 和 释放 电流 是 增加 和, hence, 这

振荡器 频率 是 增加 用 大概 3

1

/

2

时间. 这 结果 是 一个 decrease 在 这 输出 阻抗 和

波纹. 这个 是 的 主要的 重要 为 表面 挂载

产品 在哪里 电容 大小 和 费用 是 核心的.

小 电容, e.g. 0.1

µ

f, 能 是 使用 在 conjunction

和 这 Boost 管脚 在 顺序 至 达到 类似的 输出 电流

对照的 至 这 设备 自由 运动 和 C

1

=C

2

=10

µ

为

100

µ

f. (谈及 至 图表 的 输出 源 阻抗 作 一个

函数 的 振荡器 频率).

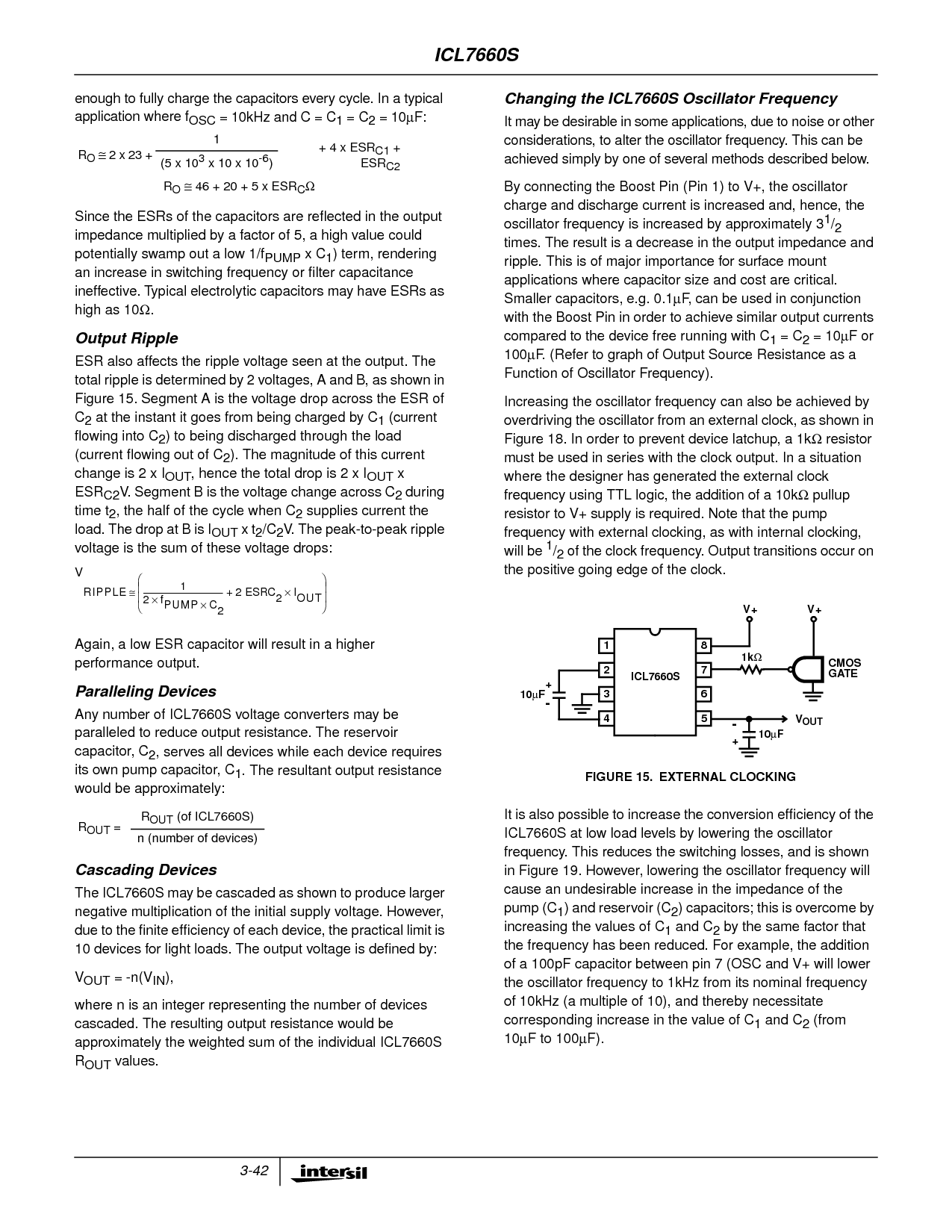

增加 这 振荡器 频率 能 也 是 达到 用

overdriving 这 振荡器 从 一个 外部 时钟, 作 显示 在

图示 18. 在 顺序 至 阻止 设备 latchup, 一个 1k

Ω

电阻

必须 是 使用 在 序列 和 这 时钟 输出. 在 一个 situation

在哪里 这 设计者 有 发生 这 外部 时钟

频率 使用 ttl 逻辑, 这 增加 的 一个 10k

Ω

pullup

电阻 至 v+ 供应 是 必需的. 便条 那 这 打气

频率 和 外部 clocking, 作 和 内部的 clocking,

将 是

1

/

2

的 这 时钟 频率. 输出 transitions 出现 在

这 积极的 going 边缘 的 这 时钟.

它 是 也 可能 至 增加 这 转换 efficiency 的 这

icl7660s 在 低 加载 水平 用 lowering 这 振荡器

频率. 这个 减少 这 切换 losses, 和 是 显示

在 图示 19. 不管怎样, lowering 这 振荡器 频率 将

导致 一个 不想要的 增加 在 这 阻抗 的 这

打气 (c

1

) 和 reservoir (c

2

) 电容; 这个 是 克服 用

增加 这 值 的 c

1

和 c

2

用 这 一样 因素 那

这 频率 有 被 减少. 为 例子, 这 增加

的 一个 100pf 电容 在 管脚 7 (osc 和 v+ 将 更小的

这 振荡器 频率 至 1khz 从 它的 名义上的 频率

的 10khz (一个 多样的 的 10), 和 因此 necessitate

相应的 增加 在 这 值 的 c

1

和 c

2

(从

10

µ

f 至 100

µ

f).

R

O

≅

2x23+

1

+ 4 x 等效串联电阻

C1

+

等效串联电阻

C2

(5 x 10

3

x 10 x 10

-6

)

R

O

≅

46 + 20 + 5 x 等效串联电阻

C

Ω

R

输出

=

R

输出

(的 icl7660s)

n (号码 的 设备)

V

波纹

1

2f

打气 C

2

×

×

--------------------------------------------

2 ESRC

2

I

输出

×

+

≅

1

2

3

4

8

7

6

5

+

-

10

µ

F

ICL7660S

V

输出

V+

+

-

10

µ

F

V+

CMOS

门

1k

Ω

图示 15. 外部 clocking

ICL7660S