dsp56f801/d

rev. 13.0

,

02/2004

© motorola, inc., 2004. 所有 权利 保留.

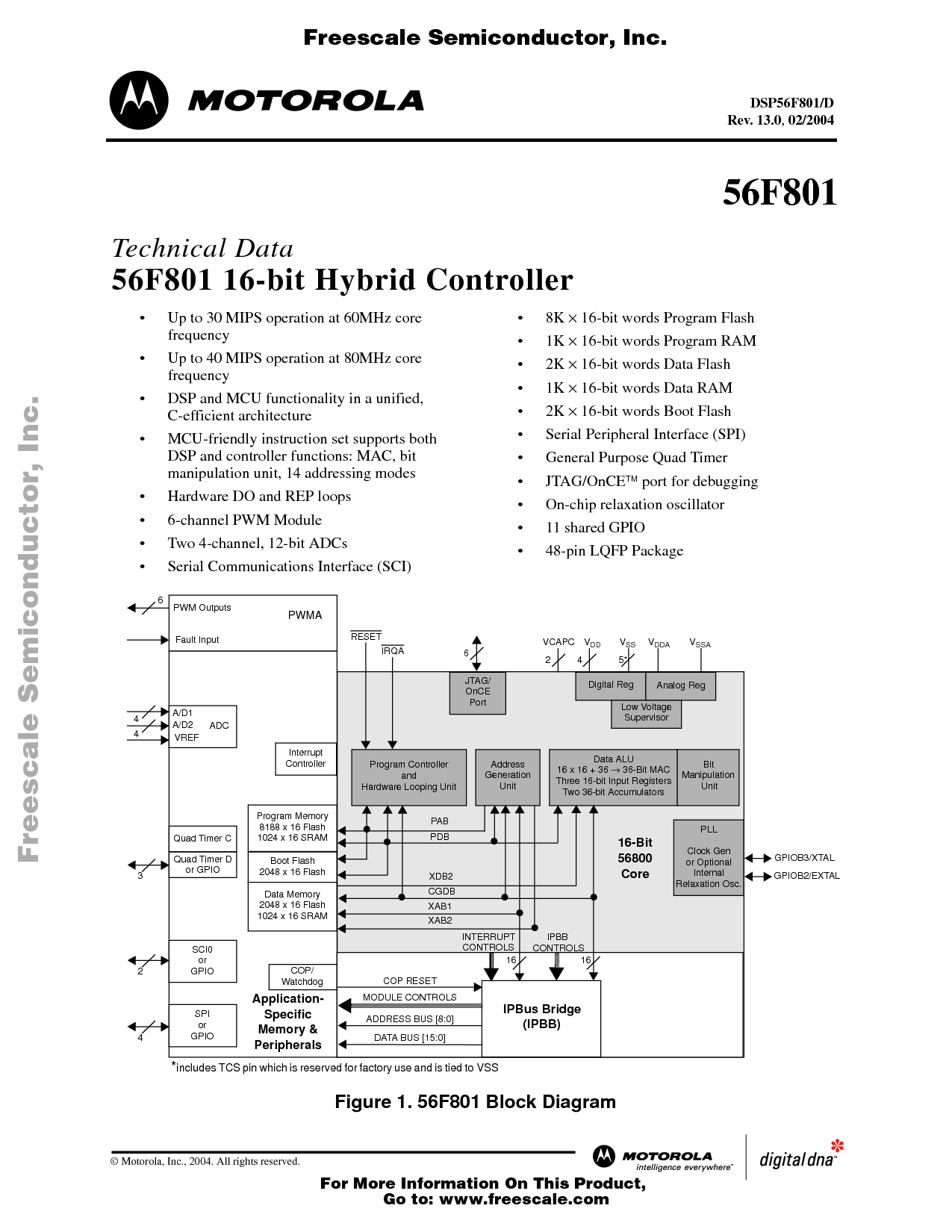

56F801

技术的 数据

56f801 16-位 混合的 控制

• 向上 至 30 mips 运作 在 60mhz 核心

频率

• 向上 至 40 mips 运作 在 80mhz 核心

频率

• dsp 和 mcu 符合实际 在 一个 unified,

c-效率高的 architecture

• mcu-friendly 操作指南 设置 支持 两个都

dsp 和 控制 功能: mac, 位

manipulation 单位, 14 寻址 模式

• 硬件 做 和 rep 循环

• 6-频道 pwm 单元

• 二 4-频道, 12-位 adcs

• 串行 communications 接口 (sci)

•8K

×

16-位 words 程序 flash

•1K

×

16-位 words 程序 内存

•2K

×

16-位 words 数据 flash

•1K

×

16-位 words 数据 内存

•2K

×

16-位 words 激励 flash

• 串行 附带的 接口 (spi)

• 一般 目的 四方形 计时器

•jtag/once

TM

端口 为 debugging

• 在-碎片 relaxation 振荡器

•11 shared gpio

• 48-管脚 lqfp 包装

图示 1. 56f801 块 图解

jtag/

OnCE

端口

数字的 reg

相似物 reg

低 电压

Supervisor

程序 控制

和

硬件 looping 单位

数据 alu

16 x 16 + 36

→

36-位 mac

三 16-位 输入 寄存器

二 36-位 accumulators

地址

一代

单位

位

Manipulation

单位

PLL

时钟 gen

或者 optional

内部的

relaxation osc.

16-位

56800

核心

PAB

PDB

XDB2

CGDB

XAB1

XAB2

gpiob3/xtal

gpiob2/extal

中断

控制

IPBB

控制

ipbus 桥

(ipbb)

单元 控制

地址 总线 [8:0]

数据 总线 [15:0]

cop 重置

重置

IRQA

应用-

明确的

记忆 &放大;

Peripherals

中断

控制

程序 记忆

8188 x 16 flash

1024 x 16 sram

激励 flash

2048 x 16 flash

数据 记忆

2048 x 16 flash

1024 x 16 sram

cop/

看门狗

SPI

或者

GPIO

SCI0

或者

GPIO

四方形 计时器 d

或者 gpio

四方形 计时器 c

一个/d1

一个/d2

模数转换器

4

2

3

4

4

6

pwm 输出

故障 输入

PWMA

16 16

VCAPC V

DD

V

SS

V

DDA

V

SSA

6

24 5*

•

•

•

•

•

•

•

•

VREF

*

包含 tcs 管脚 这个 是 保留 为 工厂 使用 和 是 系 至

VSS

F

r

e

e

s

c

一个

l

e

S

e

m

i

c

o

n

d

u

c

t

o

r

,

I

freescale 半导体, 公司

为 更多 信息 在 这个 产品,

go 至: www.freescale.com

n

c

.

.

.