初步的 产品 信息

这个 文档 包含 信息 为 一个 新 产品.

Cirrus 逻辑 reserves 这 正确的 至 modify 这个 产品 没有 注意.

1

版权

Cirrus 逻辑, 公司 2002

(所有 权利 保留)

p.o. 盒 17847, austin, 德州 78760

(512) 445 7222 传真: (512) 445 7581

http://www.cirrus.com

cs5531/32/33/34

16-位 和 24-位 ADCs 和 过激 低 噪音 PGIA

特性

Chopper Stabilized PGIA (可编程序的

增益 仪器 放大器, 1x 至 64x)

6nv/

√

Hz @ 0.1 Hz (非 1/f 噪音) 在 64x

500 pA 输入 电流 和 增益 >1

delta-sigma 相似物-至-数字的 转换器

线性 错误: 0.0007% FS

噪音 自由 决议: 向上 至 23 位

二 或者 四 频道 差别的 MUX

可称量的 输入 Span 通过 校准

±5 mV 至 差别的 ±2.5v

可称量的 V

REF

输入: 向上 至 相似物 供应

简单的 三-线 串行 接口

SPI

和 Microwire™ 兼容

施密特 触发 在 串行 时钟 (sclk)

r/w 校准 寄存器 每 频道

可选择的 文字 比率: 6.25 至 3,840 Sps

可选择的 50 或者 60 Hz 拒绝

电源 供应 配置

va+=+5v;va-=0v;vd+=+3vto+5v

va+=+2.5v;va-=-2.5v;vd+=+3vto+5v

VA+ = +3 v; VA- = -3 v; VD+ = +3 V

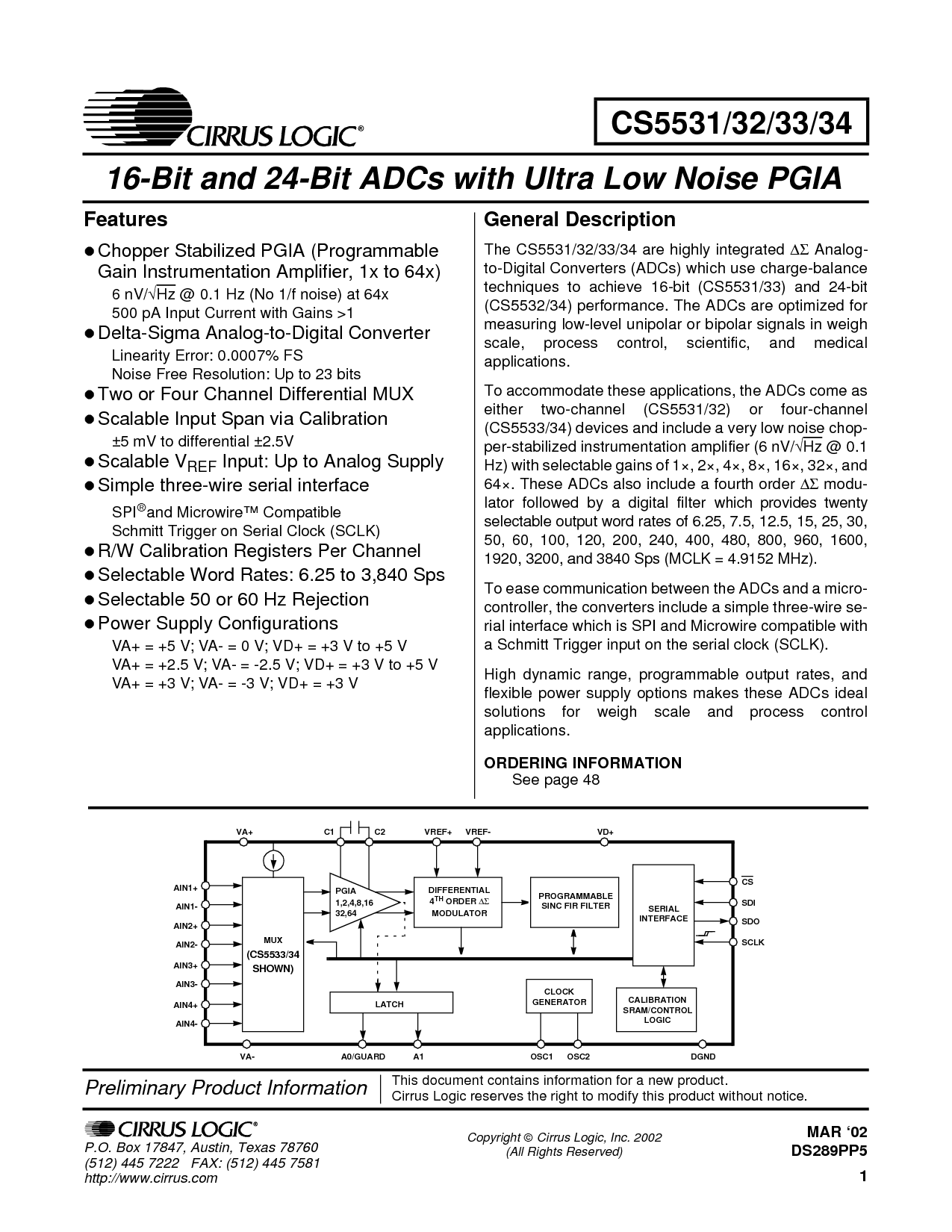

一般 描述

这 cs5531/32/33/34 是 高级地 整体的

∆Σ

相似物-

至-数字的 转换器 (adcs) 这个 使用 承担-balance

技巧 至 达到 16-位 (cs5531/33) 和 24-位

(cs5532/34) 效能. 这 ADCs 是 优化 为

测量 低-水平的 单极的 或者 双极 信号 在 weigh

规模, 处理 控制, scientific, 和 medical

产品.

至 accommodate 这些 产品, 这 ADCs 来到 作

也 二-频道 (cs5531/32) 或者 四-频道

(cs5533/34) 设备 和 包含 一个 非常 低 噪音 chop-

每-stabilized 仪器 放大器 (6 nv/

√

Hz

@0.1

hz) 和 可选择的 增益 的 1×, 2×, 4×, 8×, 16×, 32×, 和

64×. 这些 ADCs 也 包含 一个 fourth 顺序

∆Σ

modu-

lator followed 用 一个 数字的 过滤

这个 提供 twenty

可选择的 输出 文字 比率 的 6.25, 7.5, 12.5, 15, 25, 30,

50, 60, 100, 120, 200, 240, 400, 480, 800, 960, 1600,

1920, 3200, 和 3840 Sps (mclk = 4.9152 mhz).

至 使容易 交流 在 这 ADCs 和 一个 微观的-

控制, 这 转换器 包含 一个 简单的 三-线 se-

rial 接口 这个 是 SPI 和 Microwire 兼容 和

一个 施密特 触发 输入 在 这 串行 时钟 (sclk).

高 动态 范围, 可编程序的 输出 比率, 和

有伸缩性的 电源 供应 选项 制造 这些 ADCs 完美的

解决方案 为 weigh 规模 和 处理 控制

产品.

订货 信息

看 页 48

VA+ C1 C2 VREF+ vref- VD+

差别的

4

TH

顺序

∆Σ

MODULATOR

PGIA

1,2,4,8,16

可编程序的

SINC FIR 过滤

MUX

(cs5533/34

显示)

AIN1+

ain1-

AIN2+

ain2-

AIN3+

ain3-

AIN4+

ain4-

串行

接口

获得

时钟

发生器

校准

sram/控制

逻辑

DGND

CS

SDI

SDO

SCLK

OSC2OSC1A1a0/守卫va-

32,64

三月 ‘02

DS289PP5