1

128mb: x32 sdram micron 技术, inc., reserves 这 正确的 至 改变 产品 或者 规格 没有 注意.

128mbsdramx32_d.p65 – rev. d; pub. 6/02 ©2002, micron 技术, 公司

128mb: x32

SDRAM

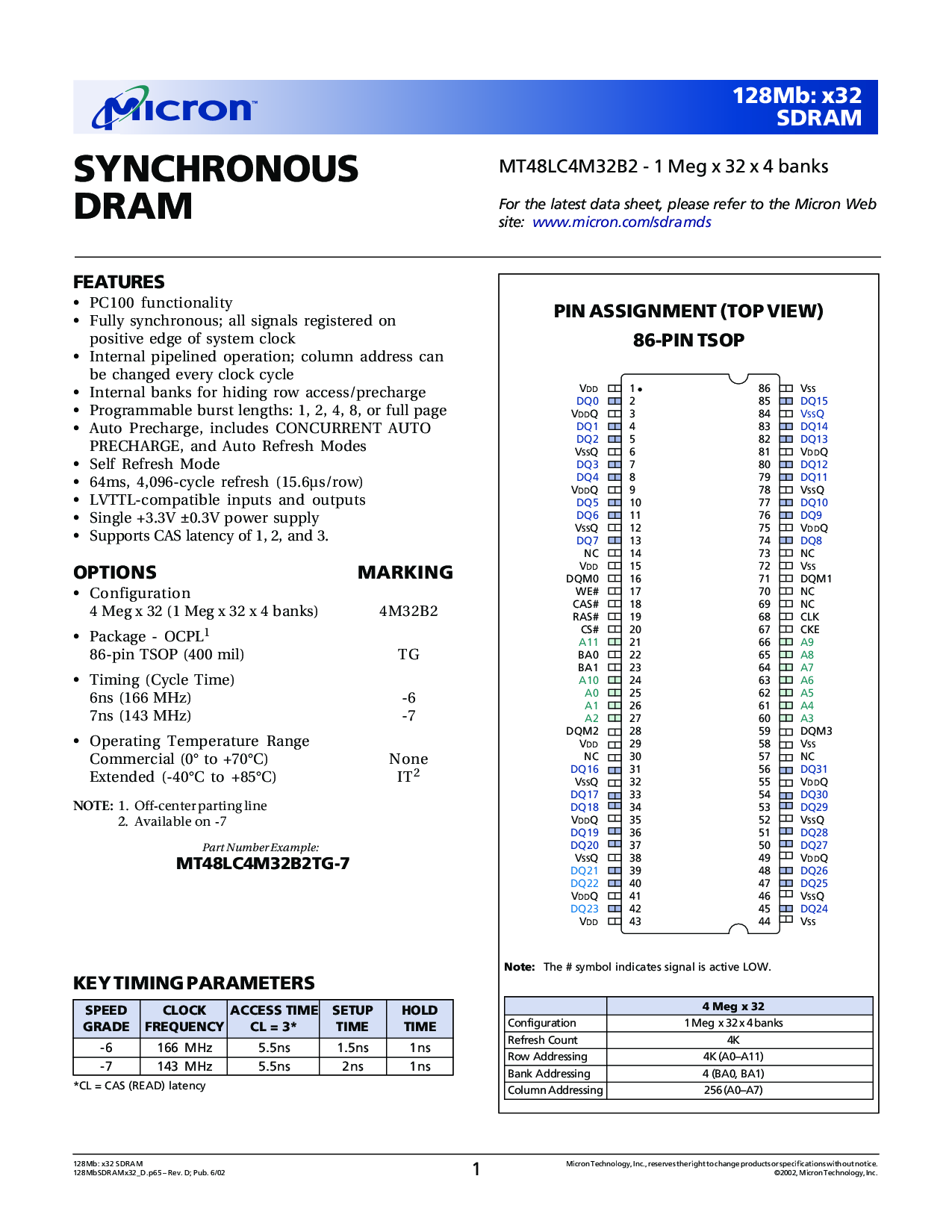

4 meg x 32

配置 1meg x 32 x 4 banks

refresh 计数 4K

行 寻址 4k (a0–a11)

bank 寻址 4 (ba0, ba1)

column 寻址 256 (a0–a7)

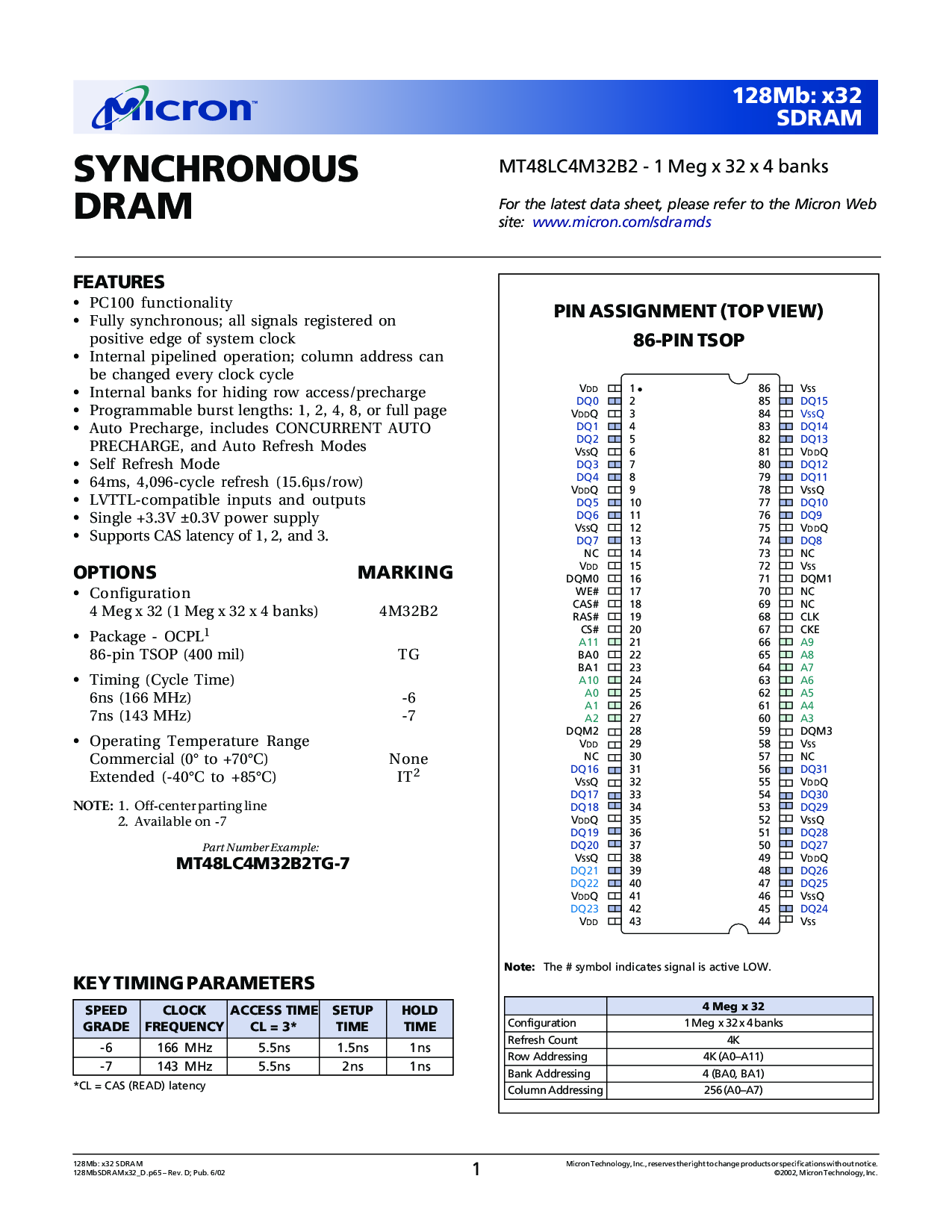

管脚 分派 (顶 视图)

86-管脚 tsop

特性

• pc100 符合实际

• 全部地 同步的; 所有 信号 注册 在

积极的 边缘 的 系统 时钟

• 内部的 pipelined 运作; column 地址 能

是 changed 每 时钟 循环

• 内部的 banks 为 hiding 行 进入/precharge

• 可编程序的 burst 长度: 1, 2, 4, 8, 或者 全部 页

• 自动 precharge, 包含 concurrent 自动

precharge, 和 自动 refresh 模式

• 自 refresh 模式

• 64ms, 4,096-循环 refresh (15.6µs/行)

• lvttl-兼容 输入 和 输出

• 单独的 +3.3v ±0.3v 电源 供应

• 支持 cas latency 的 1, 2, 和 3.

选项 标记

• 配置

4 meg x 32 (1 meg x 32 x 4 banks) 4M32B2

• 包装 - ocpl

1

86-管脚 tsop (400 mil) TG

• 定时 (循环 时间)

6ns (166 mhz) -6

7ns (143 mhz) -7

• 运行 温度 范围

商业的 (0° 至 +70°c) 毫无

扩展 (-40°c 至 +85°c) 它

2

便条:

1. 止-中心 parting 线条

2. 有 在 -7

部分 号码 例子:

mt48lc4m32b2tg-7

便条:

这 # 标识 indicates 信号 是 起作用的 低.

V

DD

DQ0

V

DD

Q

DQ1

DQ2

V

SS

Q

DQ3

DQ4

V

DD

Q

DQ5

DQ6

V

SS

Q

DQ7

NC

V

DD

DQM0

WE#

CAS#

RAS#

CS#

A11

BA0

BA1

A10

A0

A1

A2

DQM2

V

DD

NC

DQ16

V

SS

Q

DQ17

DQ18

V

DD

Q

DQ19

DQ20

V

SS

Q

DQ21

DQ22

V

DD

Q

DQ23

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

V

SS

DQ15

V

SS

Q

DQ14

DQ13

V

DD

Q

DQ12

DQ11

V

SS

Q

DQ10

DQ9

V

DD

Q

DQ8

NC

V

SS

DQM1

NC

NC

CLK

CKE

A9

A8

A7

A6

A5

A4

A3

DQM3

V

SS

NC

DQ31

V

DD

Q

DQ30

DQ29

V

SS

Q

DQ28

DQ27

V

DD

Q

DQ26

DQ25

V

SS

Q

DQ24

V

SS

同步的

DRAM

mt48lc4m32b2 - 1 meg x 32 x 4 banks

为 这 最新的 数据 薄板, 请 谈及 至 这 micron 网

站点: www.micron.com/sdramds

关键 定时 参数

速 时钟 进入时间 建制 支撑

等级 频率 cl = 3* 时间 时间

-6 166 mhz 5.5ns 1.5ns 1ns

-7 143 mhz 5.5ns 2ns 1ns

*cl = cas (读) latency