4-35

cdp1853,

CDP1853C

n-位 1 的 8 解码器

描述

这 cdp1853 和 cdp1853c 是 1 的 8 decoders 设计 为

使用 在 一般 目的 微处理器 系统. 这些

设备, 这个 是 functionally 完全同样的, 是 specifically

设计 为 使用 作 gated n-位 decoders 和 接口 直接地

和 这 1800-序列 微处理器 没有 额外的 混合-

nents. 这 cdp1853 有 一个 推荐 运行 电压

范围 的 4v 至 10.5v, 和 这 cdp1853c 有 一个 推荐

运行 电压 范围 的 4v 至 6.5v.

当 碎片 使能 (ce) 是 高, 这 选择 输出 将 是

真实 (高) 从 这 trailing 边缘 的 时钟 一个 (高-至-低 tran-

sition) 至 这 trailing 边缘 的 时钟 b (高-至-低 转变).

所有 输出 将 是 低 当 这 设备 是 不 选择 (ce = 0)

和 在 情况 的 时钟 一个 和 时钟 b 作 显示 在

图示 2. 这 cdp1853 输入 n0, n1, n2, 时钟 a, 和

时钟 b 是 连接 至 一个 1800-序列 微处理器 输出-

puts n0, n1, n2, tpa, 和 tpb respectively, 当 使用 至

decode i/o commands 作 显示 在 图示 5. 这 碎片

使能 (ce) 输入 提供 这 能力 为 多样的 水平 的

解码 作 显示 在 图示 6.

这 cdp1853 能 也 是 使用 作 一个 一般 1 的 8 解码器 为

i/o 和 记忆 系统 产品 作 显示 在 图示 4.

这 cdp1853 和 cdp1853c 是 有提供的 在 密封的 16-含铅的

双-在-线条 陶瓷的 (d suffix) 和 塑料 (e suffix) packages.

特性

• 提供 直接 控制 的 向上 至 7 输入 和 7 输出

设备

• 碎片 使能 (ce) 准许 容易 expansion 为 multi-

水平的 i/o 系统

订货 信息

包装 温度 范围 5V 10V

pkg.

非.

PDIP -40

o

c 至 +85

o

C CDP1853CE CDP1853E e16.3

烧-在 CDP1853CEX - e16.3

SBDIP -40

o

c 至 +85

o

C CDP1853CD CDP1853D d16.3

烧-在 CDP1853CDX - d16.3

march 1997

文件 号码

1189.2

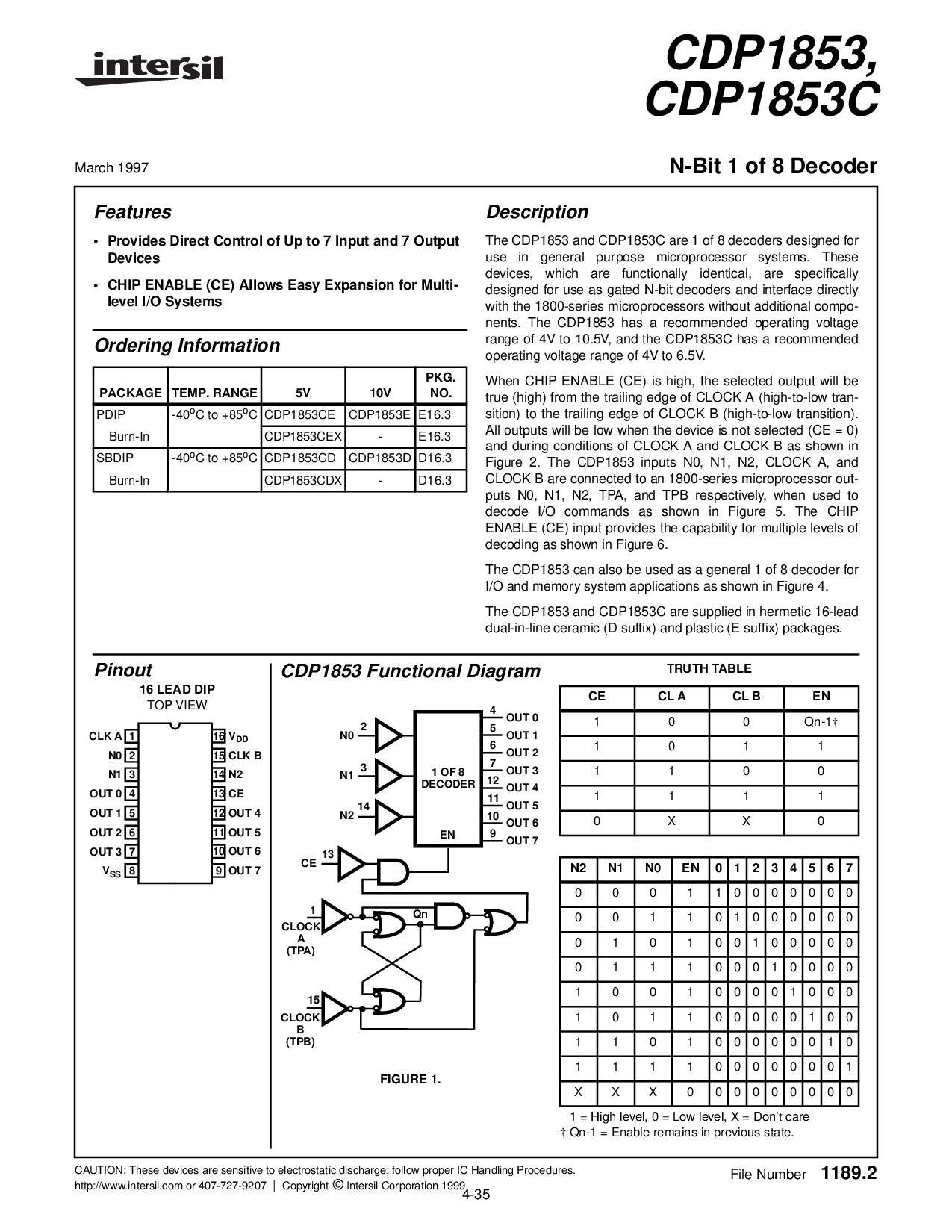

引脚

16 含铅的 插件

顶 视图

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

clk 一个

N0

N1

输出 0

输出 1

输出 2

V

SS

输出 3

V

DD

N2

CE

输出 4

输出 5

输出 6

输出 7

clk b

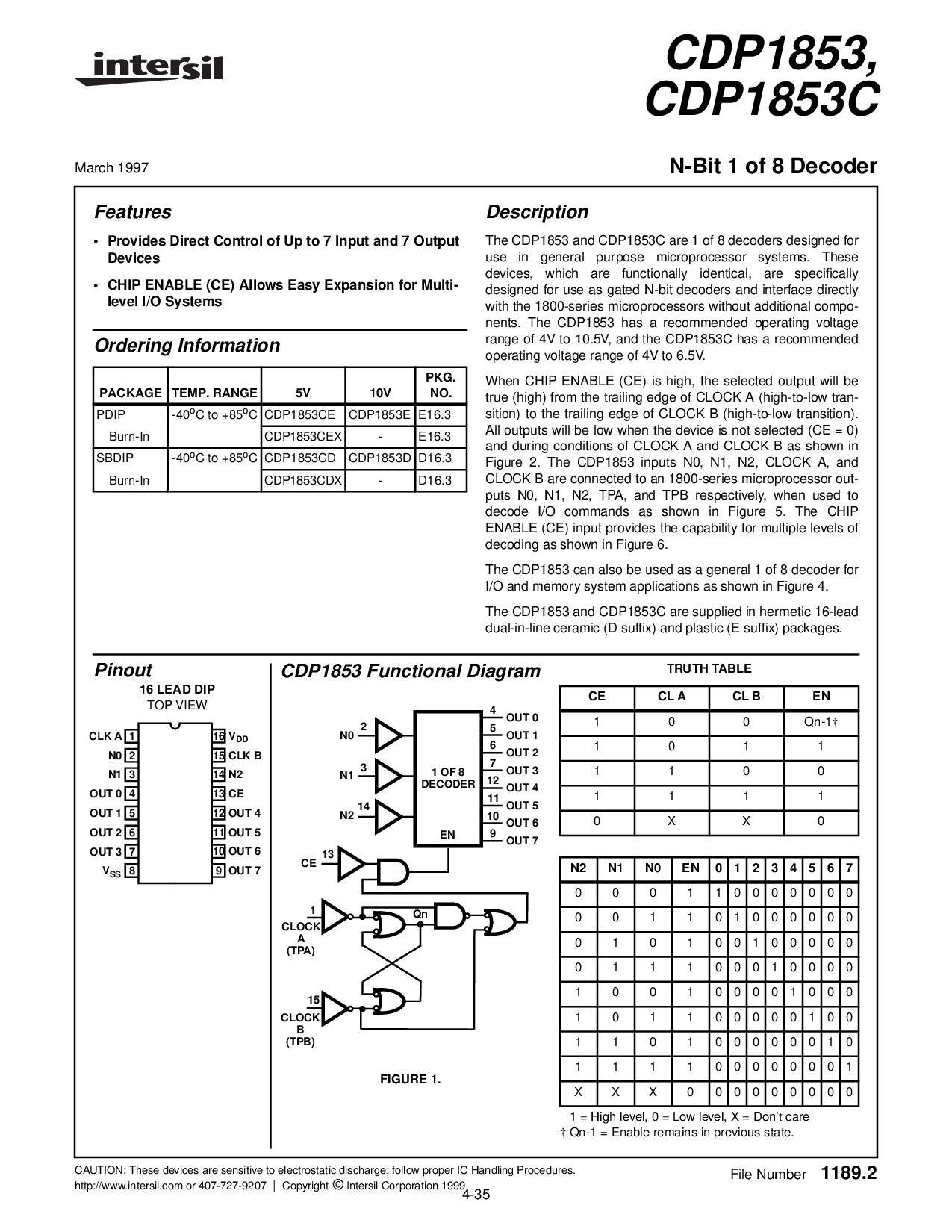

cdp1853 函数的 图解

图示 1.

Qn

4

5

6

7

12

11

10

9

1 的 8

解码器

输出 0

输出 1

输出 2

输出 3

输出 4

输出 5

输出 6

输出 7

2

3

14

N0

N1

N2

13

CE

1

15

时钟

一个

时钟

B

(tpa)

(tpb)

EN

真实 表格

1 = 高 水平的, 0 = 低 水平的, x = don’t 小心

†

qn-1 = 使能 仍然是 在 previous 状态.

CE cl 一个 cl b EN

1 0 0 qn-1

†

1011

1100

1111

0XX0

N2 N1 N0 EN 01234567

000110000000

001101000000

010100100000

011100010000

100100001000

101100000100

110100000010

111100000001

X X X 0 00000000

提醒: 这些 设备 是 敏感的 至 静电的 释放; follow 恰当的 ic 处理 程序.

http://www.intersil.com 或者 407-727-9207

|

版权

©

intersil 公司 1999