rev. 0

信息 陈设 用 相似物 设备 是 相信 至 是 精确 和

可依靠的. 不管怎样, 非 责任 是 assumed 用 相似物 设备 为 它的

使用, 也不 为 任何 infringements 的 专利权 或者 其它 权利 的 第三 部

这个 将 结果 从 它的 使用. 非 执照 是 准予 用 牵涉 或者

否则 下面 任何 专利权 或者 专利权 权利 的 相似物 设备.

一个

ad5303/ad5313/ad5323*

一个 技术 方法, p.o. 盒 9106, norwood, 毫安 02062-9106, 美国

电话: 781/329-4700 world 宽 网 站点: http://www.相似物.com

传真: 781/326-8703 © 相似物 设备, inc., 1999

+2.5 v 至 +5.5 v, 230

一个, 双 栏杆-至-栏杆

电压 输出 8-/10-/12-位 dacs

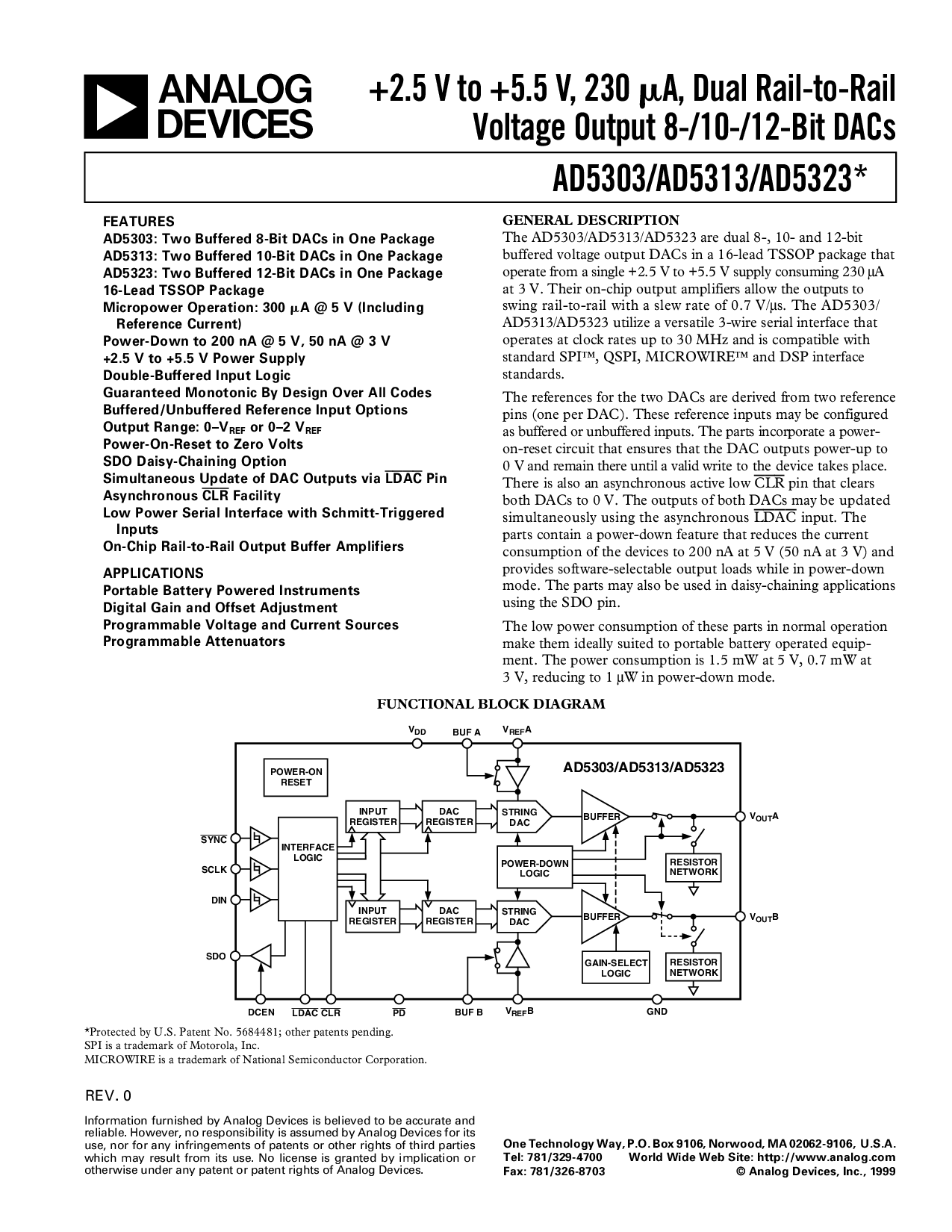

函数的 块 图解

缓存区

电源-向下

逻辑

电阻

网络

STRING

DAC

ad5303/ad5313/ad5323

V

输出

一个

V

输出

B

V

DD

V

REF

一个

V

REF

B

DAC

寄存器

DAC

寄存器

>

同步

SCLK

DIN

地

buf 一个

SDO

CLR

buf b

STRING

DAC

DCEN

LDAC

电源-在

重置

PD

缓存区

增益-选择

逻辑

电阻

网络

输入

寄存器

输入

寄存器

接口

逻辑

特性

ad5303: 二 缓冲 8-位 dacs 在 一个 包装

ad5313: 二 缓冲 10-位 dacs 在 一个 包装

ad5323: 二 缓冲 12-位 dacs 在 一个 包装

16-含铅的 tssop 包装

微小功率 运作: 300

一个 @ 5 v (包含

涉及 电流)

电源-向下 至 200 na @ 5 v, 50 na @ 3 v

+2.5 v 至 +5.5 v 电源 供应

翻倍-缓冲 输入 逻辑

有保证的 monotonic 用 设计 在 所有 代号

缓冲/unbuffered 涉及 输入 选项

输出 范围: 0–v

REF

或者 0–2 v

REF

电源-在-重置 至 零 伏特

sdo daisy-chaining 选项

同时发生的 更新 的 dac 输出 通过

LDAC

管脚

异步的

CLR

Facility

低 电源 串行 接口 和 施密特-triggered

输入

在-碎片 栏杆-至-栏杆 输出 缓存区 放大器

产品

可携带的 电池 powered 器械

数字的 增益 和 补偿 调整

可编程序的 电压 和 电流 来源

可编程序的 attenuators

一般 描述

这 ad5303/ad5313/ad5323 是 双 8-, 10- 和 12-位

缓冲 电压 输出 dacs 在 一个 16-含铅的 tssop 包装 那

运作 从 一个 单独的 +2.5 v 至 +5.5 v 供应 consuming 230

µ

一个

在 3 v. 它们的 在-碎片 输出 放大器 准许 这 outputs 至

摆动 栏杆-至-栏杆 和 一个 回转 比率 的 0.7 v/

µ

s. 这 ad5303/

ad5313/ad5323 utilize 一个 多功能的 3-线 串行 接口 那

运作 在 时钟 比率 向上 至 30 mhz 和 是 兼容 和

标准 spi™, qspi, microwire™ 和 dsp 接口

standards.

这 references 为 这 二 dacs 是 获得 从 二 涉及

管脚 (一个 每 dac). 这些 涉及 输入 将 是 配置

作 缓冲 或者 unbuffered 输入. 这 部分 包含 一个 电源-

在-重置 电路 那 确保 那 这 dac 输出 电源-向上 至

0 v 和 仍然是 那里 直到 一个 有效的 write 至 这 设备 takes 放置.

那里 是 也 一个 异步的 起作用的 低

CLR

管脚 那 clears

两个都 dacs 至 0 v. 这 输出 的 两个都 dacs 将 是updated

同时发生地 使用 这 异步的

LDAC

输入. 这

部分 包含 一个 电源-向下 特性 那 减少 这 电流

消耗量 的 这 设备 至 200 na 在 5 v (50 na 在 3 v) 和

提供 软件-可选择的 输出 负载 当 在 电源-向下

模式. 这 部分 将 也 是 使用 在 daisy-chaining 产品

使用 这 sdo 管脚.

这 低 电源 消耗量 的 这些 部分 在 正常的 运作

制造 它们 ideally suited 至 可携带的 电池 运作 配备-

ment. 这 电源 消耗量 是 1.5 mw 在 5 v, 0.7 mw 在

3 v, 减少 至 1

µ

w 在 电源-向下 模式.

*protected 用 u.s. 专利权 非. 5684481; 其它 专利权 pending.

spi 是 一个 商标 的 motorola, 公司

microwire 是 一个 商标 的 国家的 半导体 公司.