1

数据 薄板 acquired 从 harris 半导体

SCHS128C

特性

• 缓冲 输入

• 典型 传播 延迟: 8ns 在 v

CC

= 5v,

C

L

= 15pf, t

一个

= 25

o

C

• 输出 (在 温度 范围)

- 标准 输出 . . . . . . . . . . . . . . . 10 lsttl 负载

- 总线 驱动器 输出 . . . . . . . . . . . . . 15 lsttl 负载

• 宽 运行 温度 范围 . . . -55

o

c 至 125

o

C

• 保持平衡 传播 延迟 和 转变 时间

• significant 电源 减少 对照的 至 lsttl

逻辑 ics

• hc 类型

- 2v 至 6v 运作

- 高 噪音 免除: n

IL

= 30%, n

IH

= 30% 的 v

CC

在 v

CC

= 5v

• hct 类型

- 4.5v 至 5.5v 运作

- 直接 lsttl 输入 逻辑 兼容性,

V

IL

= 0.8v (最大值), v

IH

= 2v (最小值)

- cmos 输入 兼容性, i

l

≤

1

µ

一个 在 v

OL

, v

OH

描述

这 ’HC10 和 ’HCT10 逻辑 门 utilize 硅 门 CMOS

技术 至 达到 运行 speeds 类似的 至 LSTTL

门 和 这 低 电源 消耗量 的 标准 CMOS

整体的 电路. 所有 设备 有 这 能力 至 驱动 10

LSTTL 负载. 这 HCT 逻辑 家族 是 functionally 管脚

兼容 和 这 标准 ls 逻辑 家族.

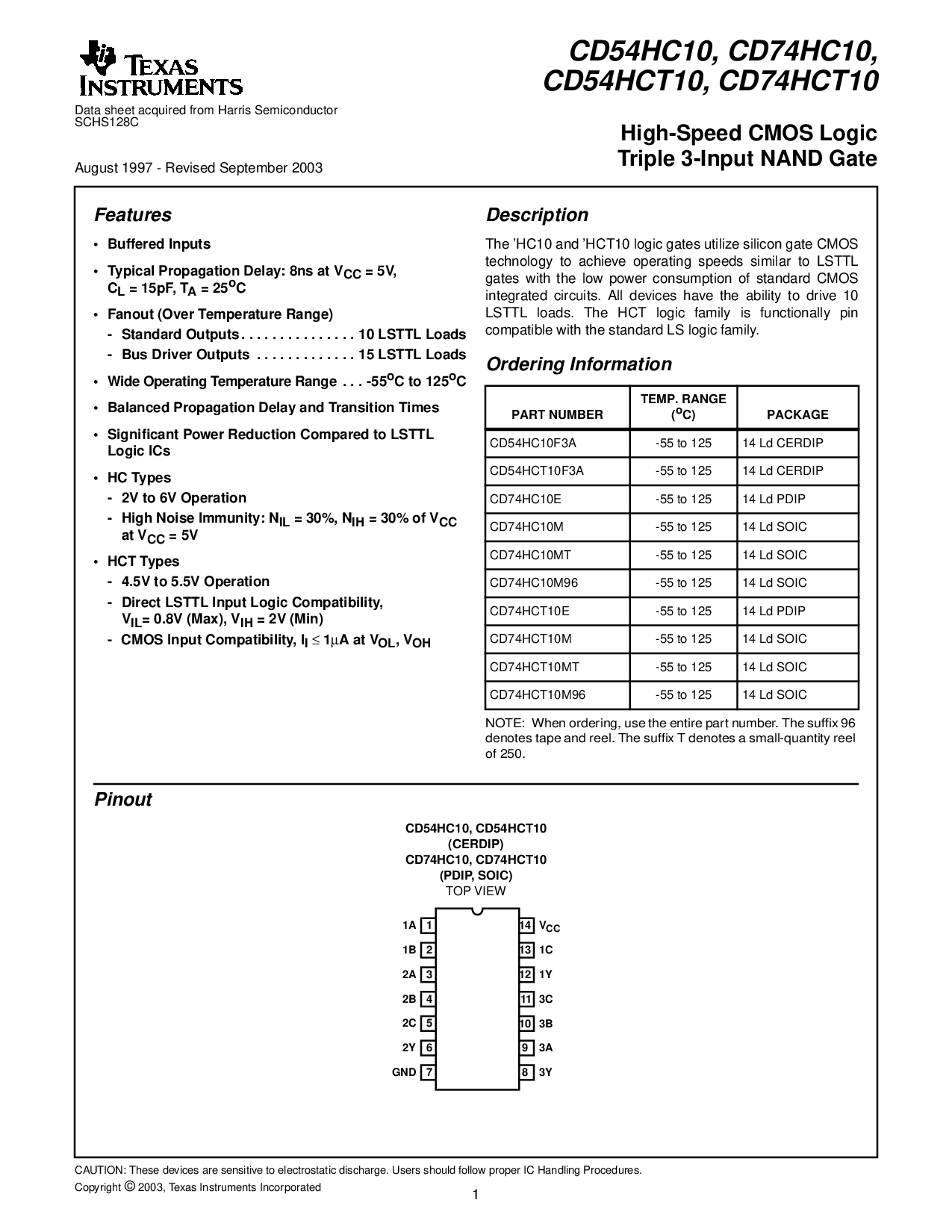

引脚

cd54hc10, cd54hct10

(cerdip)

cd74hc10, cd74hct10

(pdip, soic)

顶 视图

订货 信息

部分 号码

温度 范围

(

o

c) 包装

CD54HC10F3A -55 至 125 14 ld cerdip

CD54HCT10F3A -55 至 125 14 ld cerdip

CD74HC10E -55 至 125 14 ld pdip

CD74HC10M -55 至 125 14 ld soic

CD74HC10MT -55 至 125 14 ld soic

CD74HC10M96 -55 至 125 14 ld soic

CD74HCT10E -55 至 125 14 ld pdip

CD74HCT10M -55 至 125 14 ld soic

CD74HCT10MT -55 至 125 14 ld soic

CD74HCT10M96 -55 至 125 14 ld soic

便条: 当 订货, 使用 这 全部 部分 号码. 这 suffix 96

denotes 录音带 和 卷轴. 这 suffix T denotes 一个 小-quantity 卷轴

的 250.

1A

1B

2A

2B

2C

2Y

地

V

CC

1C

1Y

3C

3B

3A

3Y

1

2

3

4

5

6

7

14

13

12

11

10

9

8

8月 1997 - 修订 九月 2003

提醒: 这些 设备 是 敏感的 至 静电的 释放. 用户 应当 follow 恰当的 ic 处理 程序.

版权

©

2003, 德州 器械 组成公司的

cd54hc10, cd74hc10,

cd54hct10, cd74hct10

高-速 cmos 逻辑

triple 3-输入 与非 门

[ /标题

(cd74

hc10,

CD74

HCT10

)

/

sub-

ject

(高

速

CMOS

逻辑

Triple

3-输入

与非

门)

/autho

r ()

/关键-

words

(高

速

CMOS

逻辑

Triple

3-输入

与非

门,

高

速

CMOS

逻辑

Triple

3-输入

与非

门,

Harris

semi-