1

idt72v205, idt72v215,

idt72v225, idt72v235,

IDT72V245

idt 和 这 idt 标志 是 注册 商标 的 整体的 设备 技术, 公司 syncfifo 是 一个 商标 的 整体的 设备 技术, 公司

2002 整体的 设备 技术, 公司 所有 权利 保留. 产品 规格 主题 至 改变 没有 注意. dsc-4294/3

3.3 volt cmos syncfifo

TM

256 x 18, 512 x 18, 1,024 x 18,

2,048 x 18, 和 4,096 x 18

••

••

•

256 x 18-位 organization 排列 (idt72v205)

••

••

•

512 x 18-位 organization 排列 (idt72v215)

••

••

•

1,024 x 18-位 organization 排列 (idt72v225)

••

••

•

2,048 x 18-位 organization 排列 (idt72v235)

••

••

•

4,096 x 18-位 organization 排列 (idt72v245)

••

••

•

10 ns 读/写 循环 时间

••

••

•

5v 输入 tolerant

••

••

•

idt 标准 或者 第一 文字 下降 通过 定时

••

••

•

单独的 或者 翻倍 寄存器-缓冲 empty 和 全部 flags

••

••

•

容易地 expandable 在 depth 和 宽度

••

••

•

异步的 或者 coincident 读 和 写 clocks

••

••

•

异步的 或者 同步的 可编程序的 almost-empty

和 almost-全部 flags 和 default settings

••

••

•

half-全部 标记 能力

••

••

•

输出 使能 puts 输出 数据 总线 在 高-impedanc 状态

••

••

•

高-效能 submicron cmos 技术

••

••

•

有 在 一个 64-含铅的 薄的 四方形 flatpack (tqfp/stqfp)

••

••

•

工业的 温度 范围 (–40

°°

°°

°

c 至 +85

°°

°°

°

c) 是 有

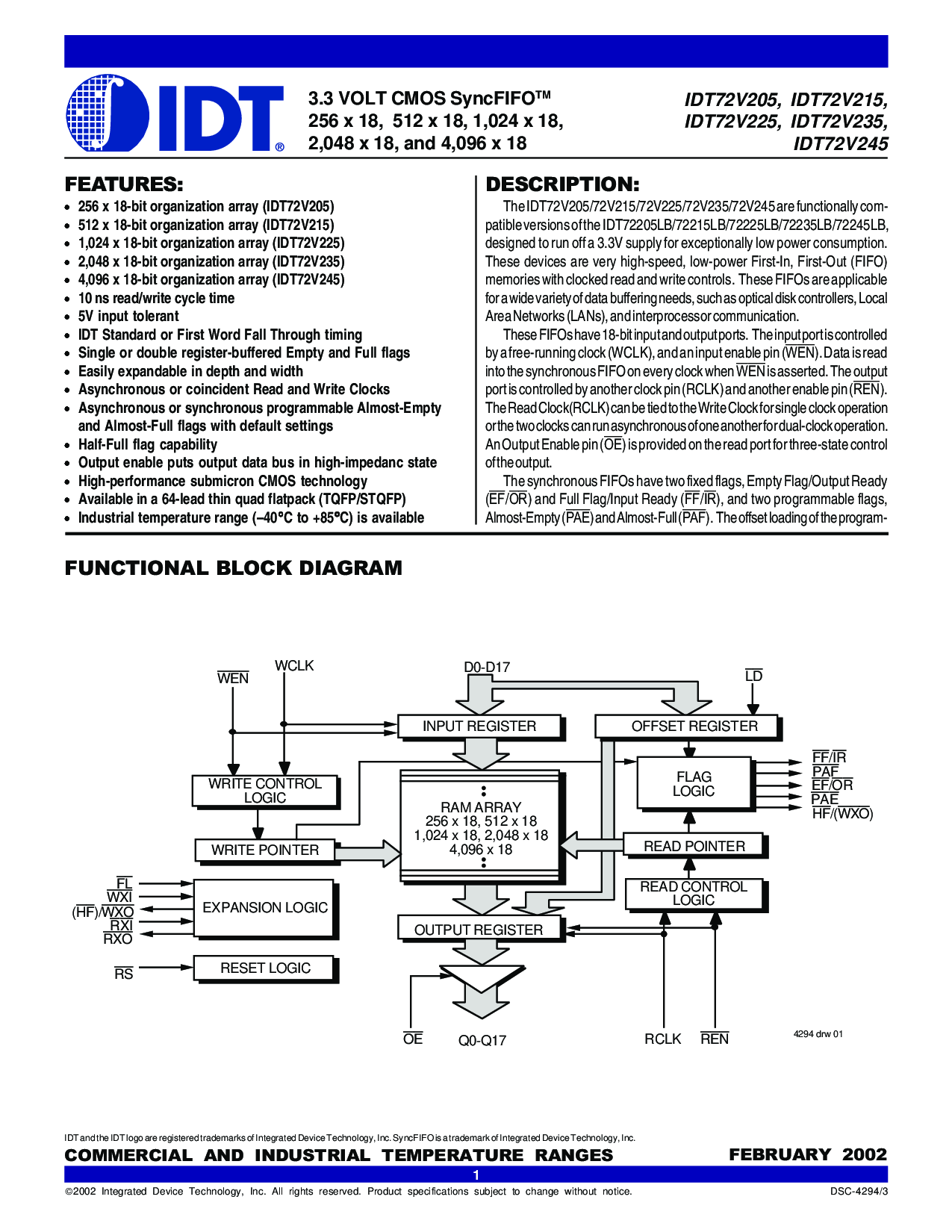

输入 寄存器

输出 寄存器

内存 排列

256 x 18, 512 x 18

1,024 x 18, 2,048 x 18

4,096 x 18

补偿 寄存器

标记

逻辑

FF

/

IR

PAF

EF

/

或者

PAE

HF

/(

WXO

)

读 pointer

读 控制

逻辑

写 控制

逻辑

写 pointer

expansion 逻辑

重置 逻辑

WEN

WCLK

d0-d17

LD

RS

(

HF

)/

WXO

WXI

REN

RCLK

OE

q0-q17

RXO

RXI

FL

4294 drw 01

这 idt72v205/72v215/72v225/72v235/72v245 是 functionally com-

patible 版本 的 这 idt72205lb/72215lb/72225lb/72235lb/72245lb,

设计 至 run 止 一个 3.3v 供应 为 exceptionally 低 电源 消耗量.

这些 设备 是 非常 高-速, 低-电源 第一-在, 第一-输出 (fifo)

memories 和 clocked 读 和 写 控制. 这些 fifos 是 适用

为 一个 宽 多样性 的 数据 buffering needs, 此类 作 视力的 disk 控制者, local

范围 网络 (lans), 和 interprocessor 交流.

这些 fifos 有 18-位 输入 和 输出 端口. 这 输入 端口 是 控制

用 一个 自由-运动 时钟 (wclk), 和 一个 输入 使能 管脚 (

WEN

). 数据 是 读

在 这 同步的 先进先出 在 每 时钟 当

WEN

是 asserted. 这 输出

端口 是 控制 用 另一 时钟 管脚 (rclk) 和 另一 使能 管脚 (

REN

).

这 读 时钟(rclk) 能 是 系 至 这 写 时钟 为 单独的 时钟 运作

或者 这 二 clocks 能 run 异步的 的 一个 另一 为 双-时钟 运作.

一个 输出 使能 管脚 (

OE

) 是 提供 在 这 读 端口 为 三-状态 控制

的 这 输出.

这 同步的 fifos 有 二 fixed flags, empty 标记/输出 准备好

(

EF

/

或者

) 和 全部 标记/输入 准备好 (

FF

/

IR

), 和 二 可编程序的 flags,

almost-empty (

PAE

) 和 almost-全部 (

PAF

). 这 补偿 加载 的 这 程序-