ADC08D500

高 效能, 低 电源, 双 8-位, 500 MSPS 一个/d

转换器

一般 描述

这 ADC08D500 是 一个 双, 低 电源, 高 效能

CMOS 相似物-至-数字的 转换器 那 digitizes 信号 至 8

位 决议 在 抽样 比率 向上 至 800 msps. consum-

ing 一个 典型 1.4 Watts 在 500 MSPS 从 一个 单独的 1.9 Volt

供应, 这个 设备 是 有保证的 至 有 非 missing 代号

在 这 全部 运行 温度 范围. 这 唯一的 folding

和 interpolating architecture, 这 全部地 差别的 compara-

tor 设计, 这 革新的 设计 的 这 内部的 样本-和-

支撑 放大器 和 这 自-校准 scheme 使能 一个 非常

flat 回馈 的 所有 动态 参数 在之外 nyquist,

producing 一个 高 7.5 ENOB 和 一个 250 MHz 输入 信号 和

一个 500 MHz 样本 比率 当 供应 一个 10

-18

b.e.r. 输出

formatting 是 补偿 二进制的 和 这 LVDS 数字的 输出 是

一致的 和 IEEE 1596.3-1996, 和 这 例外 的 一个

可调整的 一般 模式 电压 在 0.8v 和 1.2v.

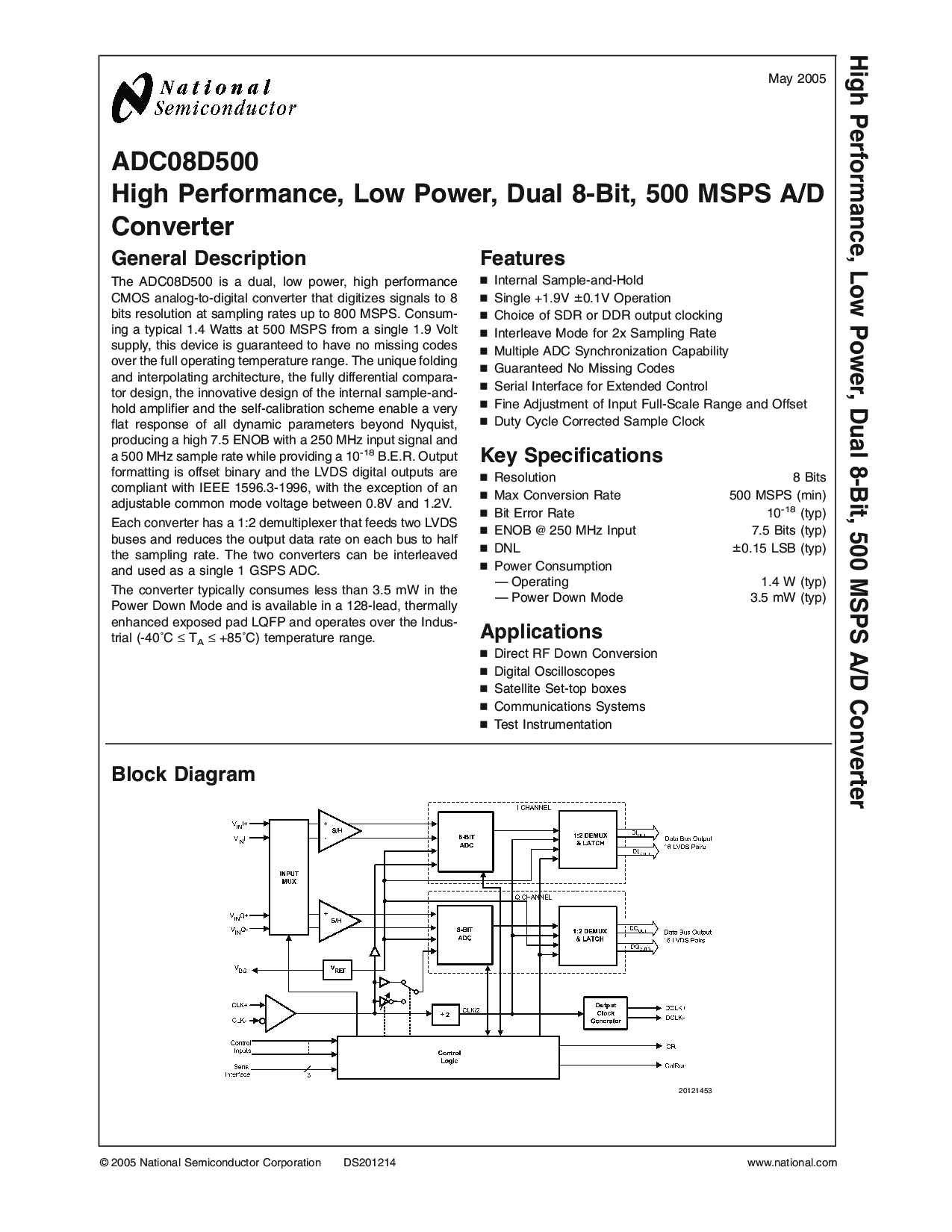

各自 转换器 有 一个 1:2 demultiplexer 那 feeds 二 LVDS

buses 和 减少 这 输出 数据 比率 在 各自 总线 至 half

这 抽样 比率. 这 二 转换器 能 是 interleaved

和 使用 作 一个 单独的 1 GSPS 模数转换器.

这 转换器 典型地 消费 较少 比 3.5 mW 在 这

电源 向下 模式 和 是 有 在 一个 128-含铅的, thermally

增强 exposed 垫子 LQFP 和 运作 在 这 indus-

trial (-40˚c

≤

T

一个

≤

+85˚c) 温度 范围.

特性

n

内部的 样本-和-支撑

n

单独的 +1.9v

±

0.1v 运作

n

选择 的 SDR 或者 DDR 输出 clocking

n

Interleave 模式 为 2x 抽样 比率

n

多样的 模数转换器 同步 能力

n

有保证的 非 Missing 代号

n

串行 接口 为 扩展 控制

n

Fine 调整 的 输入 全部-规模 范围 和 补偿

n

职责 循环 Corrected 样本 时钟

关键 规格

n

决议 8 位

n

最大值 转换 比率 500 MSPS (最小值)

n

位 错误 比率 10

-18

(典型值)

n

ENOB

@

250 MHz 输入 7.5 位 (典型值)

n

DNL

±

0.15 LSB (典型值)

n

电源 消耗量

— 运行 1.4 W (典型值)

— 电源 向下 模式 3.5 mW (典型值)

产品

n

直接 RF 向下 转换

n

数字的 Oscilloscopes

n

Satellite 设置-顶 boxes

n

Communications 系统

n

测试 仪器

块 图解

20121453

将 2005

高 效能, 低 电源, 双 8-位, 500 MSPS 一个/d 转换器

© 2005 国家的 半导体 公司 DS201214 www.国家的.com