rev. b

AD9767

–13–

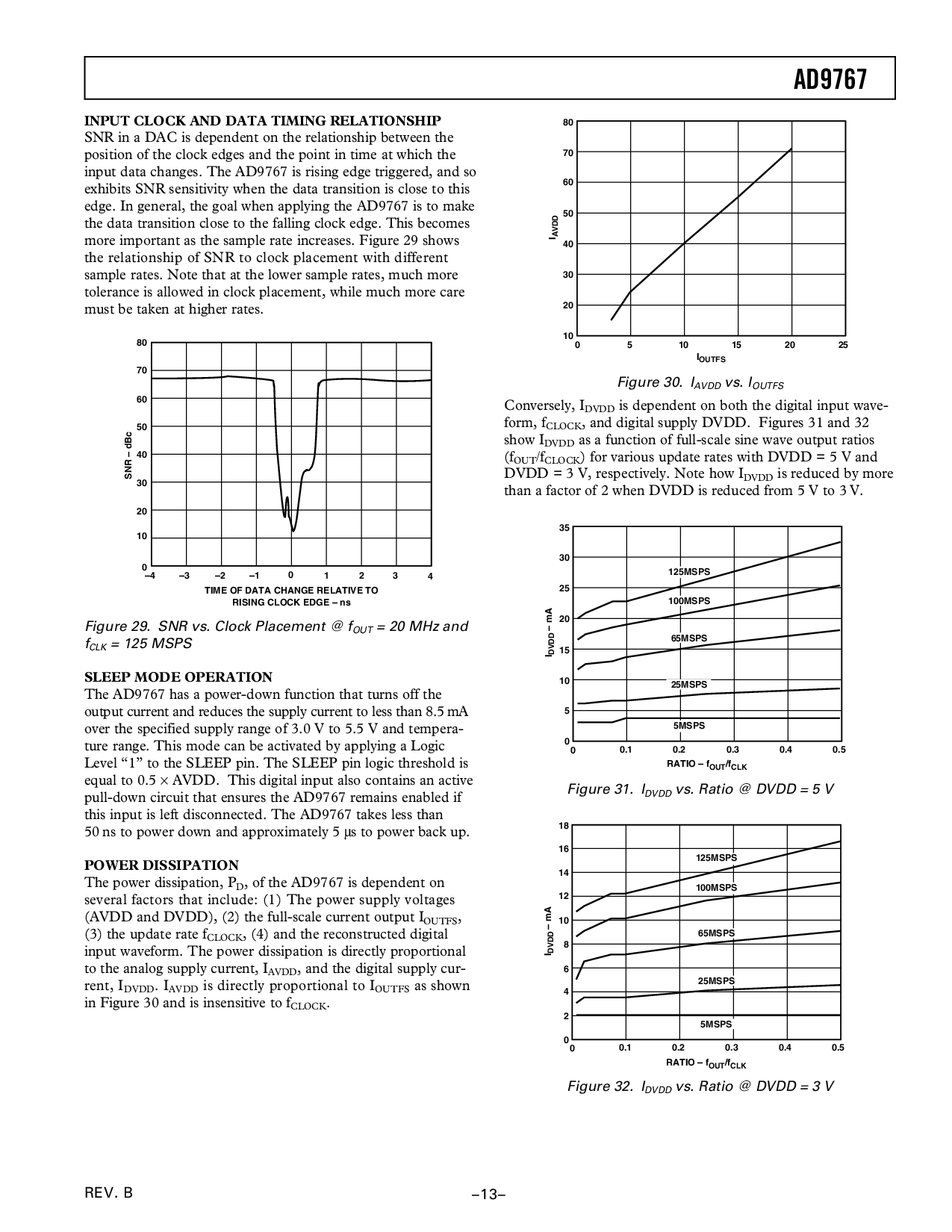

输入 时钟 和 数据 计时 关系

snr 入点 一个 dac 是 从属 开启 这 关系 之间 这

位置 的 这 时钟 边缘 和 这 点 入点 时间 在 哪个 这

输入 数据 变更. 这 ad9767 是 上升 边缘 已触发, 和 所以

展品 snr 灵敏度 当 这 数据 过渡 是 关闭 至 这个

边缘. 入点 概述, 这 目标 当 申请 这 ad9767 是 至 制造

这 数据 过渡 关闭 至 这 坠落 时钟 边缘. 这个 成为

更多 重要 作为 这 样品 费率 增加. 图 29 显示

这 关系 的 snr 至 时钟 放置位置 与 不同的

样品 费率. 备注 那 在 这 下部 样品 费率, 很多 更多

公差 是 允许 入点 时钟 放置位置, 同时 很多 更多 护理

必须 是 已拍摄 在 较高 费率.

时间 的 数据 变更 相对 至

上升 时钟 边缘

–

ns

SNR

–

dBc

0

–

4

–

2

0

23

–

3

–

1

4

1

10

20

30

40

50

60

70

80

图 29. snr vs. 时钟 放置位置 @ f

出点

= 20 mhz 和

f

clk

= 125 msps

睡眠 模式 操作

这 ad9767 有 一个 掉电 功能 那 圈数 关 这

输出 电流 和 减少 这 供应 电流 至 较少 比 8.5 ma

结束 这 指定 供应 范围 的 3.0 v 至 5.5 v 和 蛋彩画-

真实 范围. 这个 模式 可以 是 已激活 由 申请 一个 逻辑

水平 “1” 至 这 睡眠 管脚. 这 睡眠 管脚 逻辑 阈值 是

相等 至 0.5

×

avdd. 这个 数字 输入 也 包含 一个 活动

下拉 电路 那 确保 这 ad9767 遗迹 已启用 如果

这个 输入 是 左 已断开连接. 这 ad9767 需要 较少 比

50 ns 至 电源 向下 和 大约 5

µ

s 至 电源 背面 向上.

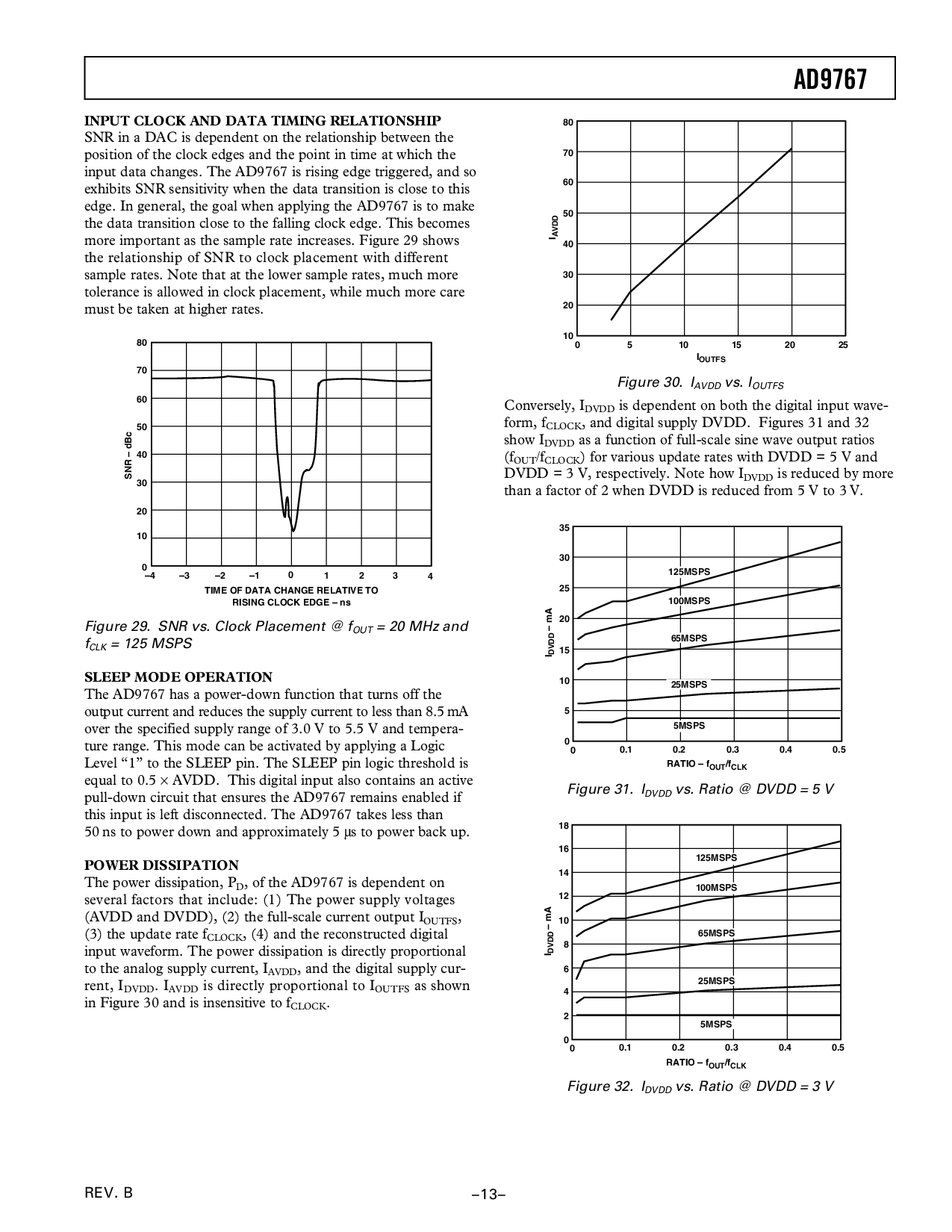

电源 耗散

这 电源 耗散, p

d

, 的 这 ad9767 是 从属 开启

几个 因素 那 包括: (1) 这 电源 供应 电压

(avdd 和 dvdd), (2) 这 满量程 电流 输出 我

OUTFS

,

(3) 这 更新 费率 f

时钟

, (4) 和 这 重建 数字

输入 波形. 这 电源 耗散 是 直接 比例

至 这 模拟 供应 电流, 我

AVDD

, 和 这 数字 供应cur-

租金, 我

DVDD

. 我

AVDD

是 直接 比例 至 我

OUTFS

作为 显示

入点 图 30 和 是 不敏感 至 f

时钟

.

我

OUTFS

0510

10

我

AVDD

20

30

40

50

60

70

80

15 20 25

图 30. 我

AVDD

vs. 我

OUTFS

相反, 我

DVDD

是 从属 开启 两者都有 这 数字 输入 波浪-

窗体, f

时钟

, 和 数字 供应 dvdd. 数字 31 和 32

显示 我

DVDD

作为 一个 功能 的 满量程 正弦 波浪 输出 比率

(f

出点

/f

时钟

) 用于 各种 更新 费率 与 dvdd = 5 v 和

dvdd = 3 v, 分别. 备注 如何 我

DVDD

是 减少 由 更多

比 一个 因素 的 2 当 dvdd 是 减少 从 5 v 至 3 v.

比率

–

f

出点

/f

clk

0

0.1

0

我

DVDD

–

ma

5

10

15

20

25

30

35

0.2 0.3 0.4 0.5

125MSPS

100MSPS

65MSPS

25MSPS

5MSPS

图 31. 我

DVDD

vs. 比率 @ dvdd = 5 v

比率

–

f

出点

/f

clk

0

0.1

0

我

DVDD

–

ma

2

4

6

8

10

12

14

0.2 0.3 0.4 0.5

16

18

125MSPS

100MSPS

65MSPS

25MSPS

5MSPS

图 32. 我

DVDD

vs. 比率 @ dvdd = 3 v