AD7002

–7–rev. b

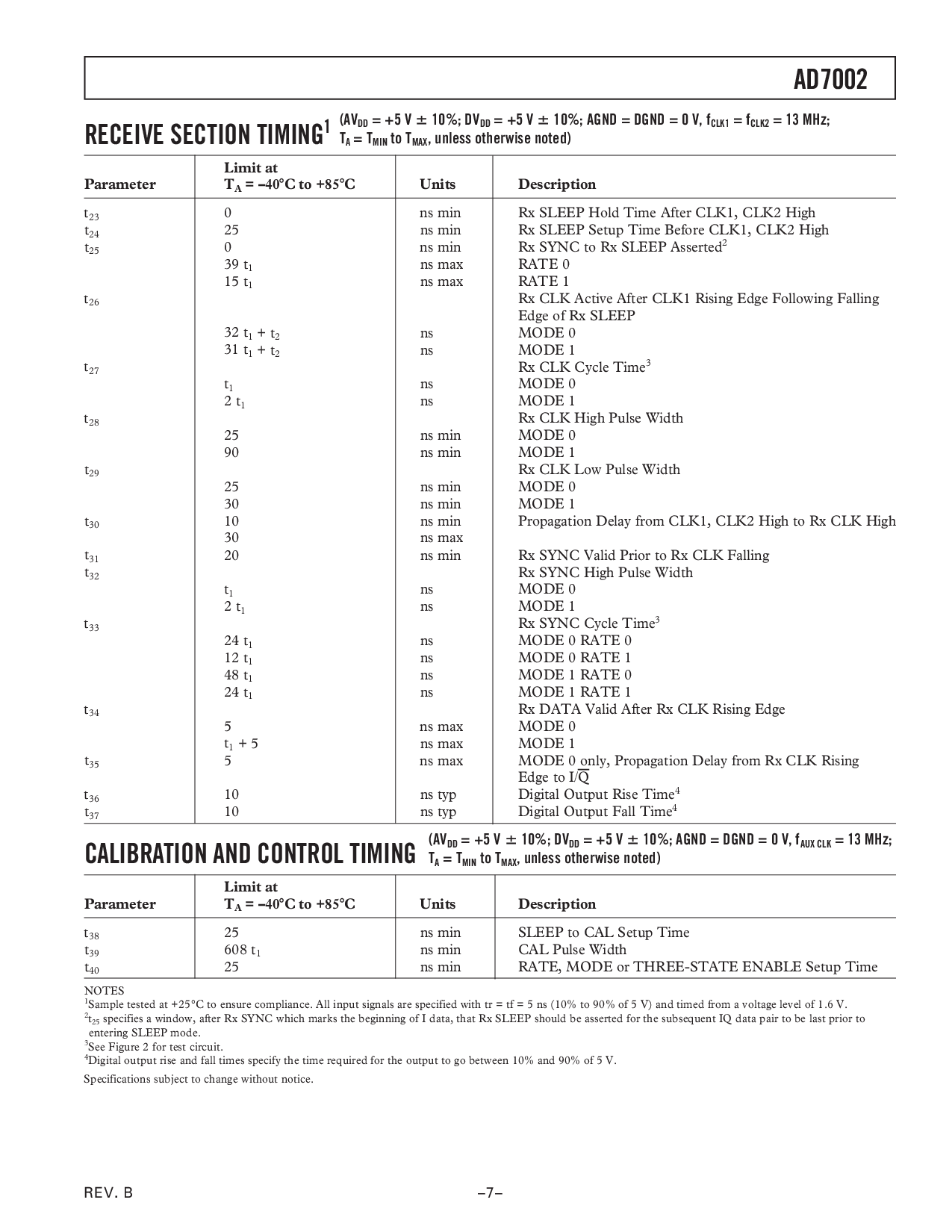

receive 部分 定时

1

限制 在

参数 T

一个

= –40

c 至 +85

C 单位 描述

t

23

0 ns 最小值 rx 睡眠 支撑 时间 之后 clk1, clk2 高

t

24

25 ns 最小值 rx 睡眠 建制 时间 在之前 clk1, clk2 高

t

25

0 ns 最小值 rx 同步 至 rx 睡眠 asserted

2

39 t

1

ns 最大值 比率 0

15 t

1

ns 最大值 比率 1

t

26

rx clk 起作用的 之后 clk1 rising 边缘 下列的 下落

边缘 的 rx 睡眠

32 t

1

+ t

2

ns 模式 0

31 t

1

+ t

2

ns 模式 1

t

27

rx clk 循环 时间

3

t

1

ns 模式 0

2 t

1

ns 模式 1

t

28

rx clk 高 脉冲波 宽度

25 ns 最小值 模式 0

90 ns 最小值 模式 1

t

29

rx clk 低 脉冲波 宽度

25 ns 最小值 模式 0

30 ns 最小值 模式 1

t

30

10 ns 最小值 传播 延迟 从 clk1, clk2 高 至 rx clk 高

30 ns 最大值

t

31

20 ns 最小值 rx 同步 有效的 较早的 至 rx clk 下落

t

32

rx 同步 高 脉冲波 宽度

t

1

ns 模式 0

2 t

1

ns 模式 1

t

33

rx 同步 循环 时间

3

24 t

1

ns 模式 0 比率 0

12 t

1

ns 模式 0 比率 1

48 t

1

ns 模式 1 比率 0

24 t

1

ns 模式 1 比率 1

t

34

rx 数据 有效的 之后 rx clk rising 边缘

5 ns 最大值 模式 0

t

1

+ 5 ns 最大值 模式 1

t

35

5 ns 最大值 模式 0 仅有的, 传播 延迟 从 rx clk rising

边缘 至 i/

Q

t

36

10 ns 典型值 数字的 输出 上升 时间

4

t

37

10 ns 典型值 数字的 输出 下降 时间

4

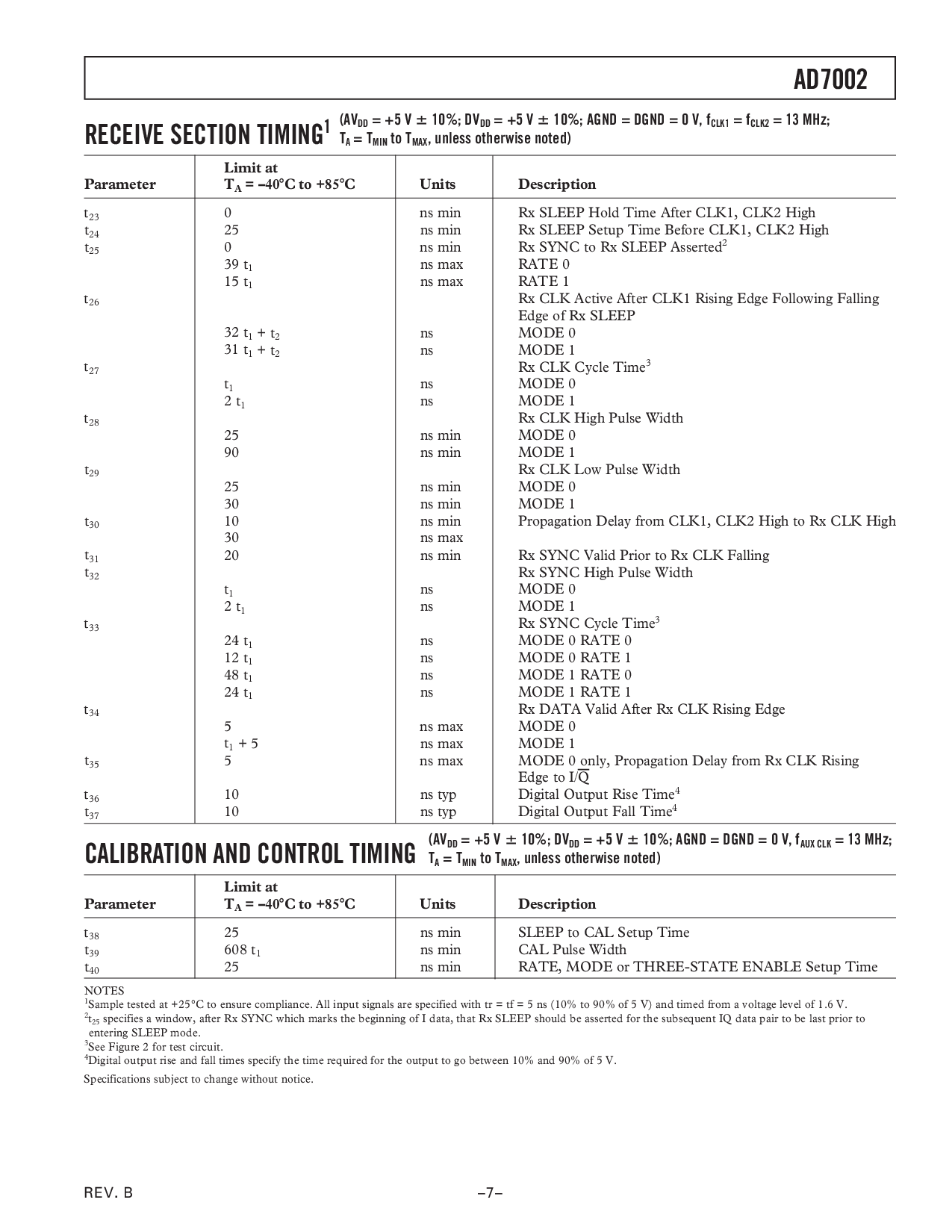

校准 和 控制 定时

限制 在

参数 T

一个

= –40

c 至 +85

C 单位 描述

t

38

25 ns 最小值 睡眠 至 cal 建制 时间

t

39

608 t

1

ns 最小值 cal 脉冲波 宽度

t

40

25 ns 最小值 比率, 模式 或者 三-状态 使能 建制 时间

注释

1

样本 测试 在 +25

°

c 至 确保 遵从. 所有 输入 信号 是 指定 和 tr = tf = 5 ns (10% 至 90% 的 5 v) 和 安排时间 从 一个 电压 水平的 的 1.6 v.

2

t

25

specifies 一个 window, 之后 rx 同步 这个 marks 这 beginning 的 i 数据, 那 rx 睡眠 应当 是 asserted 为 这 subsequent iq 数据 一双 至 是 last 较早的 至

进去 睡眠 模式.

3

看 图示 2 为 测试 电路.

4

数字的 输出 上升 和 下降 时间 具体说明 这 时间 必需的 为 这 输出 至 go 在 10% 和 90% 的 5 v.

规格 主题 至 改变 没有 注意.

(av

DD

= +5 v

10%; dv

DD

= +5 v

10%; agnd = dgnd = 0 v, f

CLK1

= f

CLK2

= 13 mhz;

T

一个

= t

最小值

至 t

最大值

, 除非 否则 指出)

(av

DD

= +5 v

10%; dv

DD

= +5 v

10%; agnd = dgnd = 0 v, f

aux clk

= 13 mhz;

T

一个

= t

最小值

至 t

最大值

, 除非 否则 指出)