4 sam0402-050301 ess 技术, 公司

es2898/es2828 产品 brief

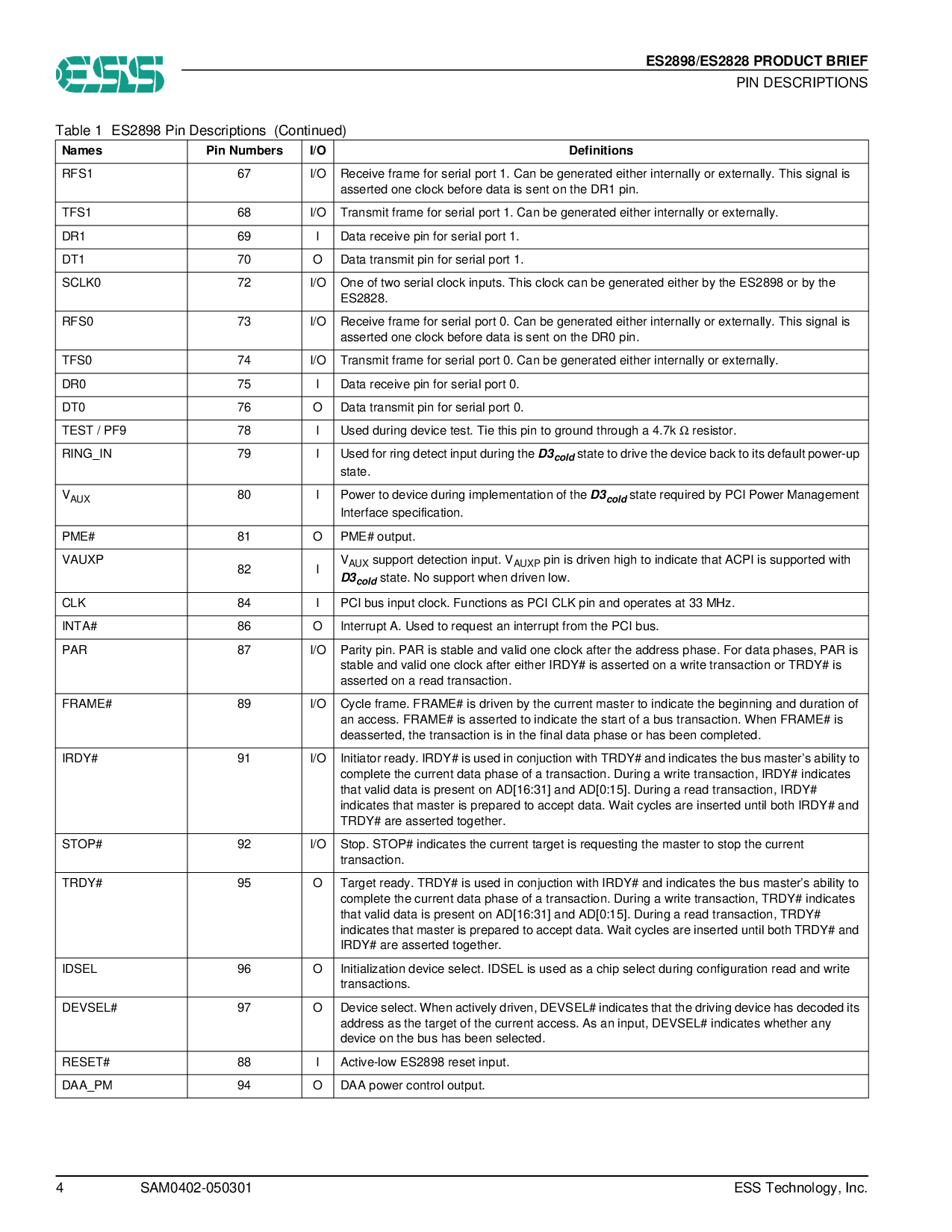

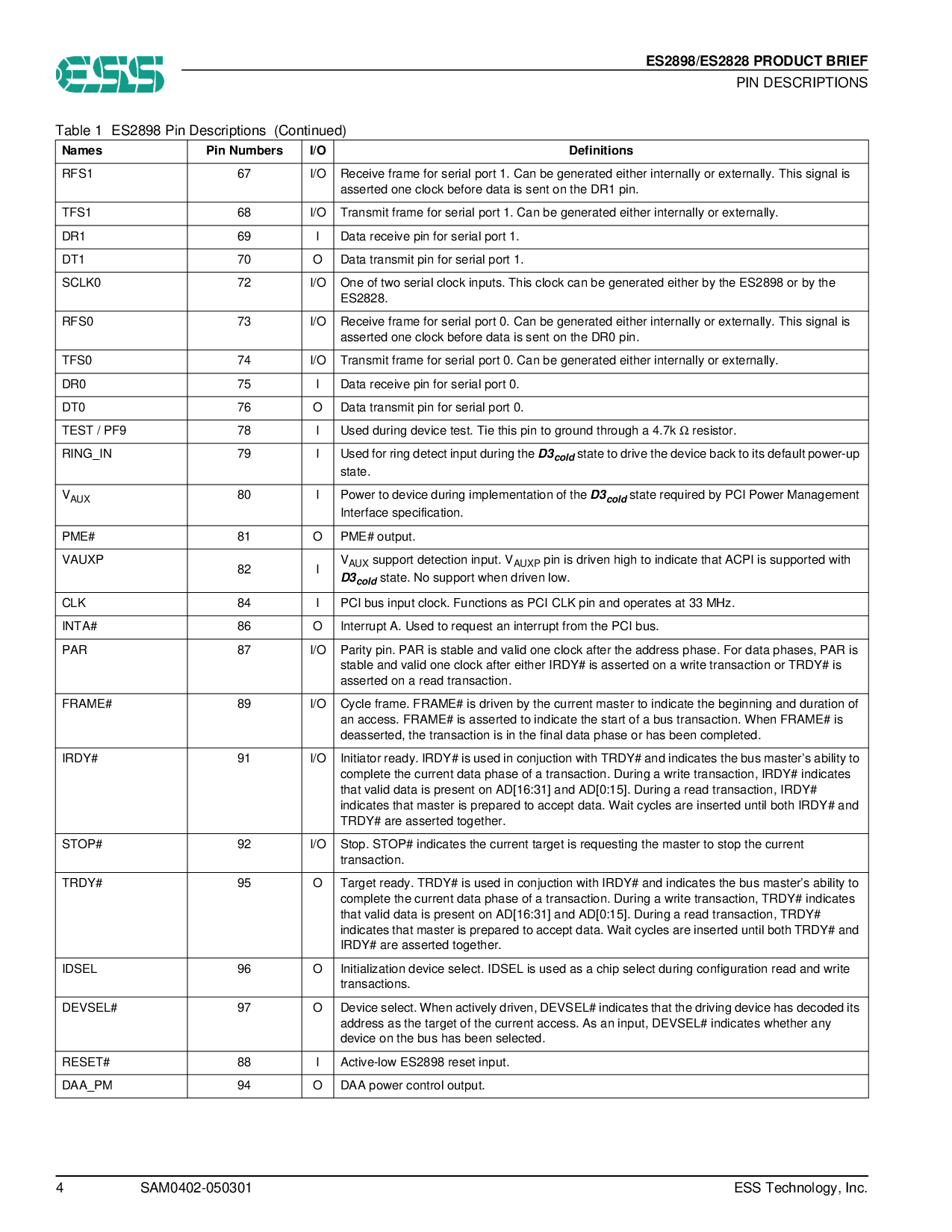

管脚 描述

RFS1 67 i/o receive 框架 为 串行 端口 1. 能 是 发生 也 内部 或者 externally. 这个 信号 是

asserted 一个 时钟 在之前 数据 是 sent 在 这 dr1 管脚.

TFS1 68 i/o transmit 框架 为 串行 端口 1. 能 是 发生 也 内部 或者 externally.

DR1 69 I 数据 receive 管脚 为 串行 端口 1.

DT1 70 O 数据 transmit 管脚 为 串行 端口 1.

SCLK0 72 i/o 一个 的 二 串行 时钟 输入. 这个 时钟 能 是 发生 也 用 这 es2898 或者 用 这

es2828.

RFS0 73 i/o receive 框架 为 串行 端口 0. 能 是 发生 也 内部 或者 externally. 这个 信号 是

asserted 一个 时钟 在之前 数据 是 sent 在 这 dr0 管脚.

TFS0 74 i/o transmit 框架 为 串行 端口 0. 能 是 发生 也 内部 或者 externally.

DR0 75 I 数据 receive 管脚 为 串行 端口 0.

DT0 76 O 数据 transmit 管脚 为 串行 端口 0.

测试 / pf9 78 I 使用 在 设备 测试. 系 这个 管脚 至 地面 通过 一个 4.7k

Ω

电阻.

环绕_在 79 I 使用 为 环绕 发现 输入 在 这

D3

cold

状态 至 驱动 这 设备 后面的 至 它的 default 电源-向上

状态.

V

AUX

80 I 电源 至 设备 在 implementation 的 这

D3

cold

状态 必需的 用 pci 电源 管理

接口 规格.

PME# 81 O pme# 输出.

VAUXP

82 I

V

AUX

支持 发现 输入. v

AUXP

管脚 是 驱动 高 至 表明 那 acpi 是 supported 和

D3

cold

状态. 非 支持 当 驱动 低.

CLK 84 I pci 总线 输入 时钟. 功能 作 pci clk 管脚 和 运作 在 33 mhz.

INTA# 86 O 中断 一个. 使用 至 要求 一个 中断 从 这 pci 总线.

PAR 87 i/o parity 管脚. par 是 稳固的 和 有效的 一个 时钟 之后 这 地址 阶段. 为 数据 阶段, par 是

稳固的 和 有效的 一个 时钟 之后 也 irdy# 是 asserted 在 一个 写 transaction 或者 trdy# 是

asserted 在 一个 读 transaction.

FRAME# 89 i/o 循环 框架. frame# 是 驱动 用 这 电流 主控 至 表明 这 beginning 和 持续时间 的

一个 进入. frame# 是 asserted 至 表明 这 开始 的 一个 总线 transaction. 当 frame# 是

deasserted, 这 transaction 是 在 这 最终 数据 阶段 或者 有 被 完成.

IRDY# 91 i/o initiator 准备好. irdy# 是 使用 在 conjuction 和 trdy# 和 indicates 这 总线 主控’s 能力 至

完全 这 电流 数据 阶段 的 一个 transaction. 在 一个 写 transaction, irdy# indicates

那 有效的 数据 是 呈现 在 ad[16:31] 和 ad[0:15]. 在 一个 读 transaction, irdy#

indicates 那 主控 是 准备好 至 接受 数据. wait 循环 是 inserted 直到 两个都 irdy# 和

trdy# 是 asserted 一起.

STOP# 92 i/o 停止. stop# indicates 这 电流 目标 是 requesting 这 主控 至 停止 这 电流

transaction.

TRDY# 95 O 目标 准备好. trdy# 是 使用 在 conjuction 和 irdy# 和 indicates 这 总线 主控’s 能力 至

完全 这 电流 数据 阶段 的 一个 transaction. 在 一个 写 transaction, trdy# indicates

那 有效的 数据 是 呈现 在 ad[16:31] 和 ad[0:15]. 在 一个 读 transaction, trdy#

indicates 那 主控 是 准备好 至 接受 数据. wait 循环 是 inserted 直到 两个都 trdy# 和

irdy# 是 asserted 一起.

IDSEL 96 O initialization 设备 选择. idsel 是 使用 作 一个 碎片 选择 在 配置 读 和 写

transactions.

DEVSEL# 97 O 设备 选择. 当 actively 驱动, devsel# indicates 那 这 驱动 设备 有 解码 它的

地址 作 这 目标 的 这 电流 进入. 作 一个 输入, devsel# indicates whether 任何

设备 在 这 总线 有 被 选择.

RESET# 88 I 起作用的-低 es2898 重置 输入.

daa_pm 94 O daa 电源 控制 输出.

表格 1 es2898 管脚 描述(持续)

Names 管脚 号码 i/o 定义