6

128mb, 64mb, 32mb q-flash 记忆 micron 技术, inc., reserves 这 正确的 至 改变 产品 或者 规格 没有 注意.

mt28f640j3_7.p65 – rev. 6, pub. 8/02 ©2002, micron 技术, 公司

128mb, 64mb, 32mb

q-flash 记忆

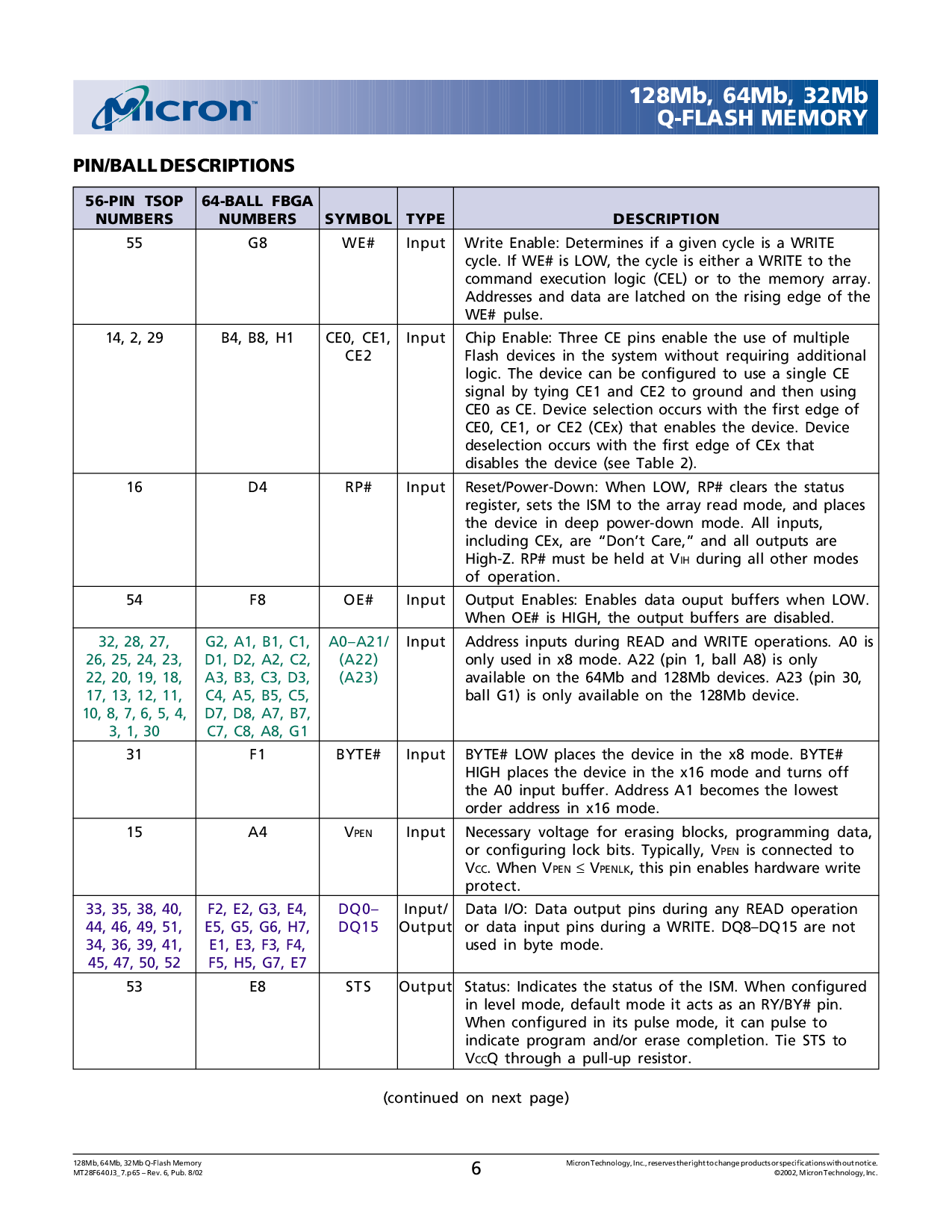

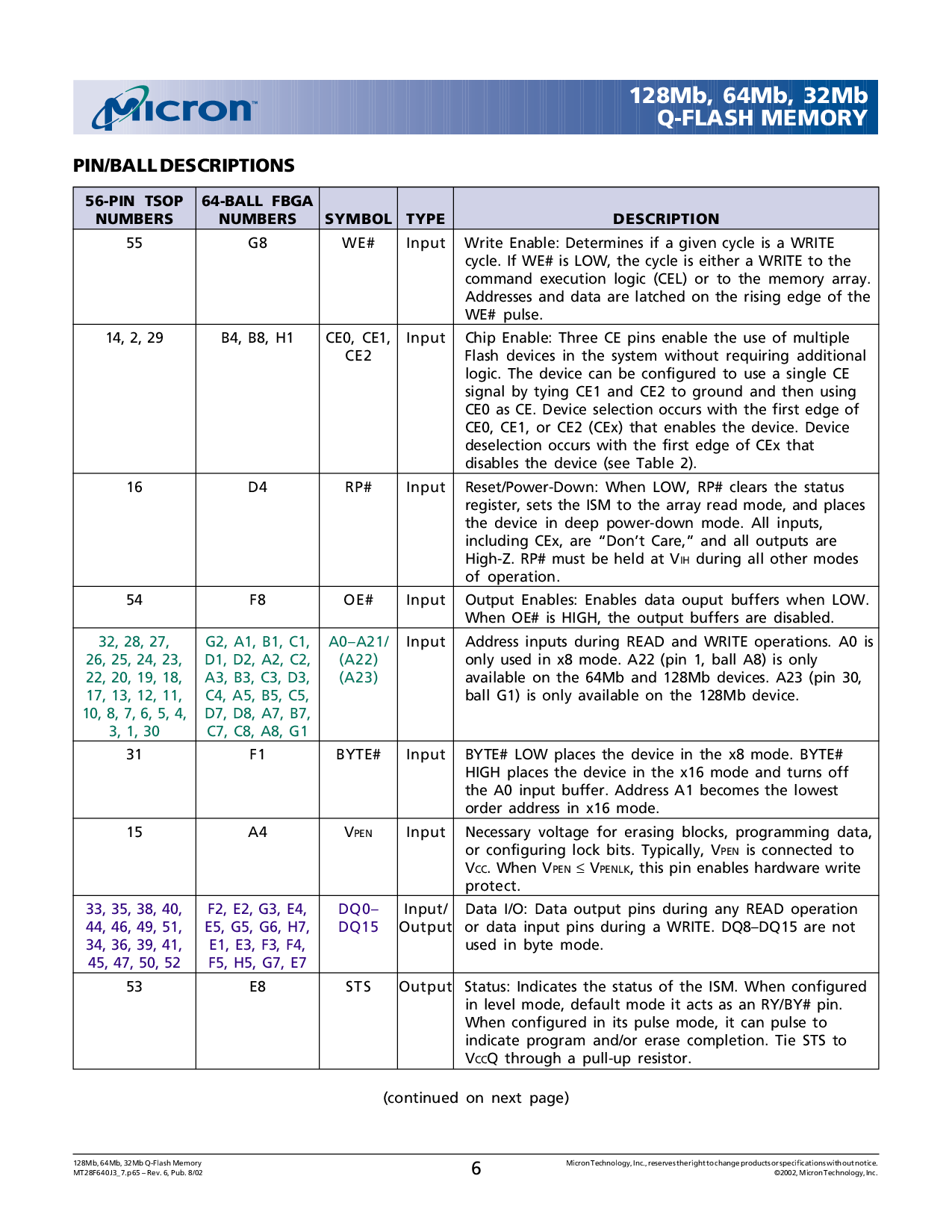

管脚/球 描述

56-管脚 tsop 64-球 fbga

号码 号码 标识 类型 描述

55 G8 WE# 输入 Write 使能: 确定 如果 一个 给 循环 是 一个 写

循环. 如果 we# 是 低, 这 循环 是 也 一个 写 至 这

command 执行 逻辑 (cel) 或者 至 这 记忆 排列.

地址 和 数据 是 latched 在 这 rising 边缘 的 这

we# 脉冲波.

14, 2, 29 b4,b8,H1 ce0, ce1, 输入 碎片 使能: 三 ce 管脚 使能 这 使用 的 多样的

CE2 flash 设备 在 这 系统 没有 需要 额外的

逻辑. 这 设备 能 是 配置 至 使用 一个 单独的 ce

信号 用 tying ce1 和 ce2 至 地面 和 然后 使用

ce0 作 ce. 设备 选择 occurs 和 这 第一 边缘 的

ce0, ce1, 或者 ce2 (cex) 那 使能 这 设备. 设备

deselection occurs 和 这 第一 边缘 的 cex 那

使不能运转 这 设备 (看 表格 2).

16 D4 RP# 输入 重置/电源-向下: 当 低, rp# clears 这 状态

寄存器, sets 这 ism 至 这 排列 读 模式, 和 places

这 设备 在 深的 电源-向下 模式. 所有 输入,

包含 cex, 是 “don’t 小心,” 和 所有 输出 是

高-z. rp# 必须 是 使保持 在 v

IH

在 所有 其它 模式

的 运作.

54 F8 OE# 输入 输出 使能: 使能 数据 输出 缓存区 当 低.

当 oe# 是 高, 这 输出 缓存区 是 无能.

32, 28, 27, g2, a1, b1, c1, a0–a21/ 输入 地址 输入 在 读 和 写 行动. a0 是

26, 25, 24, 23, d1, d2, a2, c2, (a22) 仅有的 使用 在 x8 模式. a22 (管脚 1, 球 a8) 是 仅有的

22, 20, 19, 18, a3, b3, c3, d3, (a23) 有 在 这 64mb 和 128mb 设备. a23 (管脚 30,

17, 13, 12, 11, c4, a5,b5, c5, 球 g1) 是 仅有的 有 在 这 128mb 设备.

10, 8, 7, 6, 5, 4, d7,d8,a7,b7,

3, 1, 30 c7, c8, a8, g1

31 F1 BYTE# 输入 byte# 低 places 这 设备 在 这 x8 模式. byte#

高 places 这 设备 在 这 x16 模式 和 转变 止

这 a0 输入 缓存区. 地址 a1 变为 这 最低

顺序 地址 在 x16 模式.

15 A4 V

PEN

输入 需要 电压 为 erasing blocks, 程序编制 数据,

或者 configuring 锁 位. 典型地, v

PEN

是 连接 至

V

CC

. 当 v

PEN

≤

V

PENLK

, 这个 管脚 使能 硬件 写

保护.

33, 35, 38, 40, f2, e2, g3, e4, DQ0– 输入/ 数据 i/o: 数据 输出 管脚 在 任何 读 运作

44, 46, 49, 51, e5, g5, g6, h7, DQ15 输出 或者数据 输入 管脚 在 一个 写. dq8–dq15 是 不

34, 36, 39, 41, e1, e3, f3, f4, 使用 在 字节 模式.

45, 47, 50, 52 f5, h5, g7, e7

53 E8 STS 输出 状态: indicates 这 状态 的 这 ism.当 配置

在 水平的 模式, default 模式 它 acts 作 一个 ry/by# 管脚.

当 配置 在 它的 脉冲波 模式, 它 能 脉冲波 至

表明 程序 和/或者 擦掉 completion. 系 sts 至

V

CC

q 通过 一个 拉-向上 电阻.

(持续 在 next 页)