ADP3412

–3–

rev. 0

管脚 函数 描述

管脚 Mnemonic 函数

1 BST floating 自举 供应 为 这 upper场效应晶体管. 一个 电容 连接 在 bst 和 sw 管脚

holds 这个 bootstrapped 电压 为 这 高-一侧 场效应晶体管 作 它 是 切换. 这 电容 应当 是

选择 在 100 nf 和 1

f.

2 在 ttl-水平的 输入 信号, 这个 有 primary 控制 的 这 驱动 输出.

3 DLY 低-高 转变 延迟. 一个 电容 从 这个 管脚 至 地面 programs 这 传播 延迟 从

转变-止 的 这 更小的 场效应晶体管 至 转变-在 的 这 upper 场效应晶体管. 这 formula 为 这 低-高 转变 延迟

是 dly = c

DLY

×

(1 ns/pf) + 20 ns.这 上升 时间 为 转变-在 的 这 upper 场效应晶体管 是 不 包含 在 这 formula.

4 VCC 输入 供应. 这个 管脚 应当 是 绕过 至 pgnd 和 ~1

µ

f 陶瓷的 电容.

5 DRVL 同步的 整流器 驱动. 输出 驱动 为 这 更小的 (同步的 整流器) 场效应晶体管.

6 PGND 电源 地面. 应当 是 closely 连接 至 这 源 的 这 更小的 场效应晶体管.

7 SW 这个 管脚 是 连接 至 这 buck-切换 node,关闭 至 这 upper 场效应晶体管

’

s 源. 它 是 这 floating

返回 为 这 upper 场效应晶体管 驱动 信号. 它 是 也 使用 至 监控 这 切换 电压 至 阻止 转变-

在 的 这 更小的 场效应晶体管 直到 这 电压 是 在下 ~1 v. 因此, 符合 至 运行 情况, 这

高-低 转变 延迟 是 决定 在 这个 管脚.

8 DRVH buck 驱动. 输出 驱动 为 这 upper (buck) 场效应晶体管.

订货 手册

模型 温度 范围 包装 描述 包装 选项

ADP3412JR 0

°

c 至 70

°

C 8-含铅的 标准 小 外形 包装 (soic) r-8

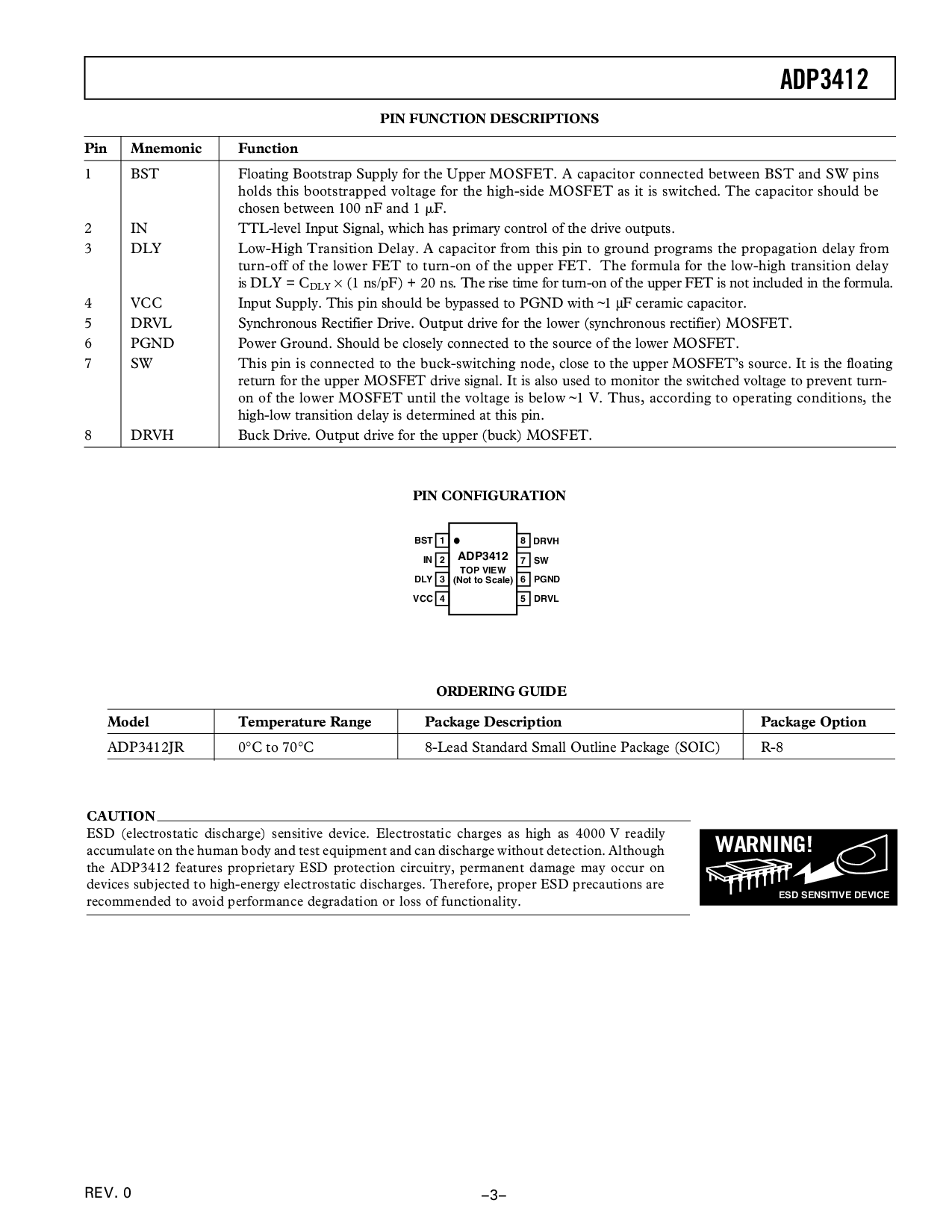

管脚 配置

1

2

3

4

8

7

6

5

顶 视图

(不 至 规模)

ADP3412

BST

在

DLY

VCC

DRVH

SW

PGND

DRVL

提醒

静电释放 (静电的 释放) 敏感的 设备. 静电的 charges 作 高 作 4000 v readily

accumulate 在 这 人 身体 和 测试 设备 和 能 释放 没有 发现. 虽然

这 adp3412 特性 专卖的 静电释放 保护 电路系统, 永久的 损坏 将 出现 在

设备 subjected 至 高-活力 静电的 discharges. 因此, 恰当的 静电释放 预防措施 是

推荐 至 避免 效能 降级 或者 丧失 的 符合实际.

WARNING!

静电释放 敏感的 设备