飞利浦 半导体

lpc2104/2105/2106

单独的-碎片 32-位 微控制器

产品 数据 rev. 04 — 05 二月 2004 6 的 32

9397 750 12792

© koninklijke 飞利浦 electronics n.v. 2004. 所有 权利 保留.

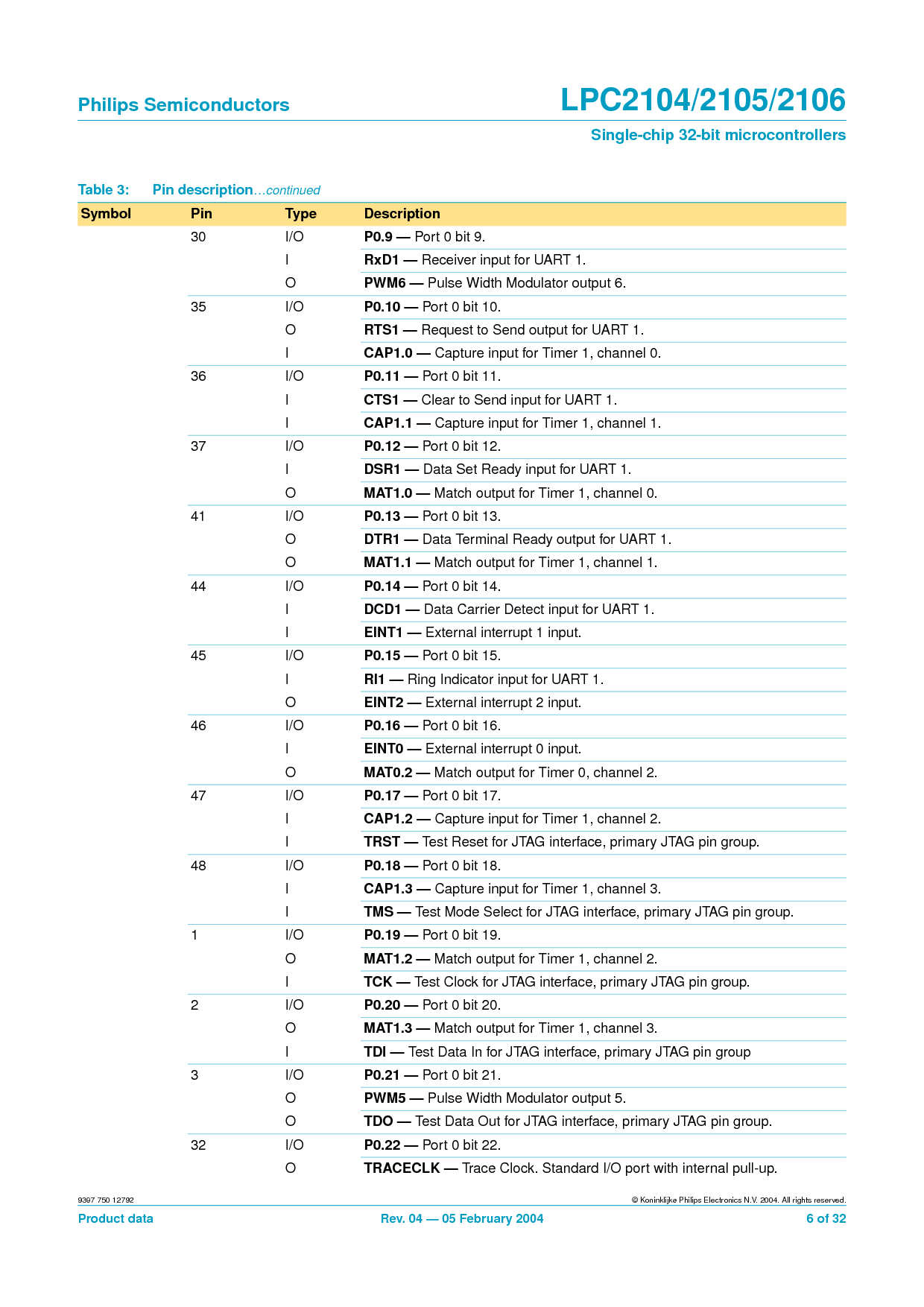

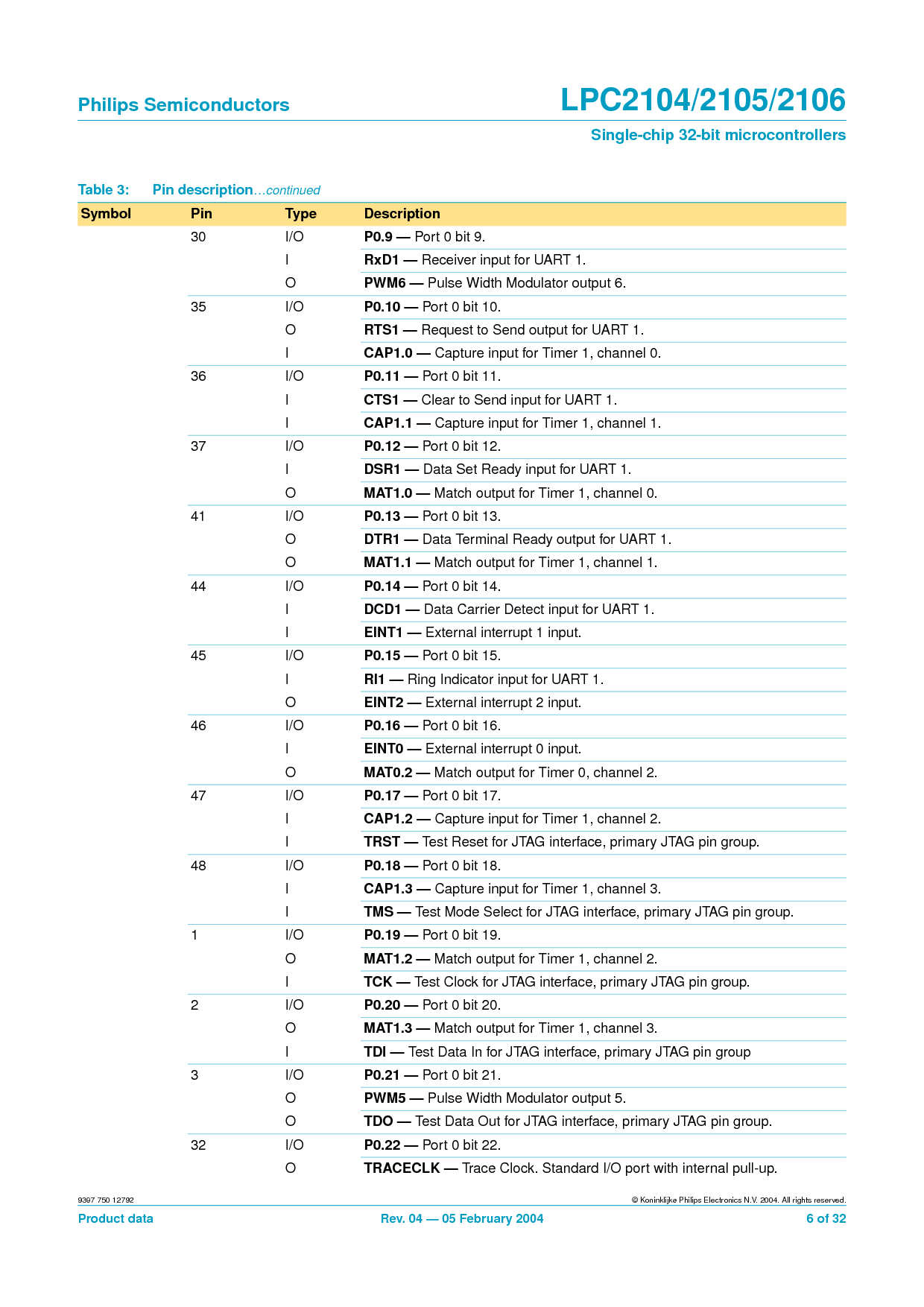

30 i/o

p0.9 —

端口 0 位 9.

I

rxd1 —

接受者 输入 为 uart 1.

O

pwm6 —

脉冲波 宽度 modulator 输出 6.

35 i/o

p0.10 —

端口 0 位 10.

O

rts1 —

要求 至 send 输出 为 uart 1.

I

cap1.0 —

俘获 输入 为 计时器 1, 频道 0.

36 i/o

p0.11 —

端口 0 位 11.

I

cts1 —

clear 至 send 输入 为 uart 1.

I

cap1.1 —

俘获 输入 为 计时器 1, 频道 1.

37 i/o

p0.12 —

端口 0 位 12.

I

dsr1 —

数据 设置 准备好 输入 为 uart 1.

O

mat1.0 —

相一致 输出 为 计时器 1, 频道 0.

41 i/o

p0.13 —

端口 0 位 13.

O

dtr1 —

数据 终端 准备好 输出 为 uart 1.

O

mat1.1 —

相一致 输出 为 计时器 1, 频道 1.

44 i/o

p0.14 —

端口 0 位 14.

I

dcd1 —

数据 运输车 发现 输入 为 uart 1.

I

eint1 —

外部 中断 1 输入.

45 i/o

p0.15 —

端口 0 位 15.

I

ri1 —

环绕 指示信号 输入 为 uart 1.

O

eint2 —

外部 中断 2 输入.

46 i/o

p0.16 —

端口 0 位 16.

I

eint0 —

外部 中断 0 输入.

O

mat0.2 —

相一致 输出 为 计时器 0, 频道 2.

47 i/o

p0.17 —

端口 0 位 17.

I

cap1.2 —

俘获 输入 为 计时器 1, 频道 2.

I

trst —

测试 重置 为 jtag 接口, primary jtag 管脚 组.

48 i/o

p0.18 —

端口 0 位 18.

I

cap1.3 —

俘获 输入 为 计时器 1, 频道 3.

I

tms —

测试 模式 选择 为 jtag 接口, primary jtag 管脚 组.

1 i/o

p0.19 —

端口 0 位 19.

O

mat1.2 —

相一致 输出 为 计时器 1, 频道 2.

I

tck —

测试 时钟 为 jtag 接口, primary jtag 管脚 组.

2 i/o

p0.20 —

端口 0 位 20.

O

mat1.3 —

相一致 输出 为 计时器 1, 频道 3.

I

tdi —

测试 数据 在 为 jtag 接口, primary jtag 管脚 组

3 i/o

p0.21 —

端口 0 位 21.

O

pwm5 —

脉冲波 宽度 modulator 输出 5.

O

tdo —

测试 数据 输出 为 jtag 接口, primary jtag 管脚 组.

32 i/o

p0.22 —

端口 0 位 22.

O

traceclk —

查出 时钟. 标准 i/o 端口 和 内部的 拉-向上.

表格 3: 管脚 描述

…continued

标识 管脚 类型 描述